Fターム[5J106AA05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412) | デジタルPLL (213)

Fターム[5J106AA05]に分類される特許

41 - 60 / 213

位相同期回路、CDR回路及び受信回路

【課題】基準クロックの周波数を低くして消費電力を抑制することのできる位相同期回路を提供する。

【解決手段】第1の位相比較器と第2の位相比較器とに、それぞれ帰還クロックの少なくとも1周期分異なる位相差をつけた分周クロックを入力して基準クロックとの位相比較を行い、受信信号と帰還クロックとの位相比較の結果で第1と第2の位相比較器の出力の重みづけを行い、重みづけされた出力により帰還クロックの位相調節を行う。

(もっと読む)

デジタル位相同期ループ回路

【課題】TDC(Time−to−DigitalConverter)の回路規模を拡張することなく、デスキュー用途に用いることが可能であるADPLLの構成の提供。

【解決手段】DCO19と、FREFを分周するMDIV11と、DCOの出力FOを分周するPDIV20と、PDIVの出力FOUTを分周するNDIV12と、MDIVの出力信号FRとDCOの出力FOの位相差を測定するTDC13と、NDIVの出力FDとFOの位相差を測定するTDC14と、FRでFOをサンプルするFF15と、FRとFDのうち位相が先行するパルスと次のパルスのエッジの期間、FOをカウントするCONT17と、TDC13、14、FF15の出力を入力し、カウンタの出力を受け、FRとFDの位相差を演算するPERR16と、PERRの出力を入力し、フィルタ処理した信号をDCOに供給するDFIL18を備える。

(もっと読む)

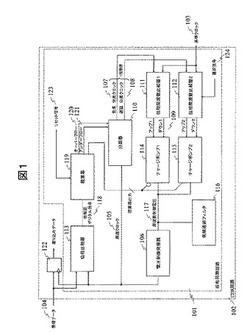

位相同期ループ回路

【課題】必要な特性を満たしつつ、回路構成を簡素化し、省面積化を可能とするデジタルPLLの提供。

【解決手段】リファレンスクロック信号FRと分周クロック信号FDの位相差を検出するTDC101、FDとFRの進み遅れを出力するFF103、位相誤差演算器102、位相誤差(PERR)を平滑化するデジタルフィルタ104、出力クロック信号FOを出力するDCO105、FOを分周したFDを出力するN分周器106、N分周器106内のカウンタ値をFRに応答してサンプルするレジスタ107を備え、TDC101は、位相差検出測定範囲がFOの1周期以内とされ、FRとFDの位相差をFOの1周期に換算した小数で出力し、位相誤差演算器102は、FDとFRの位相差が、FOの周期の整数倍以上のときは、レジスタ107出力と符号情報signから、FOの1周期内のときは、TDCの出力と符号情報signからPERRを演算出力する。

(もっと読む)

クロック生成回路および電子機器

【課題】クロック生成回路の回路規模を抑制しつつ、クロック信号の周波数スペクトルを好適に拡散する。

【解決手段】クロック生成回路1の電流制御発振部13は、供給される電流に応じた遅延量で信号を遅延する複数の電流制御遅延回路11を含む閉ループ12によりクロック信号を生成する。位相制御部15〜18は、クロック信号と基準信号とを比較する比較器15を有し、これらの信号の位相差を減らすように変化する制御電流を、複数の電流制御遅延回路11に供給する電流として出力する。拡散電流生成部19は、複数の電流制御遅延回路11の一部に対して、制御電流の替わりに、制御電流と異なる電流値のスペクトラム拡散電流を供給する。

(もっと読む)

PLL回路、PLL回路の動作方法およびシステム

【課題】 回路規模を増加することなく、PLL回路の精度を向上する。

【解決手段】 時間計測回路は、基準クロックの遷移エッジが現れてから、出力クロックの遷移エッジが2回現れるまでの時間間隔をカウント値として計測する。位相差正規化回路は、計測された時間間隔を出力クロックのクロック数で表される微少位相差に正規化する。また、位相差正規化回路は、PLL回路のロック後に、”1”または”2”を示す微少位相差が連続して現れるときに、”1”と”2”がランダムに現れるまで正規化係数を徐々にずらす。演算回路は、出力クロックの積算値から微少位相差の値を引いた値を、周波数制御語の積算値から差し引いて、基準クロックと出力クロックの位相差を示す位相差信号を生成する。発振回路は、基準クロックと出力クロックの位相を合わせるために、位相差信号に基づいて出力クロック信号の周波数を変更する。

(もっと読む)

デジタル位相差検出器およびそれを備えた周波数シンセサイザ

【課題】高精度で回路面積および消費電力が小さいデジタル位相差検出器を提供する。

【解決手段】デジタル位相差検出器は、第1の信号を累積的に遅延させて各遅延量の信号を生成する遅延回路(10)と、第2の信号に同期して各遅延量の信号をラッチするフリップフロップ群(20)と、フリップフロップ群の出力から、第1の信号の立ち上がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第1の位相差、および第1の信号の立ち下がりと第2の信号の立ち上がりおよび立ち下がりのいずれか一方との第2の位相差を検出するエッジ検出器(30)と、第1および第2の位相差を記憶する記憶回路(40)と、記憶回路が記憶している過去の第1および第2の位相差の差分およびエッジ検出器が新たに検出した第1および第2の位相差の差分から第1の信号の周期を算出し、当該周期を基準にして第1および第2の信号の位相差を正規化する正規化回路(50)とを備えている。

(もっと読む)

時間デジタル変換回路、及びその校正方法

【課題】高分解能のTDC回路の消費電力を低減することを目的とする。

【解決手段】本発明に係るTDCは、入力信号を遅延する遅延素子11を複数直列に接続するディレイラインと、ディレイラインの最後段の遅延素子の出力の反転信号を出力する反転素子13と、基準クロック、又は反転素子の出力信号のいずれかをディレイラインの初段の遅延素子に提供するマルチプレクサ15と、を有するリング発振器10と、ディレイラインの遅延素子の接続ノード、又は初段の遅延素子の入力ノードに接続され、被測定信号の変化エッジが、遅延素子11の出力する基準クロックを遅延した信号の変化エッジに対して進んでいるか遅れているかを判定する複数の判定回路17と、判定回路17の判定結果をエンコードするエンコーダ回路31と、エンコーダ回路31の出力から、被測定信号の変化エッジの基準クロックに対する位相を算出する演算回路33と、を備える。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

半導体装置及びその測定方法

【課題】従来の測定方法では、測定電流の精度を十分に確保できない問題があった。

【解決手段】本発明の半導体装置の測定方法は、外部端子TMと、出力信号の位相及び周波数に応じてチャージポンプ回路12を制御する位相周波数比較器11と、周波数制御電圧生成ノードVNDに対する電流を出力するチャージポンプ回路12と、チャージポンプ回路12が出力する電流に応じて周波数制御電圧を周波数制御電圧生成ノードVNDに生成するループフィルタ14と、周波数制御電圧に応じて出力信号の周波数を制御する電圧制御発振器15と、を有する半導体装置の測定方法であって、外部端子TMを介してチャージポンプ回路12の出力電流を含む第1、第2の測定電流のいずれか一方を測定し、外部端子TMに流れるリーク電流を含む第3の測定電流を測定し、第1、第2の測定電流とリーク電流との差分に基づき流出電流IS1又は流入電流IS2の電流値を算出する。

(もっと読む)

デジタルPLL

【課題】位相差情報をデジタル値で出力するデジタルPLLにおいて、消費電力を抑えたデジタルPLLを提供することにある。

【解決手段】デジタルPLL100は、発振器10、整数位相算出部20、小数位相算出部30、位相差算出部40、位相差変化量モニタ部50、および発振器制御部60を有する。PLLにおいては発振器の出力周波数が、分周比により設定された所望の周波数に近づく、即ちロック状態に近づくにつれ位相差の変化量は減少していくことから、位相差変化量モニタ部50にて位相差の変化量をモニタし、変化量が整数位相算出部20の1LSB未満である「1」未満になった時点で整数位相算出部20におけるカウンタ動作を停止する。

(もっと読む)

位相調整回路及び位相調整方法

【課題】消費電力を低減し、かつ回路面積も小さい位相調整回路を提供すること

【解決手段】位相調整回路100は、複数の遅延素子回路121〜124をリング状に結合したVCO120を有するPLL発振回路100を備える。また位相調整回路100は遅延素子回路を所望の遅延量に応じた数(125〜127)だけ有し、入力信号に前記所望の遅延量を与える位相遅延回路200、210を備える。PLL発振回路100は基準クロックの入力に応じた基準信号に、基準信号の所定周期分の遅延を与えた発振信号をVCO120において生成する。PLL発振回路100は、基準信号と、発振信号に応じた信号と、が略同位相となるように算出された遅延量に応じた遅延制御信号を遅延素子回路121〜124、及び遅延素子回路125〜127の各々に対して入力する。

(もっと読む)

クロック信号生成装置及び電子装置

【課題】目標周波数が変更されても、生成するクロック信号の周波数を短時間で目標周波数に一致させるクロック信号生成装置、及び、電子装置を提供することを目的とする。

【解決手段】第1制御部は、設定された目標周波数が第1の目標周波数から第2の目標周波数に変更されると、第1の所定のタイミングで、第1設定数として第3の数よりも小さい第5の数を前記第1カウンタに設定するとともに、第2設定数として第4の数よりも小さい第6の数を前記第2カウンタに設定し、第1の所定のタイミングの後の第2の所定のタイミングで、第3の数を前記第1カウンタに設定するとともに、前記第4の数を前記第2カウンタに設定する。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

DPLL回路

【課題】入力データに混入したノイズの幅がクロック周期程度にまで大きくなり、ノイズ位置が入力データの中間位置に発生した場合にも、入力データからノイズを除去できる。

【解決手段】1ビットを4クロック幅で構成する入力データからノイズフィルタで雑音を除去し、この雑音を除去した入力データと同期したクロックを生成するDPLL回路において、ノイズフィルタは、入力データに対して、4段縦続接続のシフトレジスタを設け、このシフトレジスタのレジスタ11,12,13のクロック同期した出力の一致・不一致状態に応じて最終段のレジスタ16の入力を切り替える入力ロジック17を設ける。

さらに、ノイズフィルタでは除去しきれない入力データの歪みを歪み除去回路で除去する。

(もっと読む)

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

位相同期ループ回路、半導体集積回路、電子機器、位相同期ループ回路の制御方法

【課題】位相同期ループ回路において、制御応答の改善や消費電力の低減を図る。

【解決手段】発振器制御部255と分周器制御部257は、発振制御信号と分周制御信号が、引込み過程およびロック時の双方において、ループフィルタ電圧に基づいて比例関係を持って連動して変化するようにする。発振部210と分周部220が引込み過程およびロック時の双方において連動した動作をする。引込み過程およびロック時の双方における任意のループフィルタ電圧に対応する分周部220の最高動作周波数が発振部210の発振出力信号の周波数よりも常に高くなるように各制御信号の関係を設定する。ロック時の分周制御信号は、引込み過程における発振部210の発振出力信号の最高周波数と対応するループフィルタ信号に基づくバイアス電流よりも小さなバイアス電流を分周部220に自動的に設定するようになる。このことにより、ロック時の電力消費を低減できる。

(もっと読む)

PLL回路

【課題】ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路を提供する。

【解決手段】PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、信号遅延に応じて第3のクロック信号を発振する発振回路とを含み、フィルタ回路は、第1の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、第2の遅延回路により第1のクロック信号をフィルタ処理して第2のクロック信号を生成する。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

デジタルクロック再生器

サンプリング装置(110)は、変動する周期時間を有する入力クロック信号(CLKin)を受信し、入力クロック信号(CLKin)の平均周波数より実質的に高い周波数を有するサンプリングクロック信号(CLKsmpl)に基づいて、入力クロック信号(CLKin)をサンプリングする。サンプリング装置(110)は、入力クロック信号(CLKin)の各周期に対して、各周期長値(PL)を生成する。平均化装置(120)は、いくつかの周期長値(PL)をサンプリング装置(110)から受信し、それに基づき、前記数の周期長値(PL)に等しい周期数を含む平均化期間に渡って、入力クロック信号(CLKin)に対して平均周期時間を表す平均周期長値(PLavg)を生成する。出力装置(151)は、平均周期長値(PLavg)およびサンプリングクロック信号(CLKsmpl)に基づいて、安定した出力クロック信号(CLKout)を生成する。 (もっと読む)

41 - 60 / 213

[ Back to top ]