Fターム[5J106AA05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412) | デジタルPLL (213)

Fターム[5J106AA05]に分類される特許

21 - 40 / 213

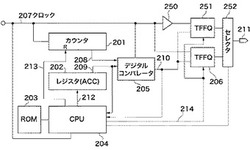

PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

(もっと読む)

半導体装置

【課題】DLL回路の調整を素早く完了する。

【解決手段】第1のクロック信号(図2のCLKIN)を遅延させて第2のクロック信号(図2のLCLK)を生成する遅延部(図2の33、34が相当する)と、第1のクロック信号と、第2のクロック信号をさらに遅延した信号(図2のRCLK)との位相を比較する位相比較回路(図2の36)と、遅延部の遅延量を決定するカウント値を遅延部に出力すると共に、位相比較回路の位相比較結果に応じてアップダウンするカウンタ回路(図2の37)と、初期設定動作時において、第1のクロック信号の周期を検知し、検知した周期に応じたカウント値の初期値をカウンタ回路に対して出力する初期遅延量制御回路(図2の30)と、を備える。

(もっと読む)

デジタル位相同期回路および物理量検出センサ

【課題】簡単な構成で位相同期を行うことができるデジタル位相同期回路および物理量検出センサを提供する。

【解決手段】位相比較部は、サンプリング値の符号情報を示す符号クロックCLK1と分周器の分周クロックCLK2との位相差を算出する。このとき、位相比較部は、符号クロックCLK1による立上りタイミングからダウンカウントし、分周器の分周クロックCLK2による立下りタイミングにてアップカウントし、符号クロックCLK1による立上りタイミングにて得られたカウント値を位相比較カウント値として出力する。そして、加算器が、位相比較カウント値に位相補正部の位相補正値を加算してループフィルタに出力する。

(もっと読む)

アキュムレータ型フラクショナルN−PLLシンセサイザおよびその制御方法

【課題】フラクショナル分周器の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制したアキュムレータ型フラクショナルN−PLLおよびその制御方法を実現する。

【解決手段】アキュムレータ型フラクショナルN−PLLシンセサイザ100を、その参照信号入力側の位相検出器の前段にアキュムレータ120からの誤差信号によって上記参照信号に対し位相調整を行う位相調整回路130を介挿して構成し、出力段のVCO114の出力を前段側にフィードバックするフラクショナル分周器115の出力である帰還信号と、上記位相調整された参照信号との両信号の位相差が生じないようにして、該両信号の位相差に応じた出力を得る位相検出器111の出力によってチャージポンプ112が駆動されないようにすることによって、フラクショナル分周器115の分周数を周期的に切り替えることに起因するフラクショナルスプリアスを抑制するように構成する。

(もっと読む)

デジタルPLL回路及びクロック生成方法

【課題】位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供する。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

PLL

【課題】ジッタが抑制されたPLLを提供する。

【解決手段】PLLは,基準クロックとフィードバッククロックとの位相差信号を遅延し,異なる時間遅延させた位相差信号に応じてチャージ電流を生成する複数のチャージポンプCPを有す。また当該複数のチャージポンプが生成するチャージ電流を加算して出力するチャージポンプ等化器と,ループフィルタと電圧制御発振器の理想特性を持ち,位相差信号の位相差を有する位相差デジタル値を入力して理想特性に基づいてレプリカ出力を生成するレプリカ回路10と,レプリカ出力と理想出力との誤差信号と前記位相差信号との相関値を平滑化してチャージポンプ係数を生成し,複数のチャージポンプそれぞれに負帰還する係数生成回路20−1とを有し、複数のチャージポンプはチャージポンプ係数に応じた電流値を持つチャージ電流をそれぞれ生成する。

(もっと読む)

スペクトラム拡散クロックジェネレータ

【課題】 残ピークノイズを低減させることができるとともに、ジッターの増大を防止することのできるスペクトラム拡散クロックジェネレータを提供する。

【解決手段】 実施形態のスペクトラム拡散クロックジェネレータは、チャージポンプ回路1が、出力電流量が設定に応じて変化する可変電流源を有し、位相比較器14により検出された位相差に応じた期間、VCO11へ印加する電圧を制御するためのチャージ電流を出力する。

(もっと読む)

デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法

【課題】デジタル位相周波数検出器、それを含むデジタル位相固定ループ、及びデジタル位相周波数検出方法を提供すること。

【解決手段】デジタル位相周波数検出器は検出部、位相比較部及びリセット部を含む。検出部は基準信号及びフィードバック入力信号のエッジを検出して基準エッジ信号及びフィードバックエッジ信号を発生する。リセット部は基準エッジ信号及びフィードバックエッジ信号に基づいてリセット信号を発生する。位相比較部は基準エッジ信号及びフィードバックエッジ信号に基づいて第1位相比較信号及び第2位相比較信号を発生し、第1フリップフロップ、第2フリップフロップ、及びラッチブロックを含む。第1フリップフロップは基準エッジ信号を受信するデータ入力端及びフィードバックエッジ信号を受信するクロック入力端を具備し、第2フリップフロップはフィードバックエッジ信号を受信するデータ入力端及び前記基準エッジ信号を受信するクロック入力端を具備する。

(もっと読む)

PLL回路

【課題】PLL回路のロック状態での定常位相誤差を抑制する。

【解決手段】PLL回路は,レファレンスクロックとフィードバッククロックの位相を比較し,当該位相の差を示す位相比較信号を出力する位相比較器と,位相比較信号が示す位相の差に応じた期間,第1のチャージポンプ電流と第2のチャージポンプ電流とを出力するチャージポンプ回路と,第1及び第2のチャージポンプ電流に基づく電荷を蓄積するキャパシタを有し,蓄積電荷による制御電圧を生成するループフィルタと,制御電圧に応じた周波数の出力クロックを生成する発振器と,出力クロックを分周して前記フィードバッククロックを出力する分周器とを有し,さらに,ロック状態のときに,位相比較信号が示す位相の差に応じて,当該位相の差が抑制されるように,第1または第2のチャージポンプ電流の電流値を調整するチャージポンプ調整回路とを有する。

(もっと読む)

小数点分周PLL回路および集積回路

【課題】ループフィルタのカットオフ周波数を低く設定することなく、スプリアスを抑制する。

【解決手段】基準発振器で生成された基準周波数を所定の基準クロックに分周する第1の分周器103と、電圧制御発振器で生成された発振周波数を所定の帰還クロックに小数点分周する第2の分周器105と、基準クロックと帰還クロックとの位相を比較する位相比較器106と、位相比較器106による比較結果に基づいて電圧制御発振器の発振周波数を制御するチャージポンプ107と、を備えた小数点分周PLL回路1において、第1の分周器103側の電源パッド1−2と、第2の分周器105側の電源パッド1−1と、位相比較器106側の電源パッド1−3と、チャージポンプ107側の電源パッド1−4とを、それぞれ別個に備える。

(もっと読む)

PLL回路、PLL回路の誤差補償方法及び通信装置

【課題】デジタル制御発振器を持つPLL回路に用いられるTDC回路の有限な分解能により発生する周期性誤差を補償することが可能なPLL回路を提供する。

【解決手段】発振回路の累積クロック数をデジタル値として検出する累積クロック数検出部と、前記発振回路の累積クロック数の小数部のデジタル値の、第1の基準クロックを基準とする周期性を検出する周期検出部と、前記発振回路の出力クロックの1周期のデジタル値、前記発振回路の累積クロック数の小数部が持つ周期性の1周期のデジタル値、および前記発振回路の累積クロック数の小数部が持つ周期性の各周期の開始点から前記第1の基準クロック数をカウントした値から補正値を算出する補正値算出部と、前記周期性の各周期の開始点から前記第1の基準クロックの周期で、前記累積クロック数の小数部に前記補正値を加算する加算部と、を備える、PLL回路が提供される。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

分周回路およびそれを備えたPLL回路並びに半導体集積回路

【課題】回路規模および消費電力を増大させることなく、回路全体の分周比の可変範囲をより拡大することのできる分周回路を実現する。

【解決手段】周期信号(s5)を2種類の分周比で分周して第1の分周信号(c1)を出力する可変分周器(2)と、第1の分周信号(c1)のサイクル数のカウント値(c2)を出力し、リセットされるとカウント動作を初期値から再開するカウンタ回路(3)と、カウント値(c2)が比較基準値(a)と一致する度にHighとLowとを反転させたパルス信号(s1)を、第2の分周信号として出力するとともに分周比の切替信号として可変分周器(2)に供給し、カウント値(c2)が比較基準値(a)と一致する度にカウンタ回路(3)にリセット信号(r)を出力する比較器(4)と、比較器(4)に比較基準値(a)を供給する制御回路(5)とを備えている。

(もっと読む)

クロック発生器、電子機器、及びクロックを発生するための制御方法

【課題】周波数変調機能をオフした際のロックアップタイムを短縮することが可能なクロック発生器、及びクロック発生器の制御方法、並びに電子機器を提供すること。

【解決手段】周波数変調機能を有するクロック発生器で、リファレンスクロックを元にフィードバック制御を加えて、位相の同期した出力クロックを出力する位相同期ループと、出力クロックの周波数を変動させる変調制御回路と、を備え、変調制御回路は、周波数変調機能がオフされた際に、出力クロックの周波数を所望の周波数へ収束させるタイミングを速くする構成とする。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

位相同期回路

【課題】位相同期回路においてロックアップを高速化する。

【解決手段】位相同期回路100は、基準信号の周波数にXを乗じて得られる出力周波数を有し、基準信号源180と、電圧制御発振器110と、位相比較器120と、第1チャージポンプ130と、ループフィルタ150と、カウンタ161と、第2チャージポンプ170と、制御回路164とを備える。電圧制御発振器110は、第1信号、および逆相の第2信号を生成する。スイッチ140は、第1チャージポンプ130で生成された電流信号をループフィルタ150に供給する。カウンタ161は、基準信号の1周期期間に含まれる、第2信号のサイクル数をカウントする。第2チャージポンプ170は、互いに反対符号の第1電流信号と第2電流信号をループフィルタ150に供給可能である。制御回路164は、サイクル数とXの値との比較に基づき、スイッチ140および第2チャージポンプ170を制御する。

(もっと読む)

局部発振器

【課題】PVTに依存しない安定した位相雑音特性を短時間で得ることができる局部発振器を提供する。

【解決手段】局部発振器は、デジタル制御発振器と、位相データ生成器と、減算器と、ループフィルタと、乗算器と、係数算出器と、を備える。前記デジタル制御発振器は、第1の発振器制御値により発振信号の発振周波数を制御可能である。前記発振周波数は、前記第1の発振器制御値と、前記第1の発振器制御値の単位値あたりの前記発振周波数の変化量と、の積に等しい。設定周波数データは、設定周波数を基準信号の基準周波数で除算して得られる。前記乗算器は、前記ループフィルタからの規格化制御値に第1の係数を乗算した前記第1の発振器制御値を出力する。前記係数算出器は、前記発振周波数が前記設定周波数に略等しくなった時の前記第1の発振器制御値を、前記設定周波数データで除算し、その除算結果を新たな前記第1の係数として前記乗算器に設定する。

(もっと読む)

PLL周波数シンセサイザ

【課題】位相雑音特性の劣化を回避し消費電力を低減するデジタルPLL周波数シンセサイザを提供する。

【解決手段】デジタルPLL周波数シンセサイザ101において、ロック検出後に第1の発振信号位相情報から、前回の発振信号位相情報と位相差εとから推定部20にて推定した第2の発振信号位相情報に切り替えることにより、通常状態(ロック状態)において誤差を持つ危険を抱えた第1の発振信号位相情報を使用せず、また、従来のリクロックのための高速動作するラッチ回路も不要とする。これにより、位相雑音特性の劣化を回避しつつ、従来に比べて消費電力を低減する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

21 - 40 / 213

[ Back to top ]