Fターム[5J106AA05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412) | デジタルPLL (213)

Fターム[5J106AA05]に分類される特許

101 - 120 / 213

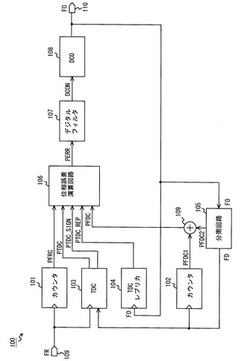

デジタルフェーズロックドループ回路

【課題】従来のADPLL回路では、出力クロックにデューティ劣化がある場合、最終的に導き出される位相差に大きな誤差が生じてしまう。

【解決手段】第1クロックをカウントする第1カウンタと、第2クロックを分周した第3クロックをカウントする第2カウンタと、第3クロックの遅延クロックと第1クロックを比較した第1比較結果と、第1クロックの遅延クロックと第3クロックを比較した第2比較結果とに応じ第1、第3クロックの相対的位相差を検出する第1位相検出器と、第2クロックの周期を測定する第2位相検出器と、第2位相検出器の検出結果により第1位相検出器の検出結果を正規化した値と、第1、第2カウンタの値とに応じて第1、第3クロックとの位相差を演算する位相誤差演算部と、位相誤差演算部の演算結果に応じ第2クロックを出力するDCOとを有するデジタルPLL回路。

(もっと読む)

デジタル位相ロック・ループ(DPLL)、デジタル位相ロック・ループ(DPLL)内のジッタを制御するための方法、デジタル制御発振器(DCO)内のディザを最適化するための方法、および自己ディザリング・デジタル制御発振器(DCO)回路

【課題】 デジタル位相ロック・ループ(DPLL)および方法を提供する。

【解決手段】 デジタル位相ロック・ループ(DPLL)および方法は、入力として基準クロックを受け取り、ディザリングした基準クロック信号を出力するように構成された調整可能遅延線を含む。位相周波数検出器(PFD)は、ディザリングした基準クロック信号をフィードバック・クロック信号と比較して、ディザリングした基準クロック信号とフィードバック・クロック信号との位相および周波数の差を決定するように構成される。デジタル制御発振器(DCO)は、PFDから早遅判断を受け取り、それに応じて出力を調整するように構成され、ディザリングした基準クロック信号はDPLLの全体的な動作を強化するためにジッタ応答を分散する。

(もっと読む)

DLL回路及びこれを備える半導体装置、並びに、データ処理システム

【課題】短時間でロックさせることが可能なDLL回路を提供すること。

【解決手段】外部クロックCKと内部クロックLCLKの立ち上がりエッジの位相を比較する位相判定回路111と、外部クロックCKと内部クロックLCLKの立ち下がりエッジの位相を比較する位相判定回路112と、判定結果に基づいて内部クロックLCLKR,LCLKFのアクティブエッジの位置を調整する調整部120と、内部クロックLCLKR,LCLKFのアクティブエッジの調整方向とが互いに同方向であることに応答して内部クロックLCLKR,LCLKFの調整量の一方を他方よりも大きくする制御回路150とを備える。これにより、位相調整しながらデューティを50%に近づけることが可能となることから、DLL回路のロックに要する時間を短縮することが可能となる。

(もっと読む)

デジタルPLL回路及びデジタルPLL動作方法

【課題】CLVスピンドル制御のランダムシーク時でもスループット低下を抑え、かつ安価で消費電力を抑えたワイドキャプチャ対応のデジタルPLL回路を提供する。

【解決手段】本発明のデジタルPLL回路10Aは、周波数値fq’に応じてマスタクロックsclkの周波数を切り替えるマスタクロック切り替え手段10Bと、周波数値fq’に一定の倍率を乗じて数値制御発振器6へ出力するとともに、マスタクロックsclkの周波数が切り替わる前後で同期クロックgclkの周波数が一定になるように前記倍率を切り替える倍率切り替え手段10Cと、を備えたことを特徴とする。

(もっと読む)

位相同期回路、および通信装置

【課題】設定される動作モードに基づいて処理信号の処理クロック周波数を動作モードに基づいて切り替え、消費電力の低減を図ることが可能な位相同期回路、および通信装置を提供する。

【解決手段】デジタル値で表される発振制御信号に基づく発振周波数の発振信号を出力する発振回路と、搬送波周波数が基準周波数で除算された分周比と動作モードを規定する制御信号とが入力され、分周比を制御信号に基づいて設定された整数値で除算する第1ビットシフト部と、発振信号に基づく信号と制御信号とが入力され制御信号に基づいて設定された整数値により発振信号に基づく信号を分周する第1分周部と、基準周波数信号の各周期において第1累積加算値と第2累積加算値および累積位相の小数部とを比較し位相比較信号を出力する位相比較部と、位相比較信号を制御信号に基づく任意の収束値に収束させ発振制御信号を出力するデータ変換部とを備える位相同期回路が提供される。

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

制御装置、クロック同期方法

【課題】DPLL回路において、入力クロックの瞬間的な位相跳びによる出力クロックの位相跳びの発生を抑制する。

【解決手段】出力クロックを入力クロックに同期させる制御を行う制御装置は、前記入力クロックと前記出力クロックとの位相差をカウントするカウント部と、前記カウント部がカウントした位相差のうち、所定範囲内の位相差を示すカウント値を抽出する抽出部と、抽出された前記所定範囲内の位相差を示すカウント値に基づいて位相差情報を生成する位相差情報生成部と、前記位相差情報生成部により生成された前記位相差情報に基づいて、生成する前記出力クロックの周波数を制御可能なクロック生成部と、を備える。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

遅延制御方法および遅延装置

【課題】遅延装置の回路規模を抑制する。

【解決手段】DLL回路120は、遅延素子122に入力された基準クロックが遅延素子122により1周期分遅延されるように遅延素子122を制御する第1の制御信号CTR1を生成する。遅延素子140は、遅延素子122と同一の構成を有し、外部からのストローブ信号S1を、第2の制御信号CTR2に応じた遅延量の分だけ遅延させる。ストローブ遅延制御回路130は、第1の制御信号CTR1と、遅延素子140による遅延量の期待値とから、遅延素子140に出力する第2の制御信号CTR2を生成する。クロック供給回路110は、遅延素子140に入力されるストローブ信号S1の周波数より高い周波数を有する基準クロックをDLL回路に供する。

(もっと読む)

PLL回路

【課題】PLL回路において、アナログ回路のデジタル化によって生じる量子化雑音を抑制することができる技術を提供する。

【解決手段】基準信号REFと分周後の信号DIVとの位相及び周波数を比較してデジタル値に変換するデジタル位相周波数比較器(DPFD)101と、デジタル位相周波数比較器101の出力から高周波雑音成分を除去するデジタルループフィルタ(DLF)102と、デジタルループフィルタ102の出力のデジタル値をアナログ値に変換するデジタルアナログ変換器(DAC)105と、デジタルアナログ変換器105の出力から高周波雑音成分を除去するアナログフィルタ(AnF)106と、アナログフィルタ106の出力に基づいて周波数が制御される電圧制御発振器(VCO)103と、電圧制御発振器103の出力を分周し、分周後の信号DIVを出力する分周器(DIV)104とを備える。

(もっと読む)

低電力非同期カウンタ及び方法

【解決手段】低電力非同期カウンタの設計技術。典型的な実施形態では、複数のフリップフロップのクロック入力及び信号出力が、非同期カウント構造を実現するように直列に連結される。複数のフリップフロップの信号出力は、参照信号の順次遅延されたバージョンによってサンプリングされる。更に、参照信号の順次遅延されたバージョンを生成する設計方法が開示される。典型的な実施形態では、非同期カウント技術は、デジタル位相ロックループ(DPLL)の高速カウンタに使用され得る。 (もっと読む)

同期周波数合成器

【課題】同期周波数合成器によるクロック生成装置を提供する。

【解決手段】クロック生成装置において、2つの入力クロックに関連付けられた基準位相の範囲内の位相値を有する出力を生成する位相補間器121を有する。ロジック・ユニット130は、位相補間器121の複数の位相設定を決定するために結合され、分周器122は位相補間器121に結合され、変更可能な分周設定に基づき出力クロックを生成する。

(もっと読む)

発振回路、DC−DCコンバータ及び半導体装置

【課題】CPUなどの特別な制御回路が不要で、しかも無線送受信回路で用いている周波数に関わりなく、スイッチングノイズの影響を無視できるレベルまで軽減することが可能な発振周波数制御回路を提供する。

【解決手段】周波数が下限周波数と上限周波数の間を連続的に変化しながら往復する発振回路において、アップダウン制御回路20は、第1の検出回路30がクロック信号のハイレベル又はローレベルの時間が第1の遅延時間以下になったことを検出した場合は、ダウン信号を可変周波数発振回路に出力し、第2の検出回路40がクロック信号のハイレベル又はローレベルの時間が第2の遅延時間以上になったことを検出した場合は、アップ信号を可変周波数発振回路10に出力する。

(もっと読む)

受信装置

【課題】PLLモジュールICを用いたWCDMA無線基地局装置の受信機において、従来から存在するSIR測定機能を利用して、PLLモジュールICの変調感度によるループゲイン変動を打ち消すようなIcp設定値を選択して常に安定したPLL動作を可能にし、高品質な受信特性を提供することである。

【解決手段】PLLモジュールICを用いたWCDMA無線基地局装置の受信機において、SIRを測定するSIR測定手段と、前記SIR測定手段によってSIRを測定し、該測定結果に基づいてチャージポンプ電流を調整するよう制御する制御手段と、を備えたことを特徴とする。

(もっと読む)

半導体集積回路及びその制御方法

【課題】本発明は、安定ているクロックを生成するために、DLL回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供する。

【解決手段】本発明の半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するDLL制御手段;及び、バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するDLL回路を含む。

(もっと読む)

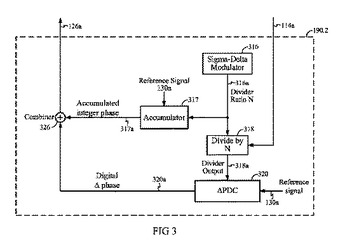

ディジタル位相ロックループにおける累算された位相−ディジタル変換

ディジタル位相ロックループ(DPLL)において信号の累算された位相をディジタル値に変換するための技術。模範的な実施形態では、信号が、分周器比Nで信号の周波数を分割するN分割モジュールと対にされる。分割された信号は、分割された信号の立ち上がりエッジと基準信号の立ち上がりエッジとの位相差を測定するデルタ位相−ディジタル変換器へ入力される。累算された分周器比群と較正された位相差群とが合算され、累算されたディジタル位相が生成される。シグマ−デルタ変調器を用いて分周器比Nを変える更なる技術が示される。  (もっと読む)

(もっと読む)

TDC回路、PLL回路、並びに無線通信装置

【課題】入力信号とトリガ信号の間に遅延時間が存在するというフリップフロップ自身の特性に起因した検出誤差を改善するTDC回路を提供する。

【解決手段】各フリップフロップ105−1、…は、CLKREF、B2からDelay1だけ遅延したタイミングをトリガにして入力信号A0、A1、A2をそれぞれ保持し、データ系列[C0:C3]として“1110”を得る。例えば、[C0:C1]が“11”の場合は遅延量の符号をマイナスとし、[C2:C3]を左から1から0に変化する点をカウントすることでデコードされる。よって、この例では、“−1”とデコードされ、Delay=−Dを検出する。

(もっと読む)

クロック・データ・リカバリ回路

【課題】

USB2.0規格などの高速シリアル通信に用いるクロック・データ・リカバリ回路に関し、受信データの取り込みエラーを防止し、かつLSI化に適した回路を提供する。

【解決手段】

周期T1のクロックをN分割したT2単位でずらしたN相のクロックを出力する手段6、シリアル転送された信号をT2毎にサンプリングしてT1毎にNビットパラレルデータに変換する手段4、その出力データをデジタル処理してNビットパラレルデータに変換する手段で、またデータ変化点を示すNビットパラレルデータに変換する手段8、変化点を示すデータを位相情報入力として前記デジタル処理されたデータのデータ変化点の略中間位置を示すデータを出力する手段10、その出力データが示したビット位置に対応する前記デジタル処理されたデータを復元データとする手段12を備える。前記デジタル処理は、移動平均処理、デューティずれ補正処理とすることができる。

(もっと読む)

グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステム

【課題】 グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステムを提供する。

【解決手段】 一実施形態のシステムは、個々のチャネルに関連する誤差信号をそれぞれ受け取る複数の入力を備えたグローバルPLL回路と、前記グローバルPLL回路と結合された遅延補償回路と、を含む。一実施形態の方法は、個々のチャネルにそれぞれ関連する複数の誤差信号を受け取るステップと、前記誤差信号に1つ又は複数の遅延補償信号を適用するステップと、前記チャネルのそれぞれに関する位相誤差出力信号を出力するステップと、を含む。

(もっと読む)

位相検出装置、位相検出方法、再生装置及び再生方法

【課題】

記録媒体から再生される再生信号とクロック信号との位相差を正確に検出することが可能な位相検出装置、位相検出方法、該位相検出装置を備えた再生装置、再生方法を提供する。

【解決手段】

位相同期回路39がリミット位相ディテクタ41を備えるので、例えば図4に示すゼロクロスのタイミング(C)が検出されたとき(ST605でYES)、クロックカウンタ47によるカウント値と所定の値とを比較し(ST606)、カウント値が所定の値より小さいときに(ST606でNO)Cから次のクロックの立ち上がりまでの間、位相カウンタ51をイネブルでない状態とすることができる。つまり、リミット位相ディテクタ41(の位相カウンタ51)の出力を無効にすることができる。この結果、例えばノイズ等の影響を受け易い所定カウント値より小さいパルス幅のRF信号(入力信号)に基づき位相エラー信号が求められることを防止することができる。

(もっと読む)

101 - 120 / 213

[ Back to top ]