Fターム[5J106AA05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412) | デジタルPLL (213)

Fターム[5J106AA05]に分類される特許

81 - 100 / 213

通信装置及びその折り返し試験方法

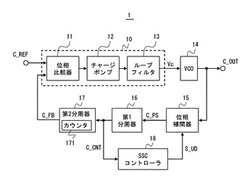

【課題】SSCのジッタを抑制し、SSCの変調度を滑らかに遷移させることが可能なSSC生成機能を有するPLL回路及び通信装置を提供する。

【解決手段】SSCコントローラ18は、SSCの変調プロファイルに応じて予め定められたタイミングで位相シフト量を変更するよう位相補間器15を制御し、出力クロック信号C_OUTの変調度を周期的に変更させる。さらに、SSCコントローラ18は、帰還クロック信号C_FBの一周期内において位相補間器15より出力される位相シフト信号C_PSに与える総位相シフト量を、当該総位相シフト量と直前の一周期における総位相シフト量との差分が常に基本遅延量Δ以下となるよう制御する。ここで、基本遅延量Δは、出力クロック信号C_OUTの周期T_OUTを位相補間器15の位相分解能Nrで除算した値(つまり、T_OUT/Nr)である。

(もっと読む)

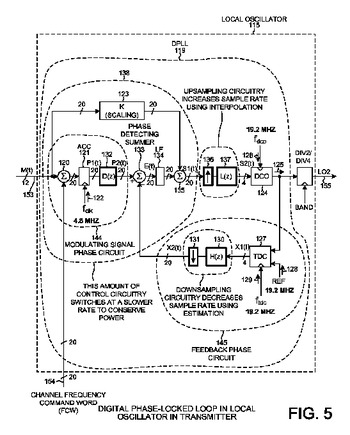

異なるサンプルレートで動作する部分を有するデジタル位相同期ループ

デジタル位相同期ループ(DPLL)は、DCO出力信号及び基準クロックを受信し及びデジタル値の第1のストリームを出力する時間−デジタル変換器(TDC)を含む。TDCを高レートでクロックすることによって量子化雑音が低減される。ダウンサンプリング回路は、第1のストリームを第2のストリームに変換する。第2のストリームは、DPLLの制御部が電力消費量を低減させるためにより低いレートで切り替わることができるようにDPLLの位相検出加算器に供給される。従って、DPLLは、マルチレートDPLLと呼ばれる。制御部によって出力されたデジタルチューニングワードの第3のストリームは、DCOをより高いレートでクロックし、それによってデジタルイメージを低減させることができるようにDCOに供給される前にアップサンプリングされる。受信機用途においては、アップサンプリングは行われず、DCOはより低いレートでクロックされ、それによって電力消費量をさらに低減させる。  (もっと読む)

(もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】安定した位相同期ループを構成できない。

【解決手段】本発明は、第1、第2のクロック信号をカウントする第1、第2のカウンタと、第1のクロック信号を遅延させた第1、第2の遅延クロック信号を生成する遅延クロック生成回路と、第1のクロック信号及び第1、第2の遅延クロック信号のそれぞれで第2のカウンタのカウント値をサンプリングするサンプル回路と、第1、第2のクロック信号を所定の数で分周した第3のクロック信号との位相差と、サンプリングしたカウント値に応じ、そのサンプリングしたカウント値のうち1つを選択する選択回路と、第1のカウンタ及び選択回路が選択したカウント値に応じて第1、第3のクロックとの位相差を演算する位相誤差演算回路と、位相誤差演算回路の演算結果に応じて第2のクロックを出力するデジタル制御発振器とを有するデジタルフェーズロックドループ回路である。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

アキュムレータおよび位相デジタル変換器を使用する2ポイント変調のデジタル位相同期ループ

2ポイント変調をサポートするデジタル位相同期ループ(DPLL)が説明される。1つの設計において、DPLLは、位相デジタル変換器、ループ内で動作するループフィルタ、ローパス変調パスのための第1の処理ユニットおよびハイパス変調パスのための第2の処理ユニットを含む。第1の処理ユニットは、入力変調信号を受信し、位相デジタル変換器の後でループフィルタより前のループの内部の第1のポイントに対して第1の変調信号を供給する。第2の処理ユニットは、入力変調信号を受信し、ループフィルタより後のループの内部の第2のポイントに対して第2の変調信号を供給する。第1の処理ユニットは、周波数を位相に変換するために入力変調信号を累算するアキュムレータを含み得る。第2の処理ユニットは、可変利得で入力変調信号をスケールするスケーリングユニットを含み得る。 (もっと読む)

クロック生成回路

【課題】位相ロックの精度を向上する。

【解決手段】クロック生成回路は、出力クロックの周期または位相を段階的に遅延する第1の遅延回路および前記第1の遅延回路の遅延時間を設定し制御する第1のカウンタを有する逓倍回路と、前記逓倍回路内の第1の遅延回路から出力された前記出力クロックを入力し、前記出力クロックを所定時間遅延させる第2の遅延回路および前記第2の遅延回路の遅延時間を設定し制御する第2のカウンタを有する位相同期回路を備え、前記逓倍回路は、初期値が第1の値であり第1のカウンタのカウンタ値が一定時間以内で変化しない場合に第2の値が設定される第3のカウンタをさらに有し、前記第3のカウンタのカウンタ値が前記第1の値から前記第2の値に変化した時、前記第2の遅延回路の遅延時間が前記第1の遅延回路の遅延時間と同じかあるいは少し長い遅延時間となるように前記第2のカウンタのカウンタ値を設定する。

(もっと読む)

改善された分解能を有する時間デジタル変換器(TDC:TIME−TO−DIGITALCONVERTER)

【解決手段】一つのインバータ遅延より小さいインバータ遅延の高分解能を含む時間デジタル変換器(TDC)が記載されている。デザイン例において、TDCは、第1及び第2の遅延パス、遅延ユニット、及び位相演算ユニットを含んでいる。第1の遅延パスは、第1の入力信号及び第1の参照信号を受信し、第1の出力を供給する。第2の遅延パスは、第2の入力信号及び第2の参照信号を受信し、第2の出力を供給する。遅延ユニットは、例えば半分のインバータ遅延によって、第1の入力信号に対して第2の入力信号を遅延する、または第1の参照信号に対して第2の参照信号を遅延する。位相演算ユニットは、第1及び第2の出力を受信し、入力信号及び参照信号間の位相差を供給する。構成は、前記第1及び第2の遅延パスについての正確なタイミングを得るために実行され得る。 (もっと読む)

非重複クロック生成のための技術

【解決手段】望ましい周波数範囲にわたって、正確な非重複時間及びクロックフェーズ遅延時間を生成する技術が提供される。一構成において、装置はそれに結合されるクロック生成回路への制御電圧を順に生成する遅延ロックループ(DLL)回路を含む非重複クロック生成回路を備えている。制御電圧はクロック生成回路によって生成される非重複遅延クロック信号の正確なタイミング関係を維持するように動作する。一態様において、DLL回路は知られたデューティサイクルによる入力クロックを受信し、入力クロックサイクルの特定の部分へのユニット遅延をフィックスする出力制御電圧を得る。更なる態様において、クロック生成回路は製造プロセス変化とは関係ない非重複時間(tnlp)でクロック信号の第1のセットから遅延されたクロック信号の第2のセット及びクロック信号の第1のセットを生成するDLL回路に結合される複数の電圧制御遅延セルを備えている。 (もっと読む)

クロック供給装置

【課題】運用系および待機系システムクロックの位相を、バックボード間の配線遅延量、温度変化および電圧変動に起因するバッファ遅延の変化量を含め一致させたシステムクロック供給装置を提供する。

【解決手段】システムクロック1に位相同期した運用系および待機系システムクロック6を出力する冗長構成とされた運用系および待機系システムクロック供給部200と運用系および待機系システムクロックを装置内各部へ分配するためのバックボード8を有する。システムクロック1に位相同期したクロック22を生成するPLL210は、運用系システムクロックを基準とし、待機系システムクロックの位相を制御する位相差調整部211を含んだ構成とする。

(もっと読む)

PLL回路

【課題】本発明の課題は、PLL回路のリファレンスリークと位相雑音を低減することである。

【解決手段】チャージポンプ回路14は、ロック状態監視回路19から出力される、PLL回路11がロック状態か否かを示す信号に基づいてチャージポンプ電流を切り換える。PLL回路11がアンロック状態のときには、第1及び第2の電流供給回路からチャージポンプ電流を供給し、ロック状態となると、第2の電流供給回路からのみチャージポンプ電流を供給する。

(もっと読む)

デジタルPLL回路

【課題】

映像信号をサンプリングするためのサンプリングクロック信号として用いても、映像に乱れを生じさせないクロック信号を生成することのできるデジタルPLL回路を提供することを課題とする。

【解決手段】

映像信号のサンプリングに用いるサンプリングクロック信号として、入力電圧に応じた発振周波数のクロック信号を出力する電圧制御発振回路と、映像信号の制御に用いられる複合同期信号と、前記電圧制御発振回路の出力に基づく帰還信号との位相差を検出する位相差検出部と、前記位相差検出部で検出される位相差が所定の範囲内にある場合は当該位相差を選択して出力し、前記位相差検出部で検出される位相差が前記所定の範囲内にない場合は前記位相差検出部で検出される位相差の目標値を出力する出力部とを含み、前記出力部の出力に基づいて、前記電圧制御発振回路の入力電圧を制御する。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

PLL回路、PLL回路無線通信機、及びPLL回路のロック検出方法

【課題】デジタル回路で構成出来、ロック検出のエラーやロストの発生を抑制することが出来ると共に、検出時間を短縮することが出来るPLL回路、無線通信機、及びロック検出方法を提供する。

【解決手段】ウィンドウ幅の異なる複数のロック検出部6b−1〜6b−nによる検出結果を用いて検出を行う。ロック判定部7は、複数のロック検出部6b−1〜6b−nによる検出結果に基づいて、ロック状態の検出を行う。

(もっと読む)

遅延ロックループのための初期化回路

【課題】遅延ロックループのための起動回路を提供する。

【解決手段】遅延ロックループにおける初期化回路は、電源投入または他のリセットの後、クロック端縁が適切な動作のために適切な順序で位相検出器によって受取られることを確実にし、遅延ロックループのリセット後、初期化回路は、遅延線における遅延を増加(または減少)させるように位相検出器をイネーブルするより先に基準クロックの少なくとも1つの端縁が受取られることを確実にし、フィードバッククロックの少なくとも1つの端縁が受取られた後、初期化回路は位相検出器をイネーブルして、遅延線における遅延を減少(または増加)させる。

(もっと読む)

リングオシレータ及びそれを用いたPLL回路

【課題】 リングオシレータで発生した高調波ノイズによる干渉を抑制できるリングオシレータ及びそのリングオシレータを備えたPLL回路を提供する。

【解決手段】 リングオシレータは、無線装置に内蔵され、複数段のインバータゲートからなる発振回路と、発振回路に接続された切り替えスイッチとを備える。発振回路が発生する高調波ノイズと無線装置の受信周波数とが干渉し、通信感度が低下する場合には、切り替えスイッチによりインバータゲートのリング状に接続される段数を切り替える。リングオシレータが発生する高調波ノイズの周波数を変えることで、無線装置の受信周波数との干渉を抑制する。

(もっと読む)

分周器

【課題】 動作周波数が高められた分周器を提供する。

【解決手段】 動作制御信号ENBが‘H’レベルに遷移し、クロック信号VCO,分周信号VCO_div2が‘L’レベル,‘H’レベルで停止した場合、3入力ナンドゲート14から出力された制御信号Aが‘L’レベルとなり、イクスクルーシブノアゲート10から出力されるトリガ信号VCO_delayが‘H’レベルとなる。トリガ信号VCO_delayはフリップフロップ11_1のトリガ端子Tに入力されており、フリップフロップ11_1から出力されている分周信号VCO_div2を‘H’レベルから‘L’レベルに遷移して、フリップフロップ11_1をリセット状態にする。

(もっと読む)

発振システム(oscillatorysystem)の周期タイミング・ジッタ(periodictimingjitter)の減少

【解決手段】PLL及びVCOを含む発振システムのようなノイズに敏感なアナログ回路について適応切替周波数回路を含む電圧調整器を含む装置が開示される。例において、装置は参照クロック発振器30、低ジッタ発振器170a、低ジッタ発振器について電源電圧WD_REGを調整するためにクロック信号入力を含む電源120、低ジッタ発振器出力周波数が安定している場合クロック検出器制御信号BOOST_CLK_SELを生成するクロック検出器、クロック検出器制御信号がアサートされた場合、低ジッタ発振器出力信号の周期ジッタの影響を抑制するために、電源へのクロック信号CLK入力として、参照クロック発振器出力信号REF_CLK、及び低ジッタ発振器出力信号VCO_CLKのうち一つを選択するマルチプレクサ110を含む。他の例において、クロック検出器制御信号は低ジッタ発振器出力周波数が安定している場合、電源のクロック信号入力として低ジッタ発振器出力信号を選択するために、マルチプレクサを制御する。 (もっと読む)

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

デジタルクロック・データ復元機およびこれを適用したトランシーバー

本発明は、デジタルフィルタ回路(digital filter)とデジタル制御発振器(DCO;digitally controlled oscillator)を用いて回路全体をデジタル回路化したクロック・データ復元機に関するものであり、本発明に係るデジタル制御発振器は、複数個のインバータチェーンを備えており、それぞれのインバータに電源電流を供給する電源電圧とインバータの間に可変抵抗スイッチングマトリックスを構成して供給電源を変化させ、発振周波数をチューニングする。

ここで、可変抵抗スイッチングマトリックスは、PMOSトランジスタ配列を用いて具現化するものの、低いレベルでの周波数チューニングステップと高いレベルでの周波数チューニングステップを互いに均等化するために、スイッチングマトリックスの列と列の間に垂直抵抗を追加挿入している。また、ジッタ発生問題を解消するために、第1シグマデルタモジュレータを用いてディザリング回路を具現化しており、セグメントサーモメーター方式を適用して少ない個数のルーティングラインでデジタル制御発振器をチューニングしている。  (もっと読む)

(もっと読む)

81 - 100 / 213

[ Back to top ]