Fターム[5J106AA05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412) | デジタルPLL (213)

Fターム[5J106AA05]に分類される特許

121 - 140 / 213

時間デジタル変換器を有する回路および位相測定方法

時間デジタル変換器のフィード回路(20)を、通常動作モードまたは調整モードの間で切り替えることにより、時間デジタル変換のための調整データが得られる。遅延回路入力と、複数のタップとを有する遅延回路(22)は、遅延回路入力からの信号の、異なって遅延されたそれぞれのバージョンを出力する。サンプリングレジスタ(24)は、タップに結合されたデータ入力を有し、クロック入力におけるアクティブ遷移に応じて、データ入力からデータをサンプリングする。通常動作モードでは、フィード回路(20)は、発振回路(10)の発振信号を、遅延回路入力に供給し、基準信号を、サンプリングレジスタ(24)のクロック入力に供給する。調整モードでは、フィード回路(20)は、発振信号によってタイミングが制御された遷移を有する信号を、遅延回路入力とクロック入力の両方に供給する。フィード回路(20)は、遅延回路入力での遷移の後に、クロック回路における第1のアクティブ遷移のタイミングを制御する、発振信号の遷移の選択を提供する。制御回路(28)は、フィード回路を通常動作モードと調整モードの間で切り替え、調整モードにおいて、複数の異なる遷移を選択して第1のアクティブ遷移のタイミングを制御するよう、フィード回路(20)を連続して制御する。制御回路は、結果として生じるデータを、各選択についてサンプリングレジスタ(24)から読み出し、前記データから、発振信号に対する調整データを決定する。  (もっと読む)

(もっと読む)

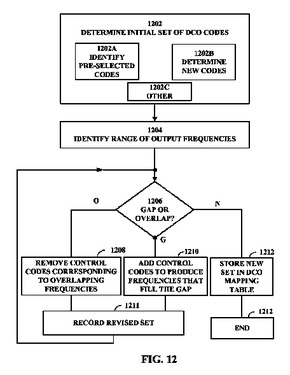

デジタル制御発振器のためのダイナミック較正技法

デジタル制御発振器(DCO)を較正するための技法を開示する。本開示の一態様では、DCOを動作させるための制御コードの初期セットを判断する。初期セットから生成された出力周波数レンジを識別する。周波数レンジにおけるギャップまたはオーバーラップインスタンスを識別する。オーバーラップの場合、修正されたセットを確立するためにオーバーラップインスタンスに対応する制御コードを初期セットから除去する。ギャップの場合、ギャップを充填する周波数値を生成するために、制御コードを初期セットに追加する。同じことを実行するための装置も開示する。  (もっと読む)

(もっと読む)

タイミング回復のためのサイクルスリップ検出

【課題】タイミング回復のためのサイクルスリップ検出の提供。

【解決手段】タイミング回復のために制御ループ中のループフィルタLFの出力信号を使用するステップと、前記フィルタ処理後のタイミング誤差信号から平均タイミング誤差値を生成するステップと、第1の閾値を超えるサンプルの隣接するブロックの平均タイミング誤差値の変化を累積するステップとを含む。第2の閾値を超える隣接するブロックの累積した平均タイミング誤差変化がサイクルスリップとして表明され、サイクルスリップの数が許容閾値である第3の閾値によって決定される。さらに、先入れ先出しメモリFIFOがサンプル挿入または削除のために設けられ、それは、サンプル挿入またはサンプル削除が向上した信頼性を伴ってサンプル領域で行われ、サイクルスリップ検出の改善された方法が雑音および不適切に選ばれたタイミングループパラメータに対する頑健性の増強のために推奨される。

(もっと読む)

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

デジタル位相ロックループ(DPLL)における電力消費を制御するシステム及び方法

【解決手段】相異なる周波数クロックの組から選択された参照クロックを生成するように適合されたプログラマブル周波数デバイスを備えた装置であって、プログラマブル周波数デバイスは更に、相異なる周波数クロック間での切り替えの際に、参照クロックのトリガエッジの同じ時間的関係を維持するように適合される。装置は更に、入力信号と出力信号との間の所定の位相関係を確立するために選択された参照クロックを使用する、デジタルPLL(DPLL)のような位相ロックループを備える。相異なる周波数クロック間の切り替えの際に参照信号の同じ時間的関係を実質的に維持することで、参照クロックが変化しても、位相ロックループ(PLL)の連続且つ有効な動作は、大きくはディスターブされない。これは、装置の電力消費を制御するために使用され得る。 (もっと読む)

張り出し無線装置、信号伝送速度の判別方法及び判別プログラム

【課題】変復調装置からベースバンド信号の伝送を受けて張り出し無線装置が動作する信号伝送系における信号の伝送速度を判別する。

【解決手段】変復調装置からベースバンド信号の伝送を受けて動作する張り出し無線装置であって、前記ベースバンド信号を基にしてパラレル信号およびクロック信号を生成するインタフェース部と、前記インタフェース部が生成する前記クロック信号と比較するための規定値の異なる信号を順次出力する制御部と、前記インタフェース部が生成する前記クロック信号と、前記制御部が出力する規定値の信号とが一致するか否かを検出し、前記両信号が一致した際に一致信号を出力するクロック回路とを有する。

(もっと読む)

ディジタル位相同期ループ(DPLL)の時間対ディジタル変換器(TDC)のパワーオンゲーティング窓を較正するためのシステム及び方法

ディジタル位相同期ループ(DPLL)の時間対ディジタル変換器(TDC)のパワーオンゲーティング窓を較正するのに関係するシステム及び方法が開示される。ゲーティング窓は同時に電力の効率的方法でTDCを動作させながらDPLLの適切な動作を保証するために較正される。特に、その技術はTDCゲーティング窓の幅を既定値に設定すること;制御ループが実質的にロックされるまで、DPLLを動作させること;DPLLの位相誤差デバイスによって生成される位相誤差信号をモニターしながら、TDCゲーティング窓の幅を所定の量だけ減少させること;位相誤差が所定の閾値に実質的に到達するか、或いは横切るときにTDCゲーティング窓の現在の幅を決定すること;及びTDCゲーティング窓の動作幅の誤差のマージンに組込む所定の量だけTDCゲーティング窓の現在の幅を増加させることを要する。  (もっと読む)

(もっと読む)

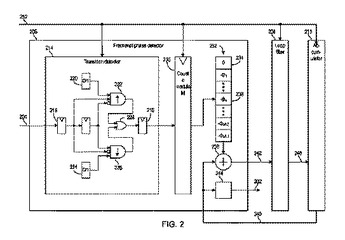

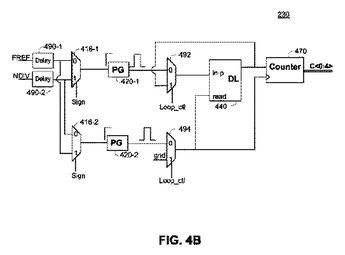

完全デジタル位相ロックループにおける位相デジタル変換器

位相デジタル変換器と、完全デジタル位相ロックループと、完全デジタル位相ロックループを有する装置とについて、本明細書で説明する。位相デジタル変換器は、時間デジタル変換器を駆動する位相周波数変換器を含む。時間デジタル変換器は、位相周波数変換器によって出力された位相差の絶対値と符号とを判断する。時間デジタル変換器は、タップ付き遅延線とループフィードバックカウンタとを利用して、ループ追跡プロセスによくある小さいタイミング差およびループ収集プロセスによくある大きいタイミング差の測定を可能にする。タップ付き遅延線は、基準期間の部分の測定を可能にし、基準クロックの速度に関する要件を低減することによって位相デジタル変換器のより低電力の動作を可能にする。  (もっと読む)

(もっと読む)

遅延同期ループ回路および表示装置

【課題】所望の単位遅延回路の1個分の遅延追加がなされた場合であっても不安定な単位遅延回路が連続しないようにすること。

【解決手段】本発明は、外部クロックと内部クロックとの位相差を比較する位相比較器1と、位相比較器1からの出力信号により遅延時間を制御するアップダウンカウンタ2と、外部クロックの遅延を制御して内部クロックとするため、アップダウンカウンタ2から出力される信号の複数ビットに対応した複数個の単位遅延回路(Delay-Cell)を備え、この複数個のDelay-Cellを直列に接続するにあたり、アップダウンカウンタ2からの出力における同一ビットの出力により制御されるDelay-Cellが隣り合わないよう接続されるデジタル遅延ライン3とを有する遅延同期ループ回路である。

(もっと読む)

信号再生回路

【課題】受信マージンを拡大可能な信号再生回路を提供する。

【解決手段】例えば、クロック信号CLKa,CLKb,CLKcを生成するクロック生成部CLK_GENと、CLKaとCLKbの間、又はCLKbとCLKcの間にデータ信号Diのエッジが入り込んだ際に、位相検出信号(EARLY,LATE)を生成するクロック・データ判定部CD_JGEと、ウインドウ幅制御部WW_CTL等を設ける。CLK_GENは、この位相検出信号に基づいて、前述したDiのエッジが入り込まないように、CLKa,CLKb,CLKcの全体位相を互いの位相差を保ったままで制御すると共に、WW_CTLからの信号(Sww)に基づいて、CLKaとCLKbの位相差、およびCLKbとCLKcの位相差を制御する。

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

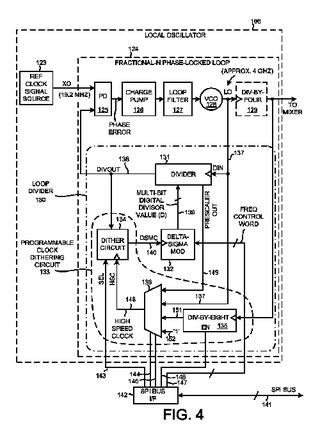

フラクショナルN位相同期回路におけるデルタ−シグマ変調器クロックディザリング

フラクショナル位相同期回路内のデルタ−シグマ変調器に供給されたクロック信号はディザ処理される。1つの例において、PLLは新しいクロックディザリング回路を含む。プログラマブルクロックディザリング回路は、いくつかの方法のうちの選択された1つで、クロック信号の位相をディザ処理するためにシリアルバスを経由して制御可能である。クロック信号が第1の方法(擬似ランダム位相ディザリング)でディザ処理される場合、デルタ−シグマ変調器によって生成されたディジタルノイズの電力は周波数帯域を通じて分散され、それによってノイズがその他の回路構成に干渉する度合を減少させる。クロック信号が第2の方法でディザ処理(ローテーショナル位相ディザリング)される場合、ディジタルノイズの電力が取り払われる周波数であり、それによってノイズがその他の回路構成に干渉する度合を減少させる。  (もっと読む)

(もっと読む)

通信用半導体集積回路

【課題】周波数変調及び位相変調の高精度化を図ることが可能な通信用半導体集積回路を提供する。

【解決手段】通信用半導体集積回路は、ループフィルタの出力に第1の係数を乗算したキャリア周波数制御値を出力する第1の乗算器と、変調周波数データに第2の係数を乗算した変調周波数制御値を出力する第2の乗算器と、キャリア周波数制御値と変調周波数制御値とを加算し、その加算結果として前記発振器制御値を出力する第4の演算器と、を備える。第2の係数Kmは、Km=Kc+A×Fmod/Frefの関係にある(Kc:第1の係数、A:補正項(実数)、Fmod:前記変調周波数、Fref:前記基準周波数)。

(もっと読む)

デジタルPLL回路

【課題】同期信号消失時の同期維持精度が向上されるとともに簡素な回路構成のデジタルPLL回路を提供することである。

【解決手段】同期信号の入力があるときの2つのクリアパルスの間に含まれる内部クロックの数の時系列的な平均値を学習値として記憶する学習値記憶回路と、PLLクロックカウンタのカウント値が学習値の整数成分と一致したとき一致検出パルスを生成する一致検出回路と、一致検出パルスを内部クロックの1周期分遅延して遅延パルスを生成するフリップフロップと、一致検出パルスまたは遅延パルスのいずれか一方を小数補正信号に従って選択し擬似同期パルスとして出力する擬似同期パルス選択回路と、補正区間において遅延パルスの数の擬似同期パルスの数に対する割合が学習値の小数成分に近似するよう選択する小数補正信号を出力する小数補正演算回路と、を有する。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

クロック発生回路

【課題】クロック発生回路において、コストの増大を回避すること。

【解決手段】ディジタル位相比較器1、ディジタルループフィルタ2、DDS3、バンドパスフィルタ4、増幅器5、OCXO6および第1分周器7は、ディジタルPLLを構成する。OCXO6から与えられるDDS3の動作周波数をfSとし、DDS3の出力設定周波数をfOとし、nを自然数とすると、DDS3からは、ディジタル/アナログ変換のイメージ成分として、[n×fS±fO]の周波数の信号が出力される。バンドパスフィルタ4は、このイメージ成分の周波数を通過帯域とする特性を有する。

(もっと読む)

クロック生成回路およびその使用方法

【課題】基準信号の周波数を逓倍又は分周したクロック信号を生成するクロック生成回路において、一つの基準信号から任意周波数のクロック信号を発生可能とする。

【解決手段】クロック生成回路1は、リング状に連結したm個の遅延素子DUからなるパルス遅延回路10と、各遅延素子DUから順次出力される通過信号P1〜Pmに基づき、基準信号CKIの周期を遅延素子DUでの遅延時間を単位として表した周期データDTを生成する周期測定部20と、除数又は乗数として使用される設定値MNを格納する設定値レジスタ50と、周期データDTに、設定値MNを乗・除してクロック信号の出力周期を表す制御データCDを生成する制御部30と、制御データCDと通過信号P1〜Pmとに基づき、基準信号CKIを分周又は逓倍したクロック信号CKOを出力する出力部40とを備え、実数で表された設定値MNを用いる。

(もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティ比特性を有するクロックを生成する。

【解決手段】本発明は、デュアルループタイプ(Dual Loop Type)のDLL回路であって、第1位相検知信号に応答し、第1遅延制御信号を生成して第1遅延ラインの遅延量を制御し、第1遅延量情報信号を出力する第1遅延制御手段と、第2位相検知信号に応答し、第2遅延制御信号を生成して第2遅延ラインの遅延量を制御し、第2遅延量情報信号を出力し、前記第1遅延制御信号と半周期情報信号に応答して前記第2遅延ラインの遅延量を再び制御する第2遅延制御手段と、前記第1遅延量情報信号と前記第2遅延量情報信号の入力を受け、基準クロックの半周期情報を抽出して前記半周期情報信号を生成する半周期検知手段と、前記第1遅延ラインの出力クロックと前記第2遅延ラインの出力クロックを組み合わせてデューティ比補正クロックを出力するデューティーサイクル補正手段とを含む。

(もっと読む)

小数部の入出力位相に基づいたデジタル位相同期ループ動作

1つの態様では、デジタルPLL(DPLL)は、入出力位相の小数部に基づいて動作する。DPLLは、入力位相を得るために少なくとも1つの入力信号を蓄積する。DPLLは、例えばタイムデジタルコンバータ(TDC)を使用して、発振器からの発振信号と参照信号との間の位相差に基づいて出力位相の小数部を決定する。DPLLは、入力位相の小数部および出力位相の小数部に基づいて位相エラーを決定する。その後、DPLLは、位相エラーに基づいて発振器のための制御信号を生成する。別の態様では、合成されたアキュムレータを含むDPLLは、参照信号に基づいて、発振信号サイクルの数のトラッキングを保持することにより粗い出力位相を決定する。 (もっと読む)

121 - 140 / 213

[ Back to top ]