Fターム[5J106AA05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 回路方式 (1,845) | 同期回路 (1,583) | PLL(位相同期ループ回路) (1,412) | デジタルPLL (213)

Fターム[5J106AA05]に分類される特許

61 - 80 / 213

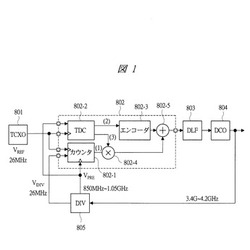

ADPLL、半導体装置及び携帯電話機

【課題】ノイズ等によって生じるチャタリングの発生を検知・訂正する機能をADPLLに提供する。

【解決手段】TDC802−2とカウンタ801−1を含むADPLLにおいて、TDCの出力(伝播遅延情報)をエンコードするエンコーダ802−3を用意する。エンコーダ802−3は複数のビットからなる伝播遅延情報を所定の単位に分けて、エンコーダ802−3内の16ビットエンコーダに個々の処理を行わせる。各16ビットエンコーダは、受け取った伝播遅延情報の一部の中に複数の変化点が存在する場合は、最下位ビットに近い変化点のみを残置させる。

(もっと読む)

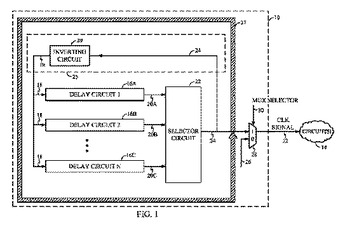

プログラマブルロジックデバイス回路に結合されるクロックデータリカバリ回路

【課題】プログラマブルロジックデバイス上またはこれと結合して設けられるクロックデータリカバリ回路の提供

【解決手段】プログラマブルロジックデバイス(“PLD”)が多数のCDRシグナリングプロトコルのうちの任意のものによって交信することを可能にするため、このPLDにプログラマブルクロックデータ復元(“CDR”)回路を装備する。CDR回路は、PLD内に内蔵するか、完全あるいは部分的に独立した集積回路とすることができる。この回路は、CDR入力、CDR出力、またはそれらの両方を行うことができる。CDR機能は、例えば非CDR低電圧作動シグナリング(“LVDS”)等のその他の非CDRシグナリング機能と組合わせて提供することができる。この回路は、大規模なシステムの一部とすることができる。

(もっと読む)

ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

【課題】階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

(もっと読む)

適応クロック発生器、システムおよび方法

機能回路のための、性能マージンを回避し、あるいは小さくするためのクロック信号を生成するために使用することができる適応クロック発生器、システムおよび関連する方法が開示される。特定の実施形態では、クロック発生器は、機能回路内の選択された遅延経路に関連する遅延回路に提供された遅延経路に従って、自律的に、かつ、適合的にクロック信号を生成する。クロック発生器には、入力信号を受け取るように適合され、かつ、出力信号を生成するために、受け取った入力信号を機能回路の遅延経路に関連する量だけ遅延させるように適合された遅延回路が含まれている。遅延回路には、上記出力信号に応答する帰還回路が結合されており、この帰還回路は、遅延回路に発振ループ構成で戻すための入力信号を生成するように適合されている。入力信号を使用して機能回路にクロック信号を提供することができる。  (もっと読む)

(もっと読む)

ADPLL回路、半導体装置及び携帯情報機器

【課題】ADPLL環境下またはADPLL環境に近い環境下において、ABSの精度向上手段を提供し、ABSの処理時間短縮を実現する。

【解決手段】ABS103中のデジタル周波数比較器103−1に、DPFD102の出力するDPE信号の初期位相差を格納するDFFを用意する。ABS動作開始直後に、DPFD102が出力するDPE信号はDPFD102の内部回路の初期位相差を表すものであるとしてDFFに記録する。以後デジタル周波数比較器103−1は入力されるDPE信号からDFFに記録された初期位相誤差を引いたものでABSを行い、高速かつ安定したABS動作の実現を図る。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

半導体記憶装置及び遅延時間制御方法

【課題】高速で遅延時間を行い、パフォーマンスを向上させる。

【解決手段】温度センサS1は、温度を検知し、温度情報として出力する。TAP保持回路S2は、予め使用される周波数と電圧状態とにおいて、使用温度範囲でDLL回路S4をロックさせ、その時々の温度センサS1により検知された温度に対応付けて、DLL回路S4のロック状態を初期遅延時間情報として保持する。実使用時には、DLL回路S4は、遅延時間制御開始時に温度センサS1により生成された温度に対する初期遅延時間情報をTAP保持回路S2から読み出し、そのロック情報に基づいて遅延時間を開始させる。

(もっと読む)

デジタルPLL回路とその制御方法

【課題】比較的簡易な回路構成で、制御時定数を短くしても超高安定な位相同期を実現する。

【解決手段】基準クロックを1/m分周器12で1/m倍し、VCXO11で発生される発振クロックを1/n分周器13で1/n倍し、両クロックを量子化位相比較器14に送り、両クロックのずれ量に相当する量子化位相差δを取得して予測制御器15に送る。予測制御器15では、入力された量子化位相差を、その極性が負から正に反転してから再び負に反転するまで、または正から負に反転してから再び正に反転するまで積分し、この積分値に-0.5倍〜-0.05倍の予測係数を掛けた値を予測重み値として求め、この予測重み値を積分値に加算して制御電圧値を予測する。この予測制御器15で予測された制御電圧値を、D/A変換器16でアナログ電圧に変換し、LPF17によって決まるループ時定数でフィルタリングして、周波数制御電圧としてVCXO11に送る。

(もっと読む)

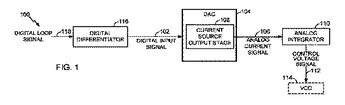

アナログ積分のためのデジタル補償を有するフェイズロックループ

フェイズロックループ(PLL)デバイスは、アナログ積分器によるアナログ電流信号の積分を少なくとも部分的に補償するために、デジタルループ信号を微分するように構成されたデジタル微分器を含む。デジタルアナログコンバータ(DAC)は、デジタル入力信号に基づいてアナログ電流信号を発生する電流源出力ステージを含む。アナログ積分器は、アナログ電流信号を積分して、電圧制御発振器(VCO)を制御するための電圧制御信号を発生する。  (もっと読む)

(もっと読む)

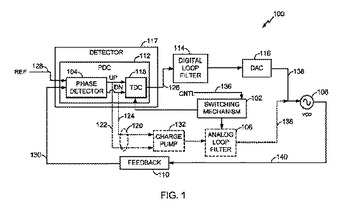

設定可能なデジタル−アナログ位相ロックループ

位相ロックループ(PLL)デバイスは、アナログ位相ロックループおよびハイブリッドアナログ−デジタル位相ロックループ内で構成可能である。アナログモードでは、少なくとも位相検出器、アナログループフィルタおよび電圧制御発振器(VCO)はアナログループを形成するために接続される。デジタルモードでは、少なくとも前記位相検出器、前記電圧制御発振器(VCO)、時間−デジタルコンバータ(TDC)、デジタルループフィルタおよびデジタル−アナログコンバータ(DAC)は前記ハイブリッドデジタル−アナログループを形成するために接続される。  (もっと読む)

(もっと読む)

デジタル位相同期回路

【課題】ホールドオーバ期間中の温度特性と経年変化に対する影響を抑え、周波数の高安定性を維持するホールドオーバ機能を有するデジタル位相同期回路を得る。

【解決手段】電圧制御型クロック発振手段の周辺の温度を測定する温度測定手段と、同期対象と同期している間、デジタルフィルタ手段からの出力で電圧制御型クロック発振手段を制御するとともにデジタルフィルタ手段からの出力と電圧制御型クロック発振手段の周辺の温度、経過時問の履歴から経過時間と電圧制御型クロック発振手段の周辺の温度と項に持つ2元多項式を求め、同期対象と同期していない間、同期対象に同期しなくなってからの経過時間および電圧制御型クロック発振手段の周辺の温度から2元多項式で電圧制御型クロック発振手段を制御する制御信号を推定するとともに推定した制御信号で電圧制御型クロック発振手段を制御するホールドオーバ手段と、を有する。

(もっと読む)

クロック生成回路及びこれを備える半導体装置並びにデータ処理システム

【課題】クロック生成回路の消費電力を低減する。

【解決手段】内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110を制御することによって内部クロック信号LCLKの位相を調整する位相制御部120と、位相制御部120の動作モードを切り替えるモード切り替え回路130とを備える。位相制御部120は、サンプリングクロック信号SYNCLK2に同期して内部クロック信号LCLKの位相を変化させる第1の動作モードと、内部クロック信号LCLKの位相を固定させる第2の動作モードを有しており、モード切り替え回路130は、リフレッシュ信号REFBなどのトリガ信号に応答して位相制御部120を第1の動作モードに遷移させ、内部クロック信号LCLKが所望の位相に達したことに応答して位相制御部120を第2の動作モードに遷移させる。

(もっと読む)

クロック生成回路及びこれを備える半導体装置並びにデータ処理システム

【課題】クロック生成回路において、カウンタ回路のスタックやロック動作の遅延を防止する。

【解決手段】位相判定信号PD0を生成する位相判定回路120と、位相判定信号PD0をサンプリングしこれに基づいて位相判定信号PD2を生成するサンプリング回路130と、位相判定信号PD2に基づいて内部クロック信号LCLKを生成するクロック生成部110とを備える。サンプリング回路130は、サンプリング周期内に位相判定信号PD0の論理レベルが変化した場合に位相判定信号PD2を固定する連続判定回路132と、位相判定信号PD1がハイレベルを示すまで位相判定信号PD2をハイレベルに固定する初期動作回路133と、位相判定信号PD1がハイレベルを示した後、連続判定回路132の動作を無効化する無効化回路134とを備える。

(もっと読む)

スペクトラム拡散クロック生成装置

【課題】生成されたスペクトラム拡散クロックを、各種タイミングを制御するカウンタのクロックとしても用いることのできるスペクトラム拡散クロック生成装置の提供。

【解決手段】SSC源クロック発生回路3,基準クロック発生回路5が発生するSSC源クロック,基準クロックは、16bitカウンタ7,9に入力されて、そのクロック数がカウンタ値cnt1,cnt2として計数される。カウンタ値cnt1,cnt2は、比較回路10に入力され、カウンタ値cnt1がカウンタ値cnt2よりも1以上大きくなると、比較回路10は比較結果cmpとしてLレベルの信号を出力する。すると、パルス生成回路21がLレベルの矩形パルス(間引き要求pls_cg)を出力し、AND回路31によりその間引き要求pls_cgとSSC源クロックとの論理積が計算されることによって、SSC源クロックが1クロック分間引かれる。

(もっと読む)

半導体装置及び位相検知回路

【課題】位相検知の誤判定を防止した高精度の位相検知回路を提供する。

【解決手段】電源線VSS1とセンスノードLSAT、LSAB間に、nMOSトランジスタの組(M1、M2、M3)、(M4、M5、M6)を備え、各トランジスタのゲートに内部クロックRCLK、RCLKのインバータINV1による反転信号、外部ロックCK、/CKをそれぞれ入力し、電源線VDD1とセンスノードLSAT、LSAB間に、pMOSトランジスタの組(MP1、MP2、MP3)、(MP4、MP5、MP6)を備え、各トランジスタのゲートにFCLKのインバータINV2による反転信号、内部クロックRCLK、外部ロックCK、/CKをそれぞれ入力し、センスノードLSAT、LSABは差動アンプAMPで増幅されラッチ回路L1でラッチされる。pMOSトランジスタ(MP11、MP12、MP13)はLSAT、LSABをプリチャージ・イコライズする。

(もっと読む)

デジタル制御発振器

【課題】TDCに関する冗長構成を削減可能なDCOを提供する。

【解決手段】DCOは、デジタル制御信号によって遅延量が制御される3以上の奇数個の単相インバータ101〜105を環状に接続したリングオシレータと、単相インバータの各々の出力信号をバッファリングし、第1の差動信号として夫々出力する奇数個のバッファ111〜115と、基準信号の立ち上がりエッジまたは立ち下がりエッジにおける第1の差動信号の値を保持して第2の差動信号として夫々出力する奇数個のフリップフロップ121〜125と、奇数個のフリップフロップから出力される奇数組の第2の差動信号を入力し、奇数組の第2の差動信号を位相の進み順に配列したときの、連続する高レベル値または連続する低レベル値の末尾を示す情報を出力するエッジ検出器130とを具備する。

(もっと読む)

クロック供給システム及び画像形成装置

【課題】SSCGの変調度を大きくすることなく、且つ低コストで、複数の電子部品から放射されるノイズを効果的に低減する。

【解決手段】一定周波数の第1クロック信号を生成する第1クロック生成器と、前記第1クロック信号の周波数変調を行うことで周期的に周波数が変動する第2クロック信号を生成する第2クロック生成器と、複数のクロック供給対象回路で使用される前記第2クロック信号の位相が、前記クロック供給対象回路毎に異なるように位相調整を行う位相調整回路とによってクロック供給システムを構成する。

(もっと読む)

タイミング・モジュールのホールドオーバのための内蔵自己検査のシステム及び方法

【課題】本発明の実施例は、局所発振器を有する装置において使用される方法を含む。

【解決手段】方法は、外部レファレンス信号によって統制される局所発振器について外部レファレンス信号にロックされている間に、外部レファレンス信号の関数であり、発振器におけるドリフトを統制するために使用される関数である補正信号に少なくとも部分的に基づいて数学的モデル毎の予測補正信号を求めるよう発振器の少なくとも2つの数学的モデルを訓練する工程を含む。方法は更に、外部レファレンス信号が利用可能でなく、発振器におけるドリフトを統制するために別の補正信号を使用する場合に最小の時間誤差を少なくとも2つの数学的モデルのうちの数学的モデルも含む。方法は、訓練に使用される期間に加えた検査持続時間の必要なしに、選択された数学的モデルを使用することが可能であるように、補正信号のサンプリングされたバージョンを使用して、選択された数学的モデルを検査する工程を更に含む。

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

発振器

【課題】 位相雑音特性を劣化させることなく可変周波数帯域の広帯域化を図ることができる発振器を提供する。

【解決手段】 可変周波数帯域の異なる複数の電圧制御発振器(15a、15b)と、複数の電圧制御発振器からの出力のいずれかを選択出力する切替器16と、パラメータに基づいて発振器出力が所定の周波数となるよう制御するデジタルPLL回路13とを備え、制御部18が、各電圧制御発振器に対応して、良好な位相雑音特性が得られるループゲイン及びダンピングファクタを記憶しておき、外部から周波数の値が入力されると、入力された周波数の値に応じて電圧制御発振器を選択し、当該電圧制御発振器からの出力を選択出力するよう切替器16を切り替え、当該電圧制御発振器に対応して記憶されているループゲイン及びダンピングファクタをパラメータとしてデジタルPLL回路13に設定する発振器としている。

(もっと読む)

61 - 80 / 213

[ Back to top ]