Fターム[5J106CC31]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数比較(弁別)回路 (250)

Fターム[5J106CC31]の下位に属するFターム

周波数電圧変換型 (9)

周波数数値変換型 (8)

基準信号と比較 (33)

複数の周波数比較(弁別)回路 (13)

Fターム[5J106CC31]に分類される特許

101 - 120 / 187

信号追跡を行う信号生成器

入力信号を追跡するように出力信号の周波数及び位相が調整される。前記出力信号が導き出される発振信号の周波数を制御するように制御信号が調整される。幾つかの側面においては、前記発振信号の前記周波数は、発振器回路に結合されたリアクティブ回路の再構成によって調整される。前記出力信号の位相は、前記発振信号と調整可能スレショルドの比較に基づいて調整することができる。例えば、前記調整可能スレショルドは、トランジスタ回路に関する調整可能バイアス信号を備えることができ、それにより、前記発振信号は、前記トランジスタ回路への入力として提供され、前記トランジスタ回路の前記出力は、前記出力信号を提供する。 (もっと読む)

信号分配装置

【課題】分周器の広帯域かつ低電圧動作を保障する。

【解決手段】信号分配装置は、第2制御信号に従って動作し、参照周波数に従って発振周波数を調整する調整部を有する位相同期ループ回路101と、電流源負荷を有し、前記調整部によって調整された発振周波数を分周してI/Q信号を生成する分周器102と、第1制御信号に従って自走発振周波数を生成する自走発振周波数生成器105と、前記参照周波数と前記自走発振周波数を比較する比較部103A及び前記比較部103Aの比較結果に従って前記第1制御信号又は前記第2制御信号を生成する制御部103Bを有する自走発振周波数制御回路103と、前記分周器102によって生成された前記I/Q信号を用いて送信又は受信を行う通信回路104と、を備えている。

(もっと読む)

デジタル制御発振回路、周波数シンセサイザ、それを用いた無線通信機器及びその制御方法

【課題】周波数が直線的に変化する範囲が広く且つ占有面積が小さいデジタル発振回路を実現できるようにする。

【解決手段】デジタル制御発振回路10は、複数の第1の可変容量素子からなる第1の容量素子群14及び複数の第2の可変容量素子からなる第2の容量素子群14を含む可変容量部12を有し、可変容量部12の容量値に対応した発振周波数の信号を生成する発振部を備えている。第1の可変容量素子の第1の容量変化量は、第2の可変容量素子の第2の容量変化量に2以上の整数値を乗じた値であり、第2の可変容量素子の個数は、2以上の整数値から1を減じた値以上である

(もっと読む)

搬送波同期回路および搬送波同期方法

【課題】局部発振器の周波数ドリフトが大きい場合、及び、周波数同期部の周波数検出精度があまり高くない場合においても、伝送品質を劣化させることなく、高速かつ安定的に搬送波との同期を確立する。

【解決手段】位相同期部52は、周波数同期部51による周波数同期処理後の残留周波数誤差Δf'を検出し、周波数同期部51に帰還させる。周波数同期部51は、収束判定回路82からの収束ステートを監視し、残留周波数誤差Δf'が収束したタイミングにおいて、位相同期部52からの残留周波数誤差Δf'に対する周波数引き込みを行う。本発明は、例えば、無線デジタル通信などの搬送波同期回路に適用できる。

(もっと読む)

CDR回路

【課題】異なる複数のビットレートの入力データを再生できるようにしたCDR回路を提供する。

【解決手段】参照クロックCKの周波数に対応した制御信号Vrにより第2の電圧制御発振器3の発振周波数が決定されるPLL回路と、制御信号Vrにより第2の電圧制御発振器3の発振周波数と同じ周波数で再生クロックCLK1を発振し且つ入力データのタイミングに合わせて該再生クロックCLK1の発振位相が調整される第1の電圧制御発振器1と、入力データを再生クロックCLK1によりリタイミングするフリップフロップ回路2とを備えるCDR回路において、PLL回路に、分周比の異なる2個の分周器7A,7Bと、該分周器7A,7Bの内の1つを選択するセレクタ8とを備えさせる。

(もっと読む)

PLL回路および再生装置

【課題】データ信号からクロックを復調する際に、周波数ロックがはずれることを防ぎ、再生装置の再生品質を高める。

【解決手段】PLL回路200は位相追従ループと周波数追従ループを備える。周波数追従ループは、周波数比較器202とローパスフィルタLPF225とを備える。周波数比較器202は、復調クロックCLKとデータ信号S1との周波数差を検出し、検出結果に応じた周波数誤差信号を出力する。LPF225は、周波数誤差信号に応じて充放電するコンデンサ226の充放電により周波数誤差信号を平滑して周波数制御電圧信号FVCを得る。第1の制御部240と第2の制御部250は、周波数ロック状態において、周波数比較器202からLPF225への出力が遮断されるオフ期間と遮断されないオン期間が交互に繰り返されるように制御し、オフ期間においてリーク電流に起因するFVCの変動を補正する。

(もっと読む)

周波数シンセサイザ及びこれを用いた無線通信装置

【課題】インダクタの使用による面積増大や、製造ばらつきによる歩留まり低下を防ぎつつ、動作周波数範囲を拡大する。

【解決手段】制御電圧によって制御される周波数で発振して発振信号を出力する電圧制御発振器106と;発振信号を分周して第1の分周信号を出力する、自走周波数が制御可能なプリスケーラ107と;第1の分周信号を分周して第2の分周信号を出力するプログラマブル・ディバイダ102と;第2の分周信号の位相と基準クロック信号の位相を比較して位相差に対応する信号を出力する位相比較器108を含み、位相差に対応して制御電圧を生成する制御電圧生成部と;第2の分周信号の周波数と基準クロック信号の周波数を比較して周波数差に対応した信号を出力する周波数比較器103と;周波数差に対応した信号に従って周波数差を最小化するように自走周波数を制御する制御部109と;を具備する。

(もっと読む)

位相調整回路および位相調整方法

【課題】 VCOの出力に生じている周波数変動を動的に補正し、これによりロングタームジッタを削減することが可能な位相調整回路の提供。

【解決手段】 周波数比較部12において、基準クロックRIN1の分周クロックREF1の周波数とフィードバッククロックFIN1の分周クロックFB1の周波数を測定および比較し、位相調整部13において、周波数比較部12の比較結果により、FB1の周波数がREF1より高ければカウンタ13−1をカウントアップして可変遅延回路13−2の遅延量を増やし、FB1の周波数がREF1より低ければカウンタ13−1をカウントダウンして可変遅延回路13−2の遅延量を減らす。

(もっと読む)

システムクロック供給装置及び基準発振器の周波数ずれ判定方法

【課題】システムクロック供給装置及び基準発振器の周波数ずれ判定方法に関し、装置内の基準発振器自身の周波数ずれを、測定用の発振器を用いずに判定し、周波数異常箇所を特定し、異常周波数クロックの送出を防ぐ。

【解決手段】二重化構成(N系及びE系)のシステムクロック供給装置内にそれぞれ備えられたOCXO等の基準発振器(#N,#E)9−1の出力クロックと、システム同期用に通常入力されるリファレンスクロック(例えば8KHz)とを、周波数ずれ測定部(#N,#E)1−1でそれぞれ比較し、所定回数の周波数ずれの発生を誤検出保護回路(#N,#E)1−2で測定し、該両系の測定結果を基に異常個所判定部(#N,#E)1−3で、自系若しくは他系の基準発振器(#N,#E)9−1の出力クロックの周波数ずれ又はリファレンスクロックの異常を判定して異常箇所を特定し、異常箇所を他系に切り替えるよう選択信号を送出する。

(もっと読む)

光ディスク装置、クロック生成装置、およびクロック生成方法

【課題】設定発振周波数範囲を自律して切り換える。

【解決手段】光ディスク装置1は、動作クロックの制御値に応じて動作クロックの発振周波数を調節可能であり、制御値の変更により調節可能な発振周波数の範囲を、段階的に異なる複数の設定発振周波数範囲のいずれか1つに切り換え可能である発振器20と、設定発振周波数範囲について、制御値の上限値、当該上限値に対応する制御値の初期値、制御値の下限値、および当該下限値に対応する制御値の初期値が設定されており、制御値が上限値に達した時に一段階上の設定発振周波数範囲に切り換えると共に制御値を当該上限値に対応する初期値に設定し、制御値が下限値に達した時に一段階下の設定発振周波数範囲に切り換えると共に制御値を当該下限値に対応する初期値に設定する発振周波数範囲切り換え回路30と、を有するクロック生成機能を備える。

(もっと読む)

ルビジウム原子発振器

【課題】スイープ電圧発生のための回路規模を小型化し、且つ非ロック時における周波数引き込み動作を自動的に行なうことが可能なルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器100は、OMU1と、増幅器2と、出力信号をデジタル信号に変換するA/D変換器3と、ロック状態又は非ロック状態を判定する状態判定部11と、位相変調信号fmの周波数成分を選択的に出力するBPF13と、スイープ電圧データを生成するスイープ電圧データ生成手段12と、タイマ15と、第1のBPF13の出力信号又はスイープ電圧データ生成手段12の出力信号を選択するSW−A14と、アナログ信号に変換するD/A変換器5と、位相検波して周波数制御信号を生成する位相検波器6と、周波数制御信号を積分処理する積分回路7と、周波数制御信号に従い出力周波数が制御されるVCXO8と、を備えて構成されている。

(もっと読む)

ジッタ発生装置

【課題】ジッタをデジタル的に発生させることにより、ジッタに関する調整が可能でありジッタ非注入時の信号劣化が生じることを防止したジッタ発生装置を提供する。

【解決手段】本実施の形態におけるジッタ発生装置では、第2カウンタ5が出力する−1〜1の範囲内のランダムな整数値のカウンタ値を第1カウンタ2が出力するカウンタ値に加算して、波形メモリ3にアドレスとして入力し振幅データから波形を得ることにより、ジッタをデジタル的に発生させ、波形20に対して波形21,22の波形の間をランダムにゆらいだ、ジッタが注入された波形を得ることが可能となる。

(もっと読む)

位相同期回路および電子機器

【課題】位相同期回路において、発振回路の周波数変換ゲインのばらつきに起因する帯域やダンピングファクタのばらつきの発生を防止する。

【解決手段】ゲイン特性情報取得部107Aは、判定基準周波数f1,f2を使って、初期電流Iini と各周波数で発振させるための周波数制御電流Iosciとを合成して電流制御発振部101Aに供給しながら、実動時の電流制御発振部101Aの周波数変換ゲインKcco を規定する判定基準周波数f1,f2の各発振制御信号Iosci_1,Iosci_2の差の情報(Iout_2 )を測定し、そのデータを周波数比較結果保持部172_2に記憶しておく。位相同期動作時には、周波数比較結果保持部172_2に記憶しておいた周波数比較結果fcompのデータD(f2)に基づく制御電流Icpcnt を補正信号として使って、周波数変換ゲインKcco のばらつきが相殺されるように駆動部104Zを制御する。

(もっと読む)

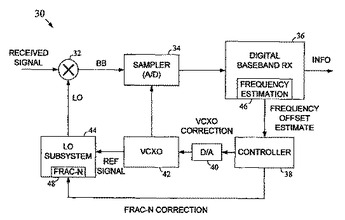

周波数修正を効率的に適用するための方法および装置

【課題】

電圧制御発振器によって駆動される分数分周方式シンセサイザを有する構造において、周波数精度を維持する。

【解決手段】

このために、最初に、分数分周方式シンセサイザを使用することで、大きな周波数誤差を修正する。つぎに、分数分周方式シンセサイザから電圧制御発振器へ、修正値を毎回少しずつ、ゆっくりと移動させる。  (もっと読む)

(もっと読む)

位相同期ループ回路及び信号発生装置

【課題】回路規模の大幅な増大を招かずに、早期に所望の周波数を有する信号を出力することができる位相同期ループ回路及び当該回路を備える信号発生装置を提供する。

【解決手段】位相同期ループ回路1は、PLL部10と、PLL部10から出力される信号S1の周波数をPLL部10の同調周波数帯域に高速に引き込むためのプリチューン信号S26を生成するプリチューン信号生成部20とを備えている。プリチューン信号生成部20は、PLL部10から出力される信号S1の周波数をカウントするカウンタ21、カウンタ21でカウントされた信号S1の周波数とプリチューン周波数との誤差を示す誤差値が所定の閾値よりも小であるか否かを判定する誤差判定部23、及び誤差判定部23の判定によって誤差値が所定の閾値よりも小となるときのPLL部10に与えられるプリチューン信号S26を記憶するメモリ25を備える。

(もっと読む)

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、第1、第2の信号(例えば、NCLK信号およびMCLK信号)の周波数が一致しているか否かを正しく判定できるようにした周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法を提供する。

【解決手段】NCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたUP信号を生成するエッジ検出回路111aと、MCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたDown信号を生成するエッジ検出回路111bと、UP信号及びDown信号をカウントし、そのカウント値をQ1、Q0信号で出力する2ビットアップダウンカウンタ112と、Q1、Q0信号に基づいて、NCLK信号の周波数とMCLK信号の周波数とが一致しているか否かを判定する判定回路113と、を有する。

(もっと読む)

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、NCLK信号およびMCLK信号等の周波数が一致しているか否かを正しく判定できるようにする。

【解決手段】NCLP信号の分周信号であるNCLP2信号と、MCLP信号の分周信号であるMCLP2信号とを生成する。次に、MCLP2信号がHレベルのときはNCLP信号をアップ信号としてカウントし、MCLP2信号がLレベルのときはNCLP信号をダウン信号としてカウントし、そのカウント値をQN1、QN0信号で出力する。また、NCLP2信号がHレベルのときはMCLP信号をアップ信号としてカウントし、NCLP2信号がLレベルのときはMCLP信号をダウン信号としてカウントし、そのカウント値をQM1、QM0信号で出力する。そして、QN1、QN0、QM1、QM0の各信号に基づいて、NCLP信号とMCLP信号の各周波数が一致しているか否かを判定する。

(もっと読む)

スペクトラム拡散クロック発生回路

【課題】入力される基準クロック信号に基づく変調波を生成するスペクトラム拡散クロック発生回路であって、回路の製造プロセス、電源、又は、温度等に起因する変調波の変動を低減するスペクトラム拡散クロック発生回路を提供すること。

【解決手段】出力信号を分周した分周出力信号を出力する分周器と、前記分周出力信号と受信した基準クロック信号との位相差を検出する位相比較器と、前記位相差に応じて充放電信号を発生するチャージポンプと、前記充放電信号に応じた差信号を発生するループフィルタと、前記差信号と変調波とが入力されて被変調波を生成する変調回路と、前記被変調波に応じた周波数のクロックを発生するクロック発生器とを有するスペクトラム拡散クロック発生回路であって、前記基準クロック信号に基づき前記変調波を生成する変調波生成回路を有するスペクトラム拡散クロック発生回路。

(もっと読む)

CDR回路

【課題】入力データに含まれているジッタを削除した再生データを得る。

【解決手段】入力データのデータレート周波数と同じ周波数の参照クロックを入力データにより位相合わせして再生クロックを作成し、該再生クロックにより前記入力データをFIFO101に書き込む。該FIFO101からの読み出しには、前記再生クロックと同期関係にない前記参照クロック又は別のクロックを使用し、前記FIFO101から再生データを出力させる。

(もっと読む)

電圧制御発振装置及びその制御方法

【課題】発振周波数の離散的な調整機能を設けた電圧制御発振装置の調整が簡単かつ正確にできるようにする。

【解決手段】調整データの入力で、電圧制御発振部の発振周波数の可変範囲を複数段階に調整可能な構成とする。また、制御電圧データに従い、調整用の制御電圧を可変で発生させる制御電圧生成部を備える。その上で、調整用の制御電圧を可変で生成させ、その可変生成された調整電圧で電圧制御発振部の発振を、設定可能な最大周波数と最小周波数とし、その最大周波数と最小周波数とを計測する。その計測結果から中心周波数を計算し、計算された中心周波数を用いて、電圧制御発振部の適正な調整用の制御電圧を設定し、その設定された制御電圧に固定して、調整データを可変させて適正な調整データを設定する処理を行う。

(もっと読む)

101 - 120 / 187

[ Back to top ]