Fターム[5J106CC31]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数比較(弁別)回路 (250)

Fターム[5J106CC31]の下位に属するFターム

周波数電圧変換型 (9)

周波数数値変換型 (8)

基準信号と比較 (33)

複数の周波数比較(弁別)回路 (13)

Fターム[5J106CC31]に分類される特許

81 - 100 / 187

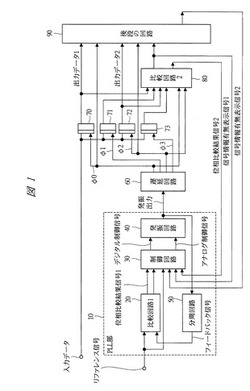

受信回路

【課題】入力データに位相を合わせたクロック信号を安定的かつ低消費電力で得る受信回路を提供する。

【解決手段】受信回路において、制御回路30、発振回路40、分周回路50、フリップフロップ回路、第1および第2の位相比較回路などを備え、発振回路40の発振周波数は、入力データに信号情報が有る時にはクロック信号と入力データの位相比較結果に基づいて制御し、入力データに信号情報が無い時にはクロック信号を分周して得たフィードバック信号と一定の周期で変化するリファレンス信号の位相比較結果に基づいて制御する。発振回路40は、2系統の制御信号によって発振周波数を制御でき、一方の系統の制御信号の変化に対しては徐々にかつ大きく発振周波数が変化し、他方の系統の制御信号の変化に対しては直ちにかつ小さく(少しだけ)発振周波数が変化するように構成する。

(もっと読む)

PLL回路

【課題】面積増大や消費電流増大を伴うことなくPLLロック時の位相オフセット量により生じるクロックの位相ばらつきを極力小さし、またロック後の温度や電源電圧変動へも対応できるようにする。

【解決手段】基準クロックCLK1と帰還クロックCLK2の位相を位相周波数比較器41で比較した結果に応じて出力クロックCLK3の周波数を決定するPLL回路において、出力クロックCLK3がクロックバッファ6を介して入力する分周回路5と分周回路5の出力クロックが入力し帰還クロックCLK2を出力する可変遅延回路9と、その帰還クロックCLK2の位相と基準クロックCLK1の位相を比較する位相比較器8とを備える。可変遅延回路9は、位相比較器8における基準クロックCLK1の位相と帰還クロックCLK2の位相の位相差がキャンセルされるようにその遅延量が制御され、結果としてPLL出力クロックCLK3の位相を調整できる。

(もっと読む)

PLL回路

【課題】消費電力と出力雑音の双方を抑えることができるPLL回路を得ることを目的とする。

【解決手段】PLL回路が、位相比較器1、チャージポンプ2、ループフィルタ3、電圧制御発振器4及び分周器5を備えており、CMOSロジック回路を用いて、分周器5を構成し、バイポーラトランジスタを搭載しているECL回路を用いて、位相比較器1及びチャージポンプ2を構成している。このようにPLL回路を構成することで、消費電力と出力雑音の双方を抑えることができる。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

受信側デバイスの出力クロック周波数の補正回路

データ(16)およびタイムスタンプ要素(18)を受信する受信側デバイス(13)の出力クロックの周波数を補正するための出力クロック補正回路(14)は、出力クロックフィードバックループ(20)、FIFOバッファ(22)およびタイムスタンプアジャスタ(24)を含む。出力クロックフィードバックループ(20)は、タイムスタンプ要素(18)に基づいて出力クロックの位相および/または周波数を調節する。FIFOバッファ(22)は、一時的にデータを格納する。タイムスタンプアジャスタ(24)は、FIFOバッファの状態に基づいてタイムスタンプ要素を選択的に調節する。一実施形態では、前記状態が、FIFOバッファ内の実データレベルに少なくとも部分的に基づくものとなる。別の実施形態では、FIFOバッファ(22)が目標データレベル範囲を有し、FIFOバッファ内の実データレベルがこの範囲外となったときに、タイムスタンプ要素が調節される。 (もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

PLL回路およびディスク再生装置

【課題】簡易な演算処理にて、適時かつ迅速に、周波数誤差を検出でき、これにより、サンプリングクロックの位相誤差を円滑に補正できるPLL回路を提供する。

【解決手段】再生信号の立ち上がり時に検出された位相誤差量が、遅延回路115と減算回路116に供給される。減算回路116は、供給された位相誤差量と一回前に供給された位相誤差量(遅延回路115からの出力)とを減算する。この減算結果をもとに、時間軸上における位相誤差量の傾き値Kp(周波数誤差)が傾き値算出回路117にて算出される。同様に、再生信号の立ち下がり時に検出された位相誤差量から傾き値Knが傾き値算出回路120にて算出される。制御回路121は、傾き値Kp,Knの何れかが閾値を超えると制御信号を出力する。セレクタ111は、制御信号が入力されると位相誤差量に替えてグランド信号をLPF112に供給する。

(もっと読む)

半導体集積回路装置および逓倍クロック生成方法

【課題】 エージング時に使用可能な同期逓倍クロック発生回路を提供することである。

【解決手段】 可変ディレイヤを用いた発振回路と、カウンタを用いた発振周波数制御回路とを有し、入力クロック周波数の逓倍の周波数のクロックを発生するクロック発生回路において、上記発振回路を入力クロックに同期させて動作させることで、入力クロックと同期した逓倍クロックを発生させる。

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】広帯域で量子化雑音及び発振器の位相雑音を除去し、小面積で構成可能な位相同期回路を提供する。

【解決手段】第1の制御信号及び第2の制御信号の組み合わせによって制御される共通の周波数及び互いに異なる位相を夫々持つ第1及び第2の発振信号を生成する制御発振器と;基準信号と第1の発振信号との間の周波数差及び位相差に応じた第1の検出信号を生成するデジタル位相周波数検出器と;第1の検出信号の高周波成分を除去して第1の制御信号を生成するデジタルフィルタと;第2の発振信号と基準信号との間の位相差に応じた第2の検出信号を生成するアナログ位相検出器と;第2の検出信号の高周波成分を除去して、第2の制御信号を出力するアナログフィルタと;アナログ位相検出器及びアナログフィルタを能動状態とするために、基準信号と第1の発振信号の同期を検出する同期検出部と;を具備する。

(もっと読む)

発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置

【課題】マイコン等の特別な制御回路が不要で、しかも無線送受信回路で使用する周波数に関係なく、スイッチングノイズの影響を無視できるレベルまでスイッチングノイズを軽減することができる発振周波数制御回路、その発振周波数制御回路を有するDC−DCコンバータ及び半導体装置を得る。

【解決手段】アップ/ダウン制御回路11は、第1クロック信号CLKAと第1分周クロック信号CLKB1との周波数を比較する第1周波数比較回路12と、第1クロック信号CLKAと第2分周クロック信号CLKB2との周波数を比較する第2周波数比較回路13の各出力信号UP及びDOWNに応じて、第2クロック信号CLKB2の周波数が所定の下限値から所定の上限値の間を連続的に変化しながら往復するように、発振回路2に対して、第2クロック信号CLKBの周波数制御を行うようにした。

(もっと読む)

デジタル位相ロックループを実施するためのシステム及び方法

【課題】デジタル位相ロックループを実施するシステム及び方法を提供する。

【解決手段】デジタル位相ロックループを実施する装置は、VCO制御電圧に応答して1次クロック信号を発生する電圧制御式発振器を含む。検出手段は、カウントアップ信号及びカウントダウン信号を含むカウンタ制御信号を発生し、1次クロック信号と基準信号の現在の関係を示す。アップ/ダウンカウンタは、次に対応するカウンタ制御信号に応答してカウンタ値を増分又は減分する。カウンタ値は、次に電圧制御式発振器により発生された1次クロック信号の周波数を調節するためにデジタル/アナログ変換器によってVCO制御電圧に変換される。代替実施形態では、上述のアップ/ダウンカウンタを利用して、デジタル/アナログ変換器でVCO制御電圧を発生する以外の適切な技術の利用により、カウンタ値に比例して電圧制御式発振器の周波数を調節することができる。

(もっと読む)

半導体集積回路

【課題】クロック信号生成部をディジタル制御するレジスタへの制御情報の格納ステップを削減すること。

【解決手段】半導体集積回路は、クロック信号CLKmを生成するディジタル制御信号生成部10、ディジタル制御部20を具備するクロック生成部を含む。クロック生成部は、位相周波数比較器31、制御レジスタ22を更に具備する。比較器31には、基準信号CLKinとフィードバック信号Moutが供給される。制御レジスタ22に比較器31の出力信号FDoutが供給され、制御レジスタ22は複数ビットのディジタル制御情報を格納する。クロック生成部は、複数のロック動作のための複数の初期設定データを予め格納する制御データ記憶回路25を更に具備する。動作選択情報Minに応答して制御データ記憶回路25から初期設定データSet1〜Set5が、制御レジスタ22の上位ビットに格納される。

(もっと読む)

周波数制御回路およびCDR回路

【課題】調整のための外部接続端子を必要とする部品や外部接続部品を必要とする部品を不要にする。

【解決手段】CDR回路は、周波数制御回路と、制御電圧に応じて発振周波数が制御されかつ入力データにより発振位相が制御される再生クロックを生成する第1のVCO2と、再生クロックによって入力データのデータ識別を行うFF1と、制御電圧に応じて発振周波数が制御される第2のVCO3とを備える。周波数制御回路は、第2のVCO3の出力信号の周波数を参照クロックの周波数と比較し、検出した周波数差に応じた信号を出力する周波数比較器4と、周波数比較器4の出力信号に応じて出力するデジタル値を上下させるアップダウンカウンタ5と、アップダウンカウンタ5の出力をアナログ信号に変換してVCO2,3の制御電圧として出力するD/A変換器6とから構成される。

(もっと読む)

原子共振器を使用した周波数発生のためのデバイス、システム、および方法

固体原子クロックは、周波数標準を生成するために、超微細共振を示すことが可能な量子状態を利用する可能性がある。出力信号を生成するために自由走行発振器を超微細共振周波数に結合することが可能なデバイスが本明細書で述べられる。本発明のある態様では、原子クロックは、シリコン基材上で作製されてもよく、また、電子集積回路の一部として、チップスケールで集積化されてもよい。固体原子クロックを利用した動作原理、作製方法、およびシステムもまた開示される。 (もっと読む)

DLL回路及びこれを用いた半導体装置、並びに、DLL回路の制御方法

【課題】チップ上における占有面積が小さく、広範囲なクロック周波数に対応可能なDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させるディレイライン210と、ディレイライン210による遅延量を制御する制御回路とを備える。ディレイライン210は、従属接続された複数の可変遅延素子500を有し、可変遅延素子500は、バイアス電流量によって遅延量が変化する差動回路構成であり、制御回路は、バイアス電流量を設定する第1の制御部300と、複数の可変遅延素子500のうち出力を取り出す可変遅延素子を選択する第2の制御部400とを有している。本発明によれば、可変遅延素子によってディレイラインが構成されていることから、少ない段数にて広範囲なクロック周波数に対応することが可能となる。

(もっと読む)

PLL回路

【課題】ハイブリッド制御方式PLL回路の定常状態における位相ジッタを低減する。

【解決手段】ハイブリッド制御方式PLL回路内の位相比較回路PHASE_COMPの出力S_PHが頻繁に変化しているか否かを判定する定常状態検出回路CONV_DETを設け、位相比較回路の出力S_PHが暫く変化していない時は定常状態に達していないと判定し、頻繁に変化している時は定常状態に達したと判定し、その判定結果に基づいて、電圧制御発振回路VCOの発振周波数をデジタル制御信号S_DGによって制御する制御幅を変更し、もしくは(および)、アナログ制御信号S_AGを変化させる頻度を変更する。これにより、定常状態に達する前の収束性を損なうことなく、定常状態に達した後のデジタル制御信号による発振周波数の制御幅を小さくできる。よって、定常状態における位相ジッタを低減できる。

(もっと読む)

注入同期型発振器

【課題】より小型化が可能な周波数逓倍器を提供する。

【解決手段】注入同期型発振器20は、インバータ(22a、22b、22c)を3段リング状に接続してリングオシレータを備えている。そして、2段目のインバータ22bの出力と、3段目のインバータ22cの出力とをnMOSトランジスタ24で接続する構成を採用している。このnMOSトランジスタ24のゲートは、外部から基準周波数信号が供給される。このような構成によって、、リングオシレータの自励発振周波数に近い周波数であって、注入された基準周波数信号と同期した整数倍の周波数で発振が行われる。このように、インジェクションロックを用いて、位相雑音を減らすことができるので、ループフィルタを必要とせず、より小面積で周波数逓倍器を構成することが可能である。

(もっと読む)

精密集積位相ロック回路用ループ・フィルタ

【課題】基準精密抵抗器と、第1のFETのゲートが第2のFETのゲートに結合されている第1のFETおよび第2のFETと、第1のFETに接続されコンデンサ電圧を発生させるフィルタ・コンデンサとを含む位相ロック・ループ回路内のループ・フィルタが提供される。

【解決手段】コンデンサ電圧は、第1のFETのソース、第2のFETのソース、および仮想グラウンドとして機能する基準精密抵抗器の底部に印加される。フィルタ・コンデンサによって生成されるコンデンサ電圧は、第2のFETが集積精密抵抗器の特性を含むように、第2のFETのバイアス点を設定する。第2のFETによって生成される所定の電圧は、第1のFETのゲートに印加されて、第1のFETが集積精密抵抗器の特性を含むように、第1のFETのバイアス点を設定する。

(もっと読む)

マルチチャネル・データ検出システム用に構成された周波数エラー組み合わせ論理および周波数エラーを生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの周波数エラー組み合わせ論理を提供することにある。

【解決手段】 この周波数エラー組み合わせ論理は、各チャネルに関する周波数エラー情報を受信することと、受信周波数エラー情報を結合し、結合された位相エラーを生成し、各チャネルからの受信周波数エラー情報に重みを付けるように構成された組み合わせ論理と、結合された周波数エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された周波数エラー出力とを含む。

(もっと読む)

81 - 100 / 187

[ Back to top ]