Fターム[5J106CC31]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数比較(弁別)回路 (250)

Fターム[5J106CC31]の下位に属するFターム

周波数電圧変換型 (9)

周波数数値変換型 (8)

基準信号と比較 (33)

複数の周波数比較(弁別)回路 (13)

Fターム[5J106CC31]に分類される特許

41 - 60 / 187

CDR回路

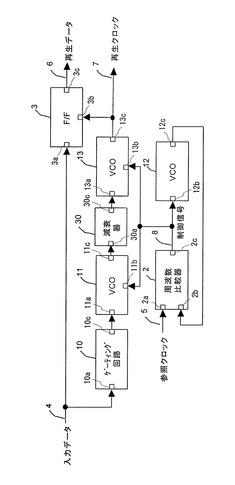

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

CDR回路

【課題】MACからの制御信号なしでも瞬時に入力データとの同期を確立し、周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するVCO11と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10とVCO11との間に設けられた、所望のデータレート周波数の信号を通過させるバンドパスフィルタ40とを備える。

(もっと読む)

同期信号生成装置、同期信号生成方法

【課題】ホールドオーバ状態からGPS通信衛星の電波を捕捉できる状態に復帰した場合、もしくはGPS通信衛星の電波を捕捉している状態からホールドオーバ状態に移行した場合、高精度の同期を迅速に行う同期信号生成装置、同期信号生成方法を提供することを課題としている。

【解決手段】同期信号生成装置1は、同期信号抽出部11と、制御部12と、同期部13と、DAC部(デジタル信号−アナログ信号変換部)14と、発振部15とを備えている。また、同期信号生成装置1には、GPS通信衛星アンテナ3と、基地局5とが接続されている。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

周波数−電流フィードバックを有する温度安定形発振回路

フェーズロックループや低周波温度安定形発振器を必要としない信号生成回路(600)および方法が開示される。この方法は、振動出力信号の周波数を制御するフィードバック信号(608)に応じて振動出力信号(CLK1〜CLKN)を生成することと、振動出力信号の周波数に対応する大きさを有する電流出力信号を生成することと、フィードバック信号を生成するために電流出力信号を基準信号(654)と比較することとを含んでよい。信号生成回路(600)は、フィードバック信号(608)に反応する発振回路(602)と、振動出力信号の周波数に対応する周波数依存性電流信号を生成する周波数−電流変換回路(620)とを含んでよい。発振回路へ向けてフィードバック信号(608)を生成するため、フィードバック変換回路(612)は出力信号を基準信号(654)と比較する。  (もっと読む)

(もっと読む)

クロックデータリカバリ回路、表示装置用データ転送装置及び表示装置用データ転送方法

【課題】回路規模、消費電力が小さく、EMI特性に優れるクロックデータリカバリ回路の提供。

【解決手段】2倍オーバーサンプリングにより、入力データをサンプリングするサンプリング回路SCと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの周波数差を検出する周波数検出回路FDと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの位相差を検出する位相検出回路PDと、少なくとも位相検出回路PDにより検出された位相差に基づいて、サンプリング回路SCに対し、リカバリクロックを出力する電圧制御発振回路VCOと、入力データとして表示データを受信している間、周波数検出回路FDの動作を停止する周波数検出制御回路FDCと、を備えるクロックデータリカバリ回路。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

クロック信号生成装置、電子装置、及び、PLL(PhaseLockedLoop)制御装置

【課題】所定のクロック信号の周波数を短時間で変更するとともに、クロック信号の周波数の変更時にクロック信号の供給先の動作が不安定になることを防止又は軽減するクロック信号生成装置等を提供する。

【解決手段】クロック信号生成装置等は、目標周波数が変更されると、第1制御部の代わりに、予め設定されている期間内に予め設定されている間隔かつ予め設定されている変更値で、クロック信号生成部に印加する電圧を順次変更し、クロック信号生成部が新たに生成するクロック信号の周波数を目標周波数に近づかせる第2制御部を備える。

(もっと読む)

バーストデータ再生装置

【課題】バーストデータからクロックを抽出してデータの再生を行うバーストデータ再生装置を得ること。

【解決手段】入力バーストデータ、ICLK、θCLKを入力し、入力バーストデータとICLKとの間の比較結果を出力する周波数位相比較部1と、入力バーストデータとICLKとの比較結果に基づいて準同期状態または非準同期状態を示す検出信号を出力する準同期状態検出部2と、比較結果を平滑化するループフィルタ部3と、準同期状態の場合は非準同期状態の場合よりも小さな利得でループフィルタ部3の出力信号を増幅する線形利得可変増幅部4と、線形利得可変増幅部4の出力信号に基づいてICLKおよびθCLKを生成する多位相型電圧制御発振部5と、入力バーストデータを遅延させる遅延調整部6と、遅延調整後の入力バーストデータとICLKに基づいてデータを再生する識別部7と、を備える。

(もっと読む)

PLL回路

【課題】低電圧動作が可能なPLL回路を提供する。

【解決手段】フィルタ用キャパシタの一端が入力される電圧制御発振器と、前記電圧制御発振器の出力が入力され、フィードバック信号を出力するn分周器と、基準信号と前記フィードバック信号との位相差に応じた電圧パルスを出力する位相周波数比較器と、前記電圧パルスに基づき、前記フィルタ用キャパシタを充放電するチャージポンプとを備え、前記チャージポンプは、前記フィルタ用キャパシタの一端に接続される充放電用容量を備える。

(もっと読む)

同期伝送装置及びジッタ抑圧方法

【課題】同期伝送装置及びジッタ抑圧方法に関し、入力クロックとシステムクロックの周波数偏差のゼロ交叉点付近で発生するピークジッタを抑圧する。

【解決手段】入力クロックを自装置内のシステムクロックでリタイミングした基準クロックを生成するディジタル回路15_1と、基準クロックに同期した出力クロックを生成するPLL回路15_2と、入力クロックの周波数偏差とシステムクロックの周波数偏差との接近を検出する周波数偏差接近検出部1_1と、該周波数偏差の接近が検出されたとき、該周波数偏差の差が増大するよう、システムクロックの発振器1_3の発振周波数を調整する周波数調整部1_2を備える。

(もっと読む)

送受信装置およびその動作方法

【課題】半導体チップ面積を低減して再生データと再生クロックの生成の誤動作の可能性を軽減する。

【解決手段】送受信装置7は、クロックデータリカバリ回路11、デシリアライザ15、シリアライザ14、PLL回路13、周波数検出器12を具備する。クロックデータリカバリ回路11は受信信号RXとPLL回路13から生成されるクロック信号TXCLKに応答して、再生クロックCLKと再生データDATAを抽出する。デシリアライザ15はCLKとDATAからパラレル受信データDTを生成し、シリアライザ14はパラレル送信データDRとTXCLKからシリアル送信信号TXを生成する。検出器12は受信信号RXとクロック信号TXCLKの周波数の差を検出して周波数制御信号FCSを生成して、信号FCSに応答して周波数の記差を低減するように、PLL回路13はTXCLKの周期を制御する。

(もっと読む)

遅延ロックループ回路、信号遅延方法

【課題】回路面積を大きくすることなく、遅延ロックループ回路を提供すること

【解決手段】逓倍PLL107は、基準クロックを逓倍して出力する。DLL211は、逓倍PLL107から出力されたクロックと、逓倍PLL107から出力されたクロックを遅延させたクロックと、を比較し、比較結果に基づいて所定の遅延量を持つ遅延信号を生成する。遅延制御信号演算回路108は、DLL211が生成した遅延信号に基づき、所望の遅延制御信号を生成する。第1の遅延回路102は、遅延制御信号演算回路108が生成した遅延制御信号に基づいて、入力信号を遅延させる。

(もっと読む)

受信部及び局側装置並びにクロック・データ再生回路における周波数校正方法

【課題】電圧制御型発振器を用いた受信部等において、温度補償用に容量素子を増やすことなく、温度変化による電圧制御型発振器の周波数特性を補償する。

【解決手段】本発明の受信部/局側装置は、受信信号からクロック信号及びデータ信号を再生するクロック・データ再生回路11を含むものであって、クロック・データ再生回路11に含まれる電圧制御型発振器17の発振周波数を校正する校正器16と、信号受信のスケジュールを管理する機能を有し、クロック信号及びデータ信号を再生すべき受信信号(上り信号)が無い状態の持続時間が校正器16による校正の所要時間を満たす時を選んで校正器16に対してリセット信号(校正指令信号)を出力する管理部104とを備えたものである。

(もっと読む)

OFDMAシステムのための2重周波数追跡ループ

無線デバイスによって受信された信号の搬送周波数とこのデバイスにとってローカルな基準信号との間の周波数誤差を修正するための方法および装置。ある幾つかの態様ではこのような方法は一般に、基準周波数を生成するLOと無線周波数(RF)位相ロックループ(PLL)とディジタルローテータとを有する受信機において信号を受信することと、上記受信された信号の搬送周波数と上記LO基準周波数との間の周波数差を推定することと、上記推定された周波数差を上記RF PLLと上記ディジタルローテータとに適用することと、を含む。  (もっと読む)

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、低ジッタで大きな電源電圧・温度変動耐性を実現する。

【解決手段】第1の発振回路および第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第2の発振回路および第1の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Ca,Cbを入力する端子を備え、第1〜第2の発振回路はそれぞれ2つの制御端子を備え、それぞれの一方の制御端子に周波数制御信号Aを入力し、第1の発振回路の他方の制御端子に回路間ばらつき調整信号Caを入力し、第2の発振回路の他方の制御端子に回路間ばらつき調整信号Cbを入力する構成。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】再生クロックを出力する第1の発振回路と、第1の発振回路と同一周波数のクロックを出力する第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Cを入力する端子と、周波数制御信号Aと回路間ばらつき調整信号Cを加算する加算器とを備え、第1〜第2の発振回路はそれぞれ1つの制御端子を備え、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に加算器の出力信号を入力する構成とする。

(もっと読む)

クロックデータ再生回路

【課題】プロセスばらつきによる発信周波数ずれを調整する。

【解決手段】入力データと周波数および位相が同期した再生クロックを出力する発振回路と、発振回路が出力する再生クロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、発振回路のプロセスばらつきによる発振周波数のずれを調整するプロセスばらつき調整信号Bを入力する端子を備え、発振回路は2つの制御端子を備え、その一方の制御端子に周波数制御信号Aを入力し、他方の制御端子にプロセスばらつき調整信号Bを入力する構成である。

(もっと読む)

41 - 60 / 187

[ Back to top ]