Fターム[5J106DD46]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611)

Fターム[5J106DD46]の下位に属するFターム

イクスクル−シブオア (92)

フリップフロップ (296)

Fターム[5J106DD46]に分類される特許

61 - 80 / 223

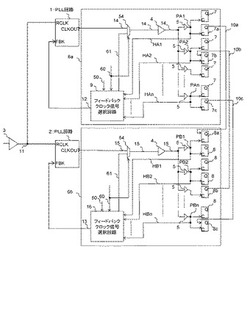

クロック分配回路およびクロック分配方法

【課題】クロック分配網間のクロックスキューをより低減する。

【解決手段】リファレンスクロック信号11の位相を調整してクロック分配網に分配するPLL回路1、2と、クロック分配網における複数のフィードバック点PA1〜PAn、PB1〜PBnからそれぞれフィードバッククロック信号HA1〜HAn、HB1〜HBnを入力し、PLL回路1、2でリファレンスクロック信号11の位相比較対象とされる複数のフィードバッククロック信号から一つの信号を、複数のフィードバッククロック信号のそれぞれの遅延値に基づいて選択するフィードバッククロック信号選択回路9、16と、を複数のクロック分配網のそれぞれに対応して備える。

(もっと読む)

集積回路、集積回路システム、シリアルパラレル変換装置およびスキュー調整方法

【課題】簡単な回路または簡単な処理によりスキュー調整する。

【解決手段】集積回路3は、入力された外クロック信号を遅延させた内クロック信号を出力するクロック遅延回路43と、入力されたデータ信号を内クロック信号によりラッチするラッチ回路45と、クロック遅延回路43に対して、外クロック信号に対する内クロック信号の遅延量として、複数の遅延量を設定する遅延量設定回路58と、複数の遅延量それぞれの設定の下でのラッチ回路45の出力信号を判定するラッチ判定回路52と、ラッチ判定回路52による複数の遅延量それぞれについての複数の判定値を記憶する記憶部53と、記憶部53に記憶された複数の判定値とクロック遅延回路43に設定した複数の遅延量との関係から、クロック遅延回路43による内クロック信号の遅延量を取得する遅延量取得部とを有する。

(もっと読む)

デジタルロック検出装置及びこれを含む周波数合成器

【課題】デジタルロック検出装置及びこれを含む周波数合成器を提供すること。

【解決手段】本発明の一側面は、複数の制御ビートの入力を受け、複数の制御ビートのロッキング(Locking)の可否を通報するビート信号を生成し出力する比較部と、ビート信号から複数の遅延信号を生成した後、複数の遅延信号とビート信号を結合して1つのクロック信号を出力する遅延セルブロックと、クロック信号の遷移時点を検出し、その検出結果を反映するロック表示信号を生成する検出部を含むデジタルロック検出装置及びこれを用いた周波数合成器を提供することができる。

(もっと読む)

PLL回路

【課題】高周波動作において、互いに容量が異なる複数のコンデンサの組み合わせを切り替えて電圧制御発振器の発振周波数帯域を切り替える際に、全ての発振周波数帯域同士を重なり合わせることが可能なPLL回路を提供することを目的とする。

【解決手段】互いに容量が異なる複数のコンデンサ51−1〜51−nの組み合わせを切り替えることにより発振周波数帯域を切り替える電圧制御発振器2を備えるPLL回路1において、電圧制御発振器2が高周波動作しているとき、容量が比較的大きなコンデンサ52−4又はコンデンサ52−5が選択されなくなる場合、補正用のコンデンサ5−1又はコンデンサ5−2を選択して電圧制御発振器2の全体の容量を大きくする。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

アキュムレータおよび位相デジタル変換器を使用する2ポイント変調のデジタル位相同期ループ

2ポイント変調をサポートするデジタル位相同期ループ(DPLL)が説明される。1つの設計において、DPLLは、位相デジタル変換器、ループ内で動作するループフィルタ、ローパス変調パスのための第1の処理ユニットおよびハイパス変調パスのための第2の処理ユニットを含む。第1の処理ユニットは、入力変調信号を受信し、位相デジタル変換器の後でループフィルタより前のループの内部の第1のポイントに対して第1の変調信号を供給する。第2の処理ユニットは、入力変調信号を受信し、ループフィルタより後のループの内部の第2のポイントに対して第2の変調信号を供給する。第1の処理ユニットは、周波数を位相に変換するために入力変調信号を累算するアキュムレータを含み得る。第2の処理ユニットは、可変利得で入力変調信号をスケールするスケーリングユニットを含み得る。 (もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、制御電圧によって遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40とを含む構成とし、切替制御回路40は、遅延段回路10における1つおきに且つ周回して順に並ぶ各インバーター回路に対応する接続切替回路を1つずつ選択し、選択した接続切替回路が、遅延信号を後段の回路に供給するように、その他の接続切替回路が遅延信号を後段の回路に供給しないようにする切替制御信号を生成し、これを各接続切替回路に供給する。

(もっと読む)

デジタル遅延線の時間遅延のプロセス、電圧、および温度のばらつき補正を行う装置と方法

【課題】プロセス、電圧、温度、補償回路、および連続的に遅延量を発生させる方法を提供する。

【解決手段】補償回路は2つの遅延線を含んでおり、各遅延線が遅延出力を供給する。2つの遅延線は、それぞれが多数の遅延エレメントを含み、その結果として1つ以上の電流枯渇型インバータを含む場合がある。遅延線の数は、2つの遅延線間で異なる場合がある。遅延出力は、2つの遅延出力に基づくオフセットパルスを決定した後、オフセットパルスの電圧を平均し、遅延量を決定する合成回路に供給される。遅延量は、1つ以上の電流または電圧となる場合があり、メモリバスドライバ、動的ランダムアクセスメモリ、同期DRAM、プロセッサ、あるいは他のクロック回路のようなアプリケーション回路の入力信号または出力信号に適用されるPVT補正量を示す。

(もっと読む)

放射線硬化チャージポンプ・トポロジ

【課題】シングル・イベント・アップセット(SEUs)により影響されにくいチャージポンプ回路を提供する。

【解決手段】第1のチャージポンプ出力を備えた第1のチャージポンプ30と、第2のチャージポンプ出力を備えた第2のチャージポンプ32と、前記第1のチャージポンプ出力及び前記第2のチャージポンプ出力を入力するように受け取り、第1の一致信号を出力するように生成する第1の一致検出器34と、第1の一致信号に基づいて、前記第1のチャージポンプ出力、または、前記第2のチャージポンプ出力のいずれかを選択するためのアナログ2:1マルチプレクサ36とを有する。

(もっと読む)

遅延固定ループ回路の遅延ライン部及び遅延固定ループ回路におけるクロック信号の遅延固定方法

【課題】レイアウトの大きさを増大させず、速やかに位相を固定させることができる遅延固定ループ及び遅延固定ループにおけるクロック遅延固定方法を提供すること。

【解決手段】遅延ライン部は、第1の遅延時間d1を各々有する複数の第1の単位遅延セルを有し、クロック信号clkを遅延する第1遅延ラインと、第2の遅延時間d2を各々有する複数の第2の単位遅延セルを有し、第1遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第2遅延ラインと、第3の遅延時間d3を各々有する複数の第3の単位遅延セルを有し、第2遅延ラインにおいて遅延固定動作が達成されない場合に、クロック信号clkを遅延する第3遅延ラインとを備え、第1の遅延時間d1が第2の遅延時間d2より短く、第2の遅延時間d2が第3の遅延時間d3より短い。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

対称性負荷遅延セル発振器(symmetricloaddelaycelloscillator)

【解決手段】発振器は、制御回路と、対称性負荷遅延セルのリングとを含む。各遅延セルは、2つの新規な対称性負荷を含む。各負荷は、レベルシフト回路と、電流ソース接続されたトランジスタと並列に結合されたダイオード接続されたトランジスタとを含む。制御回路は、発振器入力信号をバイアス制御信号に変換し、バイアス制御信号は、対称性負荷の実効的な抵抗を、遅延セルの遅延が入力信号の関数であるように制御する。制御回路は、発振遅延セル出力信号が一定の振幅を有するように遅延セルのレベルシフト回路を制御するため、制御ループの対称性負荷レプリカを用いる。第1の有利な側面では、この一定の振幅により、発振器は広い周波数レンジで動作可能である。第2の有利な側面では、発振器入力信号は出力信号発振周波数に対して、実質的に線形の関係を有する。 (もっと読む)

クロック制御回路及びこれを備える半導体装置

【課題】ノイズの影響でディレイラインが逆方向に調整されたり、ジッタ成分の影響でループに入ることのないDLL回路を提供する。

【解決手段】外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相判定回路140と、位相判定信号PD1に基づいて、サンプリング周期ごとにカウント値が更新されるカウンタ回路130と、カウント値に基づいて外部クロック信号CLKを遅延させることにより、内部クロック信号LCLKを生成するディレイライン110と、位相判定信号PD0が所定の論理レベルを示したことに応答して、同じサンプリング周期内におけるその後の位相判定信号PD0の変化を無効化した位相判定信号PD1を生成する無効化回路200とを備える。これにより、短い周期で位相判定信号に影響を与える成分を排除することが可能となる。

(もっと読む)

発振システム(oscillatorysystem)の周期タイミング・ジッタ(periodictimingjitter)の減少

【解決手段】PLL及びVCOを含む発振システムのようなノイズに敏感なアナログ回路について適応切替周波数回路を含む電圧調整器を含む装置が開示される。例において、装置は参照クロック発振器30、低ジッタ発振器170a、低ジッタ発振器について電源電圧WD_REGを調整するためにクロック信号入力を含む電源120、低ジッタ発振器出力周波数が安定している場合クロック検出器制御信号BOOST_CLK_SELを生成するクロック検出器、クロック検出器制御信号がアサートされた場合、低ジッタ発振器出力信号の周期ジッタの影響を抑制するために、電源へのクロック信号CLK入力として、参照クロック発振器出力信号REF_CLK、及び低ジッタ発振器出力信号VCO_CLKのうち一つを選択するマルチプレクサ110を含む。他の例において、クロック検出器制御信号は低ジッタ発振器出力周波数が安定している場合、電源のクロック信号入力として低ジッタ発振器出力信号を選択するために、マルチプレクサを制御する。 (もっと読む)

半導体装置

【課題】クロックの周波数が低くても、多大な時間を要することなく所望の位相遅延を可能にする半導体装置を提供する。

【解決手段】リファレンスクロックと第1のディレイラインで遅延させたリファレンスクロックとの位相比較結果に応じて第1のディレイラインでの遅延量を制御し、制御結果に基づいて第1のクロックを第2のディレイラインで遅延させ所定の位相差を有する制御クロックを生成する半導体装置にて、第1のディレイラインでの遅延量が設定可能な最大遅延量に応じた遅延量以上かつ最大遅延量未満の所定の閾値遅延量を超える場合には、セレクタによりリファレンスクロックとして出力するクロックを第1のクロックから定数倍の周波数を有する第2のクロックに切り替えるようにして、第1のクロックの周波数が低くても、多大な時間を要することなく所定の位相差を有する制御クロックを生成できるようにする。

(もっと読む)

デジタルフェーズロックドループ回路

【課題】従来のADPLL回路では、出力クロックにデューティ劣化がある場合、最終的に導き出される位相差に大きな誤差が生じてしまう。

【解決手段】第1クロックをカウントする第1カウンタと、第2クロックを分周した第3クロックをカウントする第2カウンタと、第3クロックの遅延クロックと第1クロックを比較した第1比較結果と、第1クロックの遅延クロックと第3クロックを比較した第2比較結果とに応じ第1、第3クロックの相対的位相差を検出する第1位相検出器と、第2クロックの周期を測定する第2位相検出器と、第2位相検出器の検出結果により第1位相検出器の検出結果を正規化した値と、第1、第2カウンタの値とに応じて第1、第3クロックとの位相差を演算する位相誤差演算部と、位相誤差演算部の演算結果に応じ第2クロックを出力するDCOとを有するデジタルPLL回路。

(もっと読む)

DLL回路及びこれを備える半導体装置、並びに、データ処理システム

【課題】短時間でロックさせることが可能なDLL回路を提供すること。

【解決手段】外部クロックCKと内部クロックLCLKの立ち上がりエッジの位相を比較する位相判定回路111と、外部クロックCKと内部クロックLCLKの立ち下がりエッジの位相を比較する位相判定回路112と、判定結果に基づいて内部クロックLCLKR,LCLKFのアクティブエッジの位置を調整する調整部120と、内部クロックLCLKR,LCLKFのアクティブエッジの調整方向とが互いに同方向であることに応答して内部クロックLCLKR,LCLKFの調整量の一方を他方よりも大きくする制御回路150とを備える。これにより、位相調整しながらデューティを50%に近づけることが可能となることから、DLL回路のロックに要する時間を短縮することが可能となる。

(もっと読む)

61 - 80 / 223

[ Back to top ]