Fターム[5J106DD46]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611)

Fターム[5J106DD46]の下位に属するFターム

イクスクル−シブオア (92)

フリップフロップ (296)

Fターム[5J106DD46]に分類される特許

101 - 120 / 223

半導体集積回路及びその制御方法

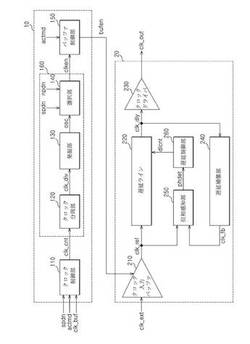

【課題】本発明は、安定ているクロックを生成するために、DLL回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供する。

【解決手段】本発明の半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するDLL制御手段;及び、バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するDLL回路を含む。

(もっと読む)

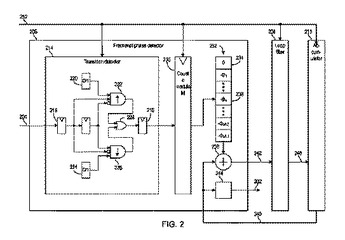

低電力無線周波数分周器

本開示によれば、高周波数で動作するように構成されたマルチモジュール分周器(MMD)回路は、入力クロック信号を分周してパルス信号を生成するカスケードの複数の2又は3分周セルを含む。MMD回路はまた、パルス信号の期間を伸張し、出力クロック信号を出力するパルスストレッチング回路を含む。カスケードの2又は3分周セル及びパルスストレッチング回路は、フルスイングの相補型金属酸化物半導体(CMOS)回路を用いてインプリメントされるかもしれない。各2又は3分周セルは、2又は3分周セルのクリティカルパスが、第1のダイナミックフリップフロップと、第2のダイナミックフリップフロップと、第1のダイナミックフリップフロップと第2のダイナミックフリップフロップとの間の2よりも多くないロジックステージとを備えるようにオーガナイズされている。  (もっと読む)

(もっと読む)

位相同期回路及びその制御方法、通信装置

【課題】

安定した周波数の出力信号を出力できるようにした位相同期回路及びその制御方法、通信装置を提供する。

【解決手段】

位相同期回路は、入力される制御電圧に応じた周波数の信号を出力信号として出力する電圧制御発振回路と、入力信号と電圧制御発振回路の出力信号との位相を比較する比較手段と、位相の比較に基づく電圧を異なるタイミングでそれぞれ保持する2つ以上のサンプル/ホールド回路と、2つ以上のサンプル/ホールド回路のいずれかを選択し、該選択したサンプル/ホールド回路からの出力を制御電圧として電圧制御発振回路に入力する切換手段と、入力信号の異常を検出する異常検出手段とを具備し、切換手段は、異常検出手段による異常の検出結果に基づいて2つ以上のサンプル/ホールド回路のいずれかの出力を選択する。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

位相検出装置、位相検出方法、再生装置及び再生方法

【課題】

記録媒体から再生される再生信号とクロック信号との位相差を正確に検出することが可能な位相検出装置、位相検出方法、該位相検出装置を備えた再生装置、再生方法を提供する。

【解決手段】

位相同期回路39がリミット位相ディテクタ41を備えるので、例えば図4に示すゼロクロスのタイミング(C)が検出されたとき(ST605でYES)、クロックカウンタ47によるカウント値と所定の値とを比較し(ST606)、カウント値が所定の値より小さいときに(ST606でNO)Cから次のクロックの立ち上がりまでの間、位相カウンタ51をイネブルでない状態とすることができる。つまり、リミット位相ディテクタ41(の位相カウンタ51)の出力を無効にすることができる。この結果、例えばノイズ等の影響を受け易い所定カウント値より小さいパルス幅のRF信号(入力信号)に基づき位相エラー信号が求められることを防止することができる。

(もっと読む)

分周器

【課題】専用の発振器を用いないボーレート発生器のように分周する周波数の誤差を許容する分周器を簡素な構成かつ高精度で実現する。

【解決手段】分周器としてのボーレート発生器1は、所定の基準クロックRCLKを分周することにより、データをサンプリングするボーレートクロックBCLKを生成する。このボーレート発生器1は、m進/m−1進ダウンカウンタ2と、カウンタ切替制御部3とを備える。m進/m−1進ダウンカウンタ2は、異なる分周比を切り替えて基準クロックRCLKを分周する。カウンタ切替制御部3は、記ボーレートクロックBCLKの正規のボーレートクロックに対する1周期毎の誤差の累積値が所定範囲を超えると、前記累積値が減少するように、m進/m−1進ダウンカウンタ2の分周比を切り替える。

(もっと読む)

適応ループ帯域を有する位相同期ループ

【課題】向上されたループ安定度とより早いロッキング率を有する適応的位相同期ループを含む半導体装置を公開する。

【解決手段】本発明の実施形態では、ループの安定度のために第2電荷ポンプを用いない方法として具現されていて、結果的に、本発明の位相同期ループはより小さいチップダイ(chip die)面積を占める。本発明の他の実施形態では、複数の電荷ポンプが用いられて、従来技術に比べてより向上されたロッキング(locking)応答時間を得ることができる。

(もっと読む)

位相同期ループ形周波数シンセサイザ

【課題】サイクルスリップの発生を防止して、短時間で周波数の切り換えを行うことができる位相同期ループ形周波数シンセサイザを得ることを目的とする。

【解決手段】 VCO4により発振される高周波信号Doの周波数が切り換えられる場合、位相比較器2が第1の位相比較信号Dnuと第2の位相比較信号Dndの差分を一定に保持するように構成する。これにより、サイクルスリップの発生を防止して、短時間で周波数の切り換えを行うことができる効果を奏する。

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

DLL回路、および半導体装置

【課題】DLLクロックが消失した場合に、位相検知における誤判定の結果を基に、遅延量が更新されることを回避し、ロック制御におけるDLLクロックサイクルの短縮化と、DLL回路の動作安定性の向上を図る。

【解決手段】本発明のDLL回路は、入力されるクロック信号の遅延量を制御する遅延信号を出力する遅延制御回路13と、この遅延信号に基づいた遅延量をクロック信号に付加し、DLLクロックとして出力する遅延回路12と、DLLクロック信号のクロッキング動作の有無を検知するDLLクロック検知回路31とを備える。そして、DLLクロック検知回路31は、DLLクロックのクロッキング動作が検知されない場合に、遅延制御回路13による遅延量の更新制御を停止させる。

(もっと読む)

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

位相比較器、位相同期回路及び位相比較制御方法

【課題】入力断検出部を位相比較器に内蔵することで位相比較器を実装するPLL回路の小型化を図る。

【解決手段】参照信号を入力すると共に、参照信号に基づく被参照信号を帰還入力し、これら入力した参照信号及び被参照信号の立ち上がりエッジを検出し、参照信号の立ち上がりエッジ及び被参照信号の立ち上がりエッジ間の位相差を検出する位相差検出部21と、位相差検出部21にて検出した位相差に基づき、位相差を小さくすべく、定電流出力動作を実行する定電流出力部24と、被参照信号のエッジを検出した後、参照信号のエッジを検出する前に、被参照信号のエッジを再度検出した場合、参照信号の入力断として検出する入力断検出部23とを有している。

(もっと読む)

デジタル位相ロックループ(DPLL)における電力消費を制御するシステム及び方法

【解決手段】相異なる周波数クロックの組から選択された参照クロックを生成するように適合されたプログラマブル周波数デバイスを備えた装置であって、プログラマブル周波数デバイスは更に、相異なる周波数クロック間での切り替えの際に、参照クロックのトリガエッジの同じ時間的関係を維持するように適合される。装置は更に、入力信号と出力信号との間の所定の位相関係を確立するために選択された参照クロックを使用する、デジタルPLL(DPLL)のような位相ロックループを備える。相異なる周波数クロック間の切り替えの際に参照信号の同じ時間的関係を実質的に維持することで、参照クロックが変化しても、位相ロックループ(PLL)の連続且つ有効な動作は、大きくはディスターブされない。これは、装置の電力消費を制御するために使用され得る。 (もっと読む)

デューティ検出回路およびCDR回路

【課題】入力データが交播パターン以外の場合であっても、高速かつ高精度にデューティを検出する。

【解決手段】デューティ検出回路は、入力データDinとこの入力データDinに周波数および位相が同期したクロックCKとを入力とし、入力データDinをクロックCKに同期してラッチして基準パルス幅を示すパルス信号Refを出力するフリップフロップ1と、入力データDinの平均電圧レベルとパルス信号Refの平均電圧レベルとの差を、入力データDinのデューティ100%からの変動分を示す検出信号Outとして出力する出力回路2とを備える。

(もっと読む)

信号再生回路

【課題】受信マージンを拡大可能な信号再生回路を提供する。

【解決手段】例えば、クロック信号CLKa,CLKb,CLKcを生成するクロック生成部CLK_GENと、CLKaとCLKbの間、又はCLKbとCLKcの間にデータ信号Diのエッジが入り込んだ際に、位相検出信号(EARLY,LATE)を生成するクロック・データ判定部CD_JGEと、ウインドウ幅制御部WW_CTL等を設ける。CLK_GENは、この位相検出信号に基づいて、前述したDiのエッジが入り込まないように、CLKa,CLKb,CLKcの全体位相を互いの位相差を保ったままで制御すると共に、WW_CTLからの信号(Sww)に基づいて、CLKaとCLKbの位相差、およびCLKbとCLKcの位相差を制御する。

(もっと読む)

高分解能の時間/デジタル変換器

【解決手段】時間/デジタル変換器(TDC)は、インバータの伝播遅延よりも優れた分解能を有し得る。一例では、非整数遅延素子回路は、TDC入力信号を受信し、そこから、第1信号の時間シフトした複製である第2信号を生成する。第1信号は、第1遅延線タイムスタンプ回路(DLTC)に供給され、第2信号は第2DLTCに供給される。第1DLTCは、TDCへの参照入力信号のエッジと第1信号のエッジとの間の時間を示す第1タイムスタンプを生成する。第2DLTCは、参照入力信号のエッジと第2信号のエッジとの間の時間を示す第2タイムスタンプを生成する。第1及び第2タイムスタンプは合成されて、共に高い分解能の全体のTDCタイムスタンプを構成する。これは、第1または第2タイムスタンプよりも優れた分解能を有する。 (もっと読む)

位相検出装置、位相比較装置およびクロック同期装置

【課題】クロック同期システムに用いる位相比較器として、次段のカウンタに影響を与えることなく、クロックの同期がとれた際に確実にロックをかけること。

【解決手段】本発明は、基準クロックの位相に対する比較クロックの位相のずれを検出する第1の位相比較部K1aと、基準クロックおよび比較クロックのいずれか一方について所定時間遅延または進んだ状態での両クロックの位相のずれを検出する第2の位相比較部K1bと、第1の位相比較部K1aの出力と第2の位相比較部K1bの出力との論理積を位相ずれの検出結果として出力する論理積部AND1とを備える

(もっと読む)

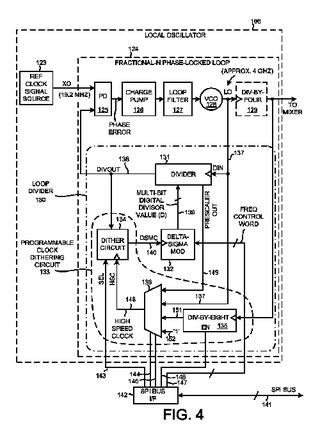

フラクショナルN位相同期回路におけるデルタ−シグマ変調器クロックディザリング

フラクショナル位相同期回路内のデルタ−シグマ変調器に供給されたクロック信号はディザ処理される。1つの例において、PLLは新しいクロックディザリング回路を含む。プログラマブルクロックディザリング回路は、いくつかの方法のうちの選択された1つで、クロック信号の位相をディザ処理するためにシリアルバスを経由して制御可能である。クロック信号が第1の方法(擬似ランダム位相ディザリング)でディザ処理される場合、デルタ−シグマ変調器によって生成されたディジタルノイズの電力は周波数帯域を通じて分散され、それによってノイズがその他の回路構成に干渉する度合を減少させる。クロック信号が第2の方法でディザ処理(ローテーショナル位相ディザリング)される場合、ディジタルノイズの電力が取り払われる周波数であり、それによってノイズがその他の回路構成に干渉する度合を減少させる。  (もっと読む)

(もっと読む)

位相同期回路及びこれを用いた受信機

【課題】広帯域で量子化雑音及び発振器の位相雑音を除去し、小面積で構成可能な位相同期回路を提供する。

【解決手段】第1の制御信号及び第2の制御信号の組み合わせによって制御される共通の周波数及び互いに異なる位相を夫々持つ第1及び第2の発振信号を生成する制御発振器と;基準信号と第1の発振信号との間の周波数差及び位相差に応じた第1の検出信号を生成するデジタル位相周波数検出器と;第1の検出信号の高周波成分を除去して第1の制御信号を生成するデジタルフィルタと;第2の発振信号と基準信号との間の位相差に応じた第2の検出信号を生成するアナログ位相検出器と;第2の検出信号の高周波成分を除去して、第2の制御信号を出力するアナログフィルタと;アナログ位相検出器及びアナログフィルタを能動状態とするために、基準信号と第1の発振信号の同期を検出する同期検出部と;を具備する。

(もっと読む)

パルス位相調整方法および装置

【課題】事前に位相ずれの評価や調整を行うことなく、フレームパルスとクロックとの間の位相変化を自動調整することができる。

【解決手段】位相制御部30により、位相調整部10での入力クロックCLKinに対する位相調整量を変化させて、レーシング検出部20により、このような危険なレーシング状態を検出し、位相制御部30により、その時の最悪位相調整量に基づいて、入力フレームパルスFPinを安定してラッチできる最適位相調整量を決定する。

(もっと読む)

101 - 120 / 223

[ Back to top ]