Fターム[5J106DD46]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | デジタル回路 (2,545) | 論理回路 (611)

Fターム[5J106DD46]の下位に属するFターム

イクスクル−シブオア (92)

フリップフロップ (296)

Fターム[5J106DD46]に分類される特許

41 - 60 / 223

デューティ補正回路、遅延同期ループ回路、カラムA/D変換器、固体撮像素子およびカメラシステム

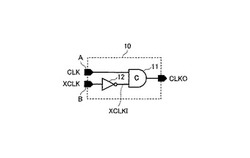

【課題】デューティ比が50%より大きい場合も小さい場合も両方を一つの素子で対応が可能であり、素子数を削減できるだけではなく、スイッチング回数を削減することが可能で、消費電流を削減することができるデューティ補正回路、DLL回路、カラムA/D変換器、固体撮像素子、およびカメラシステムを提供する。

【解決手段】デューティ補正回路10は、第1入力および第2入力を有するC素子11と、C素子11の第2入力に接続されたインバータ12と、を有し、C素子11は、入力が両方とも論理“1”になると出力が論理“1”になり、入力が両方とも論理“0”になると出力が論理“0”になり、その他の状態では出力は前の状態を保持し、C素子11の第1入力およびインバータ12にそれぞれ互いに位相差がほぼ半周期の相補クロックが入力される。

(もっと読む)

PLLロック検出回路、及びPLLロック検出回路を有するPLLシンセサイザ回路

【課題】適切にPLL回路ロックがなされているか否かを検出する。

【解決手段】PLL回路ロックがなされているか否かを検出するPLLロック検出回路を構築する。ここにおいて、そのPLLロック検出回路は、基準発振器から供給される基準発振周波数を示す基準発振周波数信号と、前記基準発振周波数を分周して得られたリファレンス周波数を示し位相比較器に供給されるリファレンス周波数信号と、VCOから供給される電圧制御発振周波数を分周して得られた比較周波数を示し前記位相比較器に供給される比較周波数信号とを受ける、そして、前記リファレンス周波数信号と前記比較周波数信号とに基づいて、前記PLL回路ロックを示すロック検出信号を出力する。

(もっと読む)

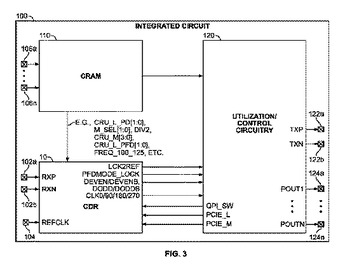

オートスピードネゴシエーションおよび他の可能な特徴を有するクロック・データ再生回路

集積回路(「IC」)は、入力データ信号からデータ情報を再生するためのクロック・データ再生(「CDR」)回路を含んでもよい。CDR回路は、参照クロックループと、データループとを含んでもよい。CDR回路によって出力される時刻変更(再生)データ信号は、その信号に含有される通信変更要求について、IC上の他の制御回路によって監視される。そのような要求に応答して、制御回路は、CDR回路の動作パラメータ(例えば、上述のループのうちのいずれか一方で使用される周波数分割ファクター)を変更することができる。これは、オートスピードネゴシエーションを採用するICサポート通信プロトコルに役立つことができる。  (もっと読む)

(もっと読む)

PLL発振回路

【課題】 アンロック状態を検査すると共に、自動的に再同期する自動リトライ機能を備えるPLL発振回路を提供する。

【解決手段】 MPU4は、外部基準信号とVCXO3からの出力信号の位相を比較してVCXO3への制御電圧を出力するPLL−IC1からのロック検出信号を入力し、ロック状態においてアンロック状態にするためのアンロックアラームテスト用データをPLL−IC1に設定し、PLL−IC1からのロック検出信号によりアンロック状態を判定すると、外部にアンロックアラーム出力信号を出力し、アンロック状態が第1の期間継続しているか否かを判定し、アンロック状態が第1の期間継続していれば、再同期を行わせるためのデータをPLL−IC1に設定するリトライを実行するPLL発振回路である。

(もっと読む)

ADPLL、半導体装置及び携帯電話機

【課題】ノイズ等によって生じるチャタリングの発生を検知・訂正する機能をADPLLに提供する。

【解決手段】TDC802−2とカウンタ801−1を含むADPLLにおいて、TDCの出力(伝播遅延情報)をエンコードするエンコーダ802−3を用意する。エンコーダ802−3は複数のビットからなる伝播遅延情報を所定の単位に分けて、エンコーダ802−3内の16ビットエンコーダに個々の処理を行わせる。各16ビットエンコーダは、受け取った伝播遅延情報の一部の中に複数の変化点が存在する場合は、最下位ビットに近い変化点のみを残置させる。

(もっと読む)

レジスタ制御ディレイロックループを備えた半導体デバイス

【課題】DLLクロックの無用なトグリングによる電流の消耗を低減することができるレジスタ制御ディレイロックループを備えた半導体デバイスを提供する。

【解決手段】レジスタ制御ディレイロックループから出力されたDLLクロックを用いる内部回路を備えた半導体デバイスにおいて、半導体デバイスに対する作動信号及び非作動信号に応答して、内部回路に印加されるDLLクロックをイネーブルしたりディスエーブルしたりするクロックイネーブル信号を生成する手段を備える。その場合、クロックイネーブル信号を生成する手段は、作動信号又は非作動信号に応答してプルダウン又はプルアップ動作を行う駆動手段と、半導体デバイスに対する作動信号に応答して駆動手段の出力ノードをリセットするリセット手段と、駆動手段の出力ノードに印加された信号をラッチし、バッファリングして出力する出力手段とを備えている。

(もっと読む)

ジッタ除去回路

【課題】従来では、基準クロック生成回路が生成するクロックにジッタが発生するという問題があった。

【解決手段】本発明にかかるジッタ除去回路は、基準クロック51のジッタを除去するジッタ除去回路であって、サンプリングクロック52に同期して基準クロック51のエッジを検出するラッチ回路12と、基準クロック51のエッジ間隔をカウントするカウンタ13と、各エッジ間隔のカウント数に基づいて基準クロック51の位相を調整する位相調整回路14と、を備える。

(もっと読む)

位相同期ループのジッタ検出方法及び装置

【課題】別途のジッタ計測装備を使用せずとも位相同期ループのジッタ水準を検出できる位相同期ループのジッタ検出方法及び装置を得る。

【解決手段】基準クロックとフィードバッククロックとの位相差信号を検出し、その位相差信号によって一定の周波数の発振信号を生成する位相同期ループと、入力遅延制御信号によって多数のキャパシタをスイッチングし、前記位相同期ループからの前記位相差信号を前記遅延制御信号によって遅延させる可変位相遅延部と、前記位相同期ループからの前記位相差信号と前記可変位相遅延部によって遅延された位相差信号とを比較し、前記位相差信号の遅延期間を検出する比較部と、前記比較部から検出された遅延期間以後にロック範囲内に位置することを検出するロック検出部とを備える。

(もっと読む)

PLL回路および通信装置

【課題】出力周波数を切り替えた際の追従性の悪化を抑止すること。

【解決手段】分周部2は、基準信号と出力信号との位相を同期させるための信号である帰還信号を所定の分周比に分周する。そして、位相比較部3は、出力信号を用いて基準信号および帰還信号の位相を比較することで、分周部2が分周した分周比の増減に追従して、出力信号を生成するための位相比較部出力のゲインが増減する。濾波部4は、位相比較部3によって生成されたアナログ信号を濾波する。出力信号発振部5は、濾波部4によって濾波されたアナログ信号に基づいて、出力信号を生成する。

(もっと読む)

クロック位相同期回路

【課題】基準クロックに位相同期したクロックを出力するクロック位相同期回路に関し、長期間安定化及び入力擾乱影響を緩和する。

【解決手段】リファレンス入力a位相に同期した電圧制御発振器1の出力信号dを得る為のクロック位相同期回路であって、リファレンス入力aの周波数と電圧制御発振器1の出力信号dの周波数とを一致させて位相比較器3により所定のタイミング毎に位相比較した位相差検出信号bを入力し、それを所定期間順次記憶するメモリ等の記憶手段と、所定期間毎の位相差検出信号の差を位相変動量として求め、位相変動量が許容範囲内の場合は、その位相変動量に対応した電圧制御発振器1の制御電圧に変換し、許容範囲内でない場合は、前回の位相変動量に対応した制御電圧又は自走状態となる制御電圧として、電圧制御発振器1に制御電圧cを入力する演算処理手段とを備えている。

(もっと読む)

内部コマンド生成回路

【課題】電流消耗を減少させることができる内部コマンド生成回路を提供する。

【解決手段】本発明の内部コマンド生成回路は、読出しまたは書込み動作のためのコマンドを受信して、所定の周期で発生する複数のパルスを含む第1バーストパルスを生成するバーストパルス発生部と、前記第1バーストパルスをシフトして内部コマンドを生成するパルスシフト部と、を含み、前記内部コマンドは、バースト終了信号またはバーストコマンドのパルスが入力されるとディセーブルされる。

(もっと読む)

信号多重化回路

【課題】データ信号とクロック信号との位相関係を適応的に制御できる信号多重化回路を提供する。

【解決手段】信号多重化回路は、第1のクロック信号の第1の位相位置に同期したデータ遷移をする第1のデータ信号と第1のクロック信号の第1の位相位置から180度位相がずれた第2の位相位置に同期したデータ遷移をする第2のデータ信号とを受け取り、第2のクロック信号に応じて第1及び第2のデータ信号を順次選択して出力するセレクタ回路と、第1及び第2のデータ信号と第1及び第2のクロック信号とに基づいて、第2のクロック信号とデータ遷移との位相関係を示す位相制御信号を出力する位相検出器と、位相制御信号に応じて位相関係を制御する位相制御器とを含む

(もっと読む)

モータ用位相同期回路及びそれを用いたスピンドルモータ

【課題】入力信号の周波数が変化するようなモータの駆動制御において、ステップ入力などのように入力信号の位相が急激に変化した場合でも、オーバーシュートやスリップによる振動などの過渡的な振動の発生を抑制することができる多重PLL回路の構成を得る。

【解決手段】第2PLL21の第2位相比較回路24によって検出される位相差が所定範囲外である場合には、ループ加算器26を介さずに、第1PLL11を用いて第2PLL21のモータ部22を制御する一方、上記位相差が所定範囲内である場合には、上記ループ加算器26を介して上記第1PLL11と上記第2PLL21とを接続して多重PLL回路を構成するように、信号経路切換部33によって、該第1及び第2PLL11,12の信号経路を切り換える。

(もっと読む)

遅延同期ループ回路

【課題】外部クロック信号が擾乱したとき、擬似ロックを検出し初期化したとき、電源を投入したとき、いずれの場合も確実にロックはずれを防止でき、レイアウトがコンパクトなDLL回路を提供する。

【解決手段】遅延同期ループ回路であって、入力クロックを、制御電圧の大きさに応じて遅延させて帰還クロックを出力する電圧制御遅延手段と、帰還クロックと基準クロックとを比較して位相差を検出し、該位相差に応じて、制御電圧を上昇させるための上昇信号と該制御電圧を下降させるための下降信号とを出力する位相比較器と、上昇信号と下降信号とに応じて制御電圧を決定し、電圧制御遅延手段に出力する制御電圧生成手段と、基準クロックと電圧制御遅延手段からの中間クロックとの論理和に基づき位相比較器をリセットする。

(もっと読む)

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

送信機および通信システム

【課題】周波数の変化に対応でき、且つクロストークに起因するジッターの低減を図ることができる送信機、および通信システムを提供する。

【解決手段】送信機2は、発振回路4と、送信部5とを備える。発振回路4は、基準クロックCKrefを入力して、同一の周期を有すると共に位相が互いに異なるN相(Nは2以上の整数)のクロックCK1〜CKNを生成して出力する。送信部5は、発振回路4から出力されたクロックCK1〜CKNを入力して、このクロックCKn(nは1以上N以下の各整数)にシリアルデータ信号Snを同期させて高速シリアル伝送線路Lnを介して受信機3に送信する。

(もっと読む)

半導体集積回路装置

【課題】プロセスモニタに必要な回路面積を増加させることなく、高精度なプロセスキャリブレーションを短時間で行う。

【解決手段】ディジタル制御発振器38が任意の発振バンドを選択した後、制御部25はTDC41の信号がプロセスモニタ制御部40に入力されるようにスイッチ44を切り換える。TDC41は、信号VREFの立ち上がりエッジと最も近い信号VPREの立ち上がりエッジの期間をディジタル値に、信号VREFの立ち上がりエッジと2番目に近い信号VPREの立ち上がりエッジの期間をディジタル値に変換し、その差を算出する。プロセスモニタ制御部40は、ルックアップテーブルを参照し、算出した値と予め設定されている期待値とを比較し、プロセス値を決定する。そのプロセス値は、プロセス信号として調整制御部26にそれぞれ出力され、プロセスキャリブレーションが行われる。

(もっと読む)

PLL回路

【課題】基準周波数信号がPLL回路に入力されなくなった場合に、チャージポンプ回路にループフィルタから電流が流れ続けることを防止する。

【解決手段】PLL回路1は、入力された電圧に応じた周波数のVCO信号を出力するVCO20と、入力された電流に応じた電圧をVCO20に与えるループフィルタ18と、第一入力信号と第二入力信号との位相差に応じた幅の位相差パルスを出力する位相比較器14と、位相差パルスを受けて、ループフィルタ18への電流入力を行うチャージポンプ回路16と、REF信号(基準周波数信号)が入力されていない無入力状態において、チャージポンプ回路16への位相差パルスの入力を停止させる位相差パルス停止部30とを備える。なお、第一入力信号は、REF信号自身又はそれを分周した信号であり、第二入力信号は、VCO信号自身又はそれを分周した信号である。

(もっと読む)

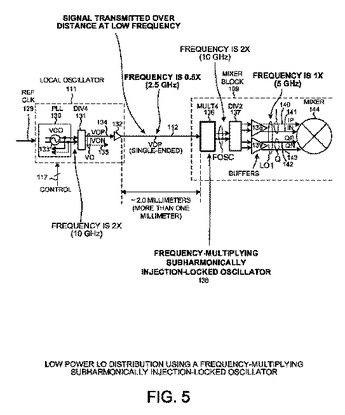

周波数逓倍サブハーモニック注入同期発振器を使用した低電力LO分配

局部発振器は、相対的に低い周波数の信号を、集積回路にわたりミキサの位置まで伝達する。ミキサの近くでは、周波数逓倍サブハーモニック注入同期発振器(SHILO)が、その信号を受信し、それからより高い周波数の信号を発生させる。SHILOがIおよびQ直交位相信号を出力する場合には、IおよびQ信号がミキサをドライブする。SHILOが直交位相信号を発生させない場合には、直交位相発生回路が、SHILO出力信号を受信し、それからミキサをドライブするIおよびQ信号を発生させる。1つの有利な態様において、局部発振器からSHILOまでの距離を越えて伝達される信号の周波数は、近くでミキサをドライブするIおよびQ信号の周波数よりも低い。距離を越えて伝達される信号の周波数を低くすることは、従来のシステムと比較すると、50パーセント以上、LO信号分配システムの電力消費を減じることができる。  (もっと読む)

(もっと読む)

クロック再生装置および電子機器

【課題】受信データ信号のエッジ位置変動が生じたとしても的確にエッジ検出を行うことが可能で、転送レートの高速化および低消費電力化を実現することが可能なクロック再生装置および電子機器を提供する。

【解決手段】ゲーティング信号生成部130Bは、位相判定部120Bの位相判定信号に応じて、エッジ検出部110の検出結果により立ち上がりエッジ検出を示す信号または立ち下がりエッジ検出を示す信号のいずれか一方の信号を第1のゲーティング信号として、他方の信号を受信データ信号の周期の半周期分を遅延させて上記第2のゲーティング信号として生成し、発振器140Bは、位相が第1のゲーティング信号SGT10および第2のゲーティング信号SGT11によって制御され、受信データ信号RDTに同期したクロック信号CLKを出力する。

(もっと読む)

41 - 60 / 223

[ Back to top ]