Fターム[5J106EE09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−付属構成 (846) | 検出回路 (618) | 誤動作検出 (274) | 同期・非同期検出 (247) | 入出力信号から検出 (62)

Fターム[5J106EE09]に分類される特許

1 - 20 / 62

バーストクロック発生回路

【課題】バーストクロック信号を安定に生成できるバーストクロック発生回路を提供する。

【解決手段】このバーストクロック発生回路では、複合映像信号における各垂直帰線期間のうちの垂直同期期間では位相ロックフィルタ4の応答速度を0に設定し、各垂直帰線期間のうちの垂直同期期間を除く期間では位相ロックフィルタ4の応答速度を比較的速い速度v1に設定し、複合映像信号における垂直帰線期間以外の表示期間では位相ロックフィルタ4の応答速度を比較的遅い通常の速度v2に設定する。したがって、標準でない複合映像信号が入力された場合でも、バーストクロック信号を安定に生成できる。

(もっと読む)

基準信号生成装置

【課題】 回路規模を増大させずに複数の外部基準信号を用いて所望の基準信号を生成でき、アンロック時にも安定した基準信号を出力する基準信号生成装置を提供する。

【解決手段】 分周された外部基準信号と分周された電圧制御発振器5の出力との位相を比較する位相比較器32を備え、複数の異なる周波数の外部基準信号を入力可能とし、可変フィルタ10が入力信号を帯域制限し、検波回路11が可変フィルタ出力の信号レベルを検出し、レベル判定回路12が、可変フィルタ10にいずれかの外部基準信号の周波数を通過させる帯域を設定し、信号レベルが適正範囲であれば、入力された外部基準信号の周波数を当該通過帯域の周波数として特定し、第1の分周器31に当該周波数に応じた分周値を設定すると共に、切替器6を位相比較器31側に切り替え、適正範囲外であれば、切替器6を固定電圧生成装置7側に切り替える基準信号生成装置としている。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

クロック生成回路

【課題】従来技術に比較して回路構成が簡単であってサイズが小さく、しかも高精度で位相補正することができるクロック生成回路を提供する。

【解決手段】基準クロックを、互いに縦続接続された複数の遅延素子により所定の遅延幅で遅延して所定の駆動クロックを発生し、上記複数の遅延素子の初段と最終段からの各駆動クロックを位相比較し、当該位相比較結果に基づいて上記複数の遅延素子の遅延量を制御することにより、上記位相比較結果の位相差が小さくなるように制御するDLL回路を備えたクロック生成回路であって、上記複数の遅延素子の初段からの駆動クロックのタイミングで、上記最終段からの駆動クロックのレベルを検出して、上記検出レベルを含む判断結果に基づいて、上記位相差が小さくなるように上記複数の遅延素子の遅延量を制御する位相オフセット手段を備えた。

(もっと読む)

シリアルデータの受信回路、受信方法およびそれらを用いたシリアルデータの伝送システム、伝送方法

【課題】単一の伝送路で、高速なシリアルデータを伝送可能な伝送技術を提供する。

【解決手段】受信回路100は、pビットに2×q回(p、qは実数)の割合で第1レベルから第2レベルへの遷移が生ずるように生成されたシリアルデータDSOUTを受ける。VCO60は、入力された制御電圧Vcnt2に応じた周波数を有するサンプリングクロック信号CLK4を発生する。第1分周器22は、サンプリングクロック信号CLK4を分周比Mで分周する。第2分周器24は、受信したシリアルデータに応じたクロック信号CLKINを分周比Nで分周する。周波数比較器20は、第1分周器22の出力信号と第2分周器24の出力信号の位相差に応じた位相周波数差信号PFDを発生する。制御電圧生成回路42は、位相周波数差信号PFDに応じて、チャージポンプ回路40の周波数を調節するための制御電圧Vcnt2を生成する。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

PLL回路、DLL回路

【課題】基準クロック信号と比較対象となるクロック信号の両者の位相を比較する位相比較器から位相差信号が出力され続けるPLL回路又はDLL回路にあって、両信号の同期を適切に検出して低ジッタ動作を実現する。

【解決手段】同期判定回路(15)は、基準クロック信号(R)の位相を基準として帰還クロック信号(V)の位相が進相又は遅相であるかを検出し、両信号の位相差の期間、進相検出信号(DOWN)又は遅相検出信号(UP)を出力する進相及び遅相検出部(158)と、進相検出信号(DOWN)が出力されている期間、初期値からの計数を開始する進相期間計数部(155)と、遅相検出信号UPが出力されている期間、初期値からの計数を開始する遅相期間計数部(156)と、進相期間計数部又は遅相期間計数部の計数値が第1の規定値に到達しない回数が第2の規定値を上回ったとき、位相同期検出信号(P_DET)を出力する位相同期判定部(157)と、を備える。

(もっと読む)

クロック発生回路

【課題】ロックアップタイムを短くすることのできるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、基準クロックRCLKに基づいて、周波数を変調させた変調クロックSCLKを発生するスペクトラム拡散クロック発生回路10と、基準クロックRCLKと変調クロックSCLKとの位相の一致を検出したときにHレベルのロック信号LOCKを出力する位相比較器20とを含む。また、クロック発生回路1は、Hレベルのロック信号LOCKが出力されるまでは基準クロックRCLKを出力クロックCLKとして選択し、Hレベルのロック信号の出力に応答して変調クロックSCLKを選択するセレクタ50を含む。

(もっと読む)

位相同期回路及びその制御方法

【課題】従来技術の位相同期回路では、入力クロックの切り替え時において、安定した出力クロックを生成することができないという問題があった。

【解決手段】本発明にかかる位相同期回路は、入力クロックを選択するセレクタ3と、入力クロックを分周する1/m分周器4と、フィードバッククロックを分周する1/n分周器5と、位相差検出器と、電圧保持回路30を有する電圧制御発振器10と、電圧保持回路31を有する電圧制御発振器11と、電圧制御発振器10,11のうちいずれかの出力を出力クロックとして出力するセレクタ13と、電圧制御発振器10,11のうちいずれかの出力をフィードバッククロックとして出力するセレクタ12と、備え、保持モードの電圧制御発振器が出力クロックfoutを生成し、通常モードの電圧制御発振器がフィードバッククロックを生成している場合に、入力クロックの切り替えが行われる。

(もっと読む)

アンロック検出回路

【課題】2つの信号間の位相差の発生を正確に検出するアンロック検出回路を提供する。

【解決手段】アンロック検出回路は、論理値を基準信号の変化に応じて記憶する第1フリップフロップと、論理値を入力信号の変化に応じて記憶する第2フリップフロップと、当該第1及び第2フリップフロップの出力の否定論理積を算出するNAND回路とを備えた位相比較器と、第1フリップフロップの出力を基準信号の変化に応じて記憶する第3フリップフロップと、第2フリップフロップの出力を入力信号の変化に応じて記憶する第4フリップフロップとを備えた第1アンロック検出器と、NAND回路の出力を基準信号の変化に応じて記憶する第5フリップフロップと、NAND回路の出力を入力信号の変化に応じて記憶する第6フリップフロップとを備える第2アンロック検出器と、第3、第4、第5及び第6フリップフロップの出力の論理和を算出するOR回路とを具備する。

(もっと読む)

クロック信号を生成できる、または各トランシーバに関連付けられたデジタル・システムのデータのバイパスを可能にする、電力管理されたトランシーバのネットワークを使用する通信システム

【課題】感知回路の雑音感受性を最小にするとともに、回路の少なくとも一部に対する電力を管理して、消費電力を少なくした通信システムを提供する。

【解決手段】通信システムはノードのセットを含む。各ノードはトランシーバ・インターフェイスとデジタル・システムを含む。トランシーバは、通信回線とデジタル・システムとの間に結合されており、伝送フォーマットおよび/または伝送プロトコルを対応するノード内の1つまたは複数のデジタル・システムにより認識されるビットのシーケンスに修正する。トランシーバは、デジタル・システムを支持する回路基板から分離された1つまたは複数のモノリシック回路基板に配置される。

(もっと読む)

半導体集積回路

【課題】テストパターンや期待値パターンを蓄えておくメモリを半導体集積回路に増設することなく、SSCG、PLL、又は、DLL等のクロック生成モジュールの単体試験を容易に可能とする。

【解決手段】この半導体集積回路は、入力されるクロック信号に基づいて新たなクロック信号を生成して出力するモジュールと、モジュールに入力されるクロック信号に含まれているパルス数をカウントする第1のカウンタと、モジュールから出力されるクロック信号に含まれているパルス数をカウントする第2のカウンタと、第1のカウンタのカウント値と第2のカウンタのカウント値とを比較して、両者が一致するか否かを表す信号を出力するコンパレータと、コンパレータから出力される信号をサンプリングする回路とを具備する。

(もっと読む)

クロックリカバリ回路およびデータ再生回路

【課題】クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供する。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

(もっと読む)

同期伝送装置及びジッタ抑圧方法

【課題】同期伝送装置及びジッタ抑圧方法に関し、入力クロックとシステムクロックの周波数偏差のゼロ交叉点付近で発生するピークジッタを抑圧する。

【解決手段】入力クロックを自装置内のシステムクロックでリタイミングした基準クロックを生成するディジタル回路15_1と、基準クロックに同期した出力クロックを生成するPLL回路15_2と、入力クロックの周波数偏差とシステムクロックの周波数偏差との接近を検出する周波数偏差接近検出部1_1と、該周波数偏差の接近が検出されたとき、該周波数偏差の差が増大するよう、システムクロックの発振器1_3の発振周波数を調整する周波数調整部1_2を備える。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

復調器及び通信装置

【課題】受信信号と局部発振信号とに位相差があっても復調できるようにする。

【解決手段】復調器1は、変調器2で送信された受信信号D3をアンテナ11で受信し、この受信した受信信号D3をVCO13に注入して、自走発振周波数を有する局部発振信号D6を発振する。この発振した局部発振信号D6を90度移相器で90度移相する(局部発振信号D7になる)。アンテナ11で受信した受信信号D3の位相と90度移相器で90度移相した局部発振信号D7の位相とを位相比較器15で比較して、局部発振信号D6の位相を調整するための位相調整信号Vctを生成する。この生成した位相調整信号Vctに基づいて、受信信号D3と局部発振信号D6とをVCO13で同期させ、該同期させたものである局部発振信号D8をミキサ17に入力する。注入同期後の局部発振信号D8と受信信号D3とをミキサ17で演算して当該受信信号D3を復調する。

(もっと読む)

位相補正装置、位相補正方法

【課題】無線送信用の電力増幅器の出力をフィードバックする位相補正装置及び位相補正方法において、フィードバック系の安定性を向上させたものを提供すること。

【解決手段】位相検出器10により検出された位相誤差(電圧CV)に対して、想定される位相誤差の全範囲でスイープさせた位相量(スイープ信号の電圧VSWP)を付加して、位相補正の目標値(電圧CV’)とする。これにより、位相補正処理の初期において、PLLのロックレンジへの引き込みを素早く行う。

(もっと読む)

クロック再生装置および電子機器

【課題】受信データ信号のエッジ位置変動が生じたとしても的確にエッジ検出を行うことが可能で、転送レートの高速化および低消費電力化を実現することが可能なクロック再生装置および電子機器を提供する。

【解決手段】ゲーティング信号生成部130Bは、位相判定部120Bの位相判定信号に応じて、エッジ検出部110の検出結果により立ち上がりエッジ検出を示す信号または立ち下がりエッジ検出を示す信号のいずれか一方の信号を第1のゲーティング信号として、他方の信号を受信データ信号の周期の半周期分を遅延させて上記第2のゲーティング信号として生成し、発振器140Bは、位相が第1のゲーティング信号SGT10および第2のゲーティング信号SGT11によって制御され、受信データ信号RDTに同期したクロック信号CLKを出力する。

(もっと読む)

データ再生回路

【課題】バースト光信号が入力された場合のロックアップ動作を高速に行うデータ再生回路を得ること。

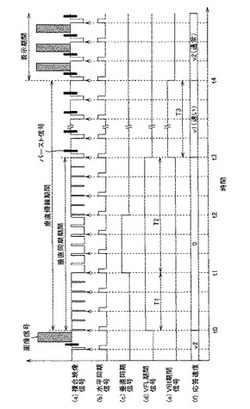

【解決手段】本発明にかかるデータ再生回路は、VCO4で生成したクロックと入力データとを比較し、比較結果に基づいてVCO4への入力電圧を調整するPLL回路(周波数・位相比較器1,フィルタ処理回路2,VCO4)と、VCO4で生成されたクロックを利用して入力データを識別再生する識別回路6と、各子局装置からの送信スケジュールに基づいて、データ入力区間を特定する受信タイミング生成回路8と、を備え、PLL回路は、第1のデータ入力区間が終了後、その次の第2のデータ入力区間が開始するまでの区間では、第1のデータ入力区間に含まれるEOB区間でVCO4への入力としていた電圧信号を、VCO4へ継続して入力させる。

(もっと読む)

基準信号発生装置

【課題】演算処理能力の低い安価なCPUを用いても、ホールドオーバー時における位相差を抑制して、保守作業の時間的制限等の自走発振に係わる課題を解決することができる基準信号発生装置を実現する。

【解決手段】制御部10は、1PPSが入力されている間に同期型制御電圧信号のレベルを経時的に観測し、記憶する。制御部10は、リファレンス信号の入力断を検出すると、自走用第1制御電圧信号を生成し、電圧制御発振器14へ与える。また該自走用第1制御電圧信号を用いて前記電圧制御発振器を制御している期間において、自走用第2制御電圧信号の算出を開始する。そして前自走用第2制御電圧信号の記算出が完了し次第、自走用制御電圧補正値を算出し、位相差を相殺しながら制御を続ける。以後、H.O.が終了するまで、自走用第N制御電圧信号の算出を繰り返し、高精度な基準周波数信号を発生させる。

(もっと読む)

1 - 20 / 62

[ Back to top ]