Fターム[5J106GG18]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 入力回路 (74)

Fターム[5J106GG18]に分類される特許

1 - 20 / 74

高安定発振器

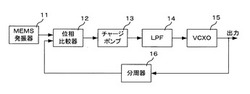

【課題】小型化が容易であり、低コストで製造可能であって、発振出力周波数における短期安定度と長期安定度とを両立させた高安定発振器を提供する。

【解決手段】一定の周波数の信号を出力する高安定発振器は、出力発振器として電圧制御型水晶発振器15を備えるPLL回路と、MEMS振動子を有するMEMS発振器11と、を備える。MEMS発振器11の出力を基準信号としてPLL回路の位相比較器12に供給する。MEMS発振器11によって出力周波数の長期安定度が維持され、電圧制御型水晶発振器15によって出力周波数の短期安定度が維持されるようにする。

(もっと読む)

発振器

【課題】周波数の可変幅を容易に変更することができ、また周波数を高精度に調整することができる発振器を提供すること。

【解決手段】第1のレジスタ3により公称周波数に対応するディジタル値を出力する。第2のレジスタ41により、公称周波数に対して周波数比率で表した周波数の調整量を出力する。一方前記周波数調整量であるディジタル値の可変範囲(フルレンジ)と周波数比率で表わした周波数の可変幅とを対応させるようにゲインを決め、このゲインを第2のレジスタ41からのディジタル値に乗算し、この乗算値と公称周波数に対応するディジタル値とを加算して周波数設定信号とする。

(もっと読む)

発振回路、発振装置およびクロックジェネレータ

【課題】消費電力を低減することができる発振回路を提供する。

【解決手段】入力信号が含むアナログ成分をデジタル信号に変換するアナログ/デジタル変換回路100と、アナログ/デジタル変換回路100で変換されたデジタル信号D1について、予め設定された周波数帯域成分のみを基準信号として通過させるバンドパスフィルタ101と、バンドパスフィルタ101を通過した基準信号D2と、PLLループ内に設けられる電圧制御発振器203からの出力信号D3との位相差が一定となるように電圧制御発振器203にフィードバック制御を行って発振させるPLL回路200とを備え、バンドパスフィルタ101は、所定の条件に基づいて、アナログ/デジタル変換回路100で変換されたデジタル信号D1の所定ビット幅について、「0」に固定するマスク処理を実行するマスク処理部102を備える。

(もっと読む)

発振装置

【課題】メモリの容量を抑えることができる発振装置を提供すること。

【解決手段】第1の発振回路の発振周波数をf1、基準温度における第1の発振回路の発振周波数をf1r、第2の発振回路の発振周波数をf2、基準温度における第2の発振回路の発振周波数をf2rとすると、f1とf1rとの差分に対応する値と、f2とf2rとの差分に対応する値と、の差分値に対応する差分対応値を求める周波数差検出部と、この周波数差検出部にて検出された前記差分対応値xに基づいて環境温度が基準温度と異なることに起因するf1の周波数補正値を取得する補正値取得部と、を備え、装置固有の除算係数をkとすると、前記補正値取得部は、x/kに相当する値であるXについてn次の多項式を演算することによりf1の周波数補正値を求める機能を備えるように装置を構成して、多項式の係数を小さくする。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

クロック再生回路

【課題】ジッタが小さく、面積が小さなクロック再生回路を提供する。

【解決手段】このクロック再生回路は、各UGにおける外部データ信号列Dinの最初の立ち上がりエッジに応答して論理レベルが反転される信号PD_Dinと、内部クロック信号VCOCLKに同期したクロック信号PD_Cinとを生成するエッジ抽出回路1と、信号PD_Dinとクロック信号PD_Cinの位相を比較し、比較結果を示す信号UP,DNを出力する位相比較器6とを備える。したがって、各UGで1回だけ位相比較を行なうので、データパターンに依存するジッタを抑制できる。

(もっと読む)

同期信号処理装置

【課題】回路の小面積化、低消費電力化を図ることが可能であり、しかも温度依存性の影響を受けない安定した位相比較が可能な同期信号処理装置を提供する。

【解決手段】水平同期信号を同期クロックで同期させ、当該同期クロックのタイミングでデジタルデータとして出力する時間デジタル変換器(TDC)と、同期クロックをカウントして参照クロックを生成する参照クロック生成部と、TDCによるデジタルデータと参照クロックの位相比較を行うことにより位相差情報を得るデジタル位相比較器と、デジタル位相比較器の位相差情報に応じて上記参照クロックとTDCによる水平同期信号のデジタルデータの位相が一致するように周波数が制御される同期クロックを生成する同期クロック生成装置と、を有する。

(もっと読む)

クロック発生回路、表示装置用駆動回路及びクロック発生回路の制御方法

【課題】電源投入時や通常動作時でも、より確実にクロックの生成が停止した状態から回復することが可能となるクロック発生回路を提供する。

【解決手段】クロック発生回路1は、クロックとデータとが重畳されたエンベデッド信号から抽出クロックを抽出するクロック抽出回路10と、前記エンベデッド信号と前記抽出クロックとに基づき前記抽出クロックの停止を検出し、前記クロック抽出回路を初期状態にリセットするリセット信号を出力する停止検出回路30と、を備えるものである。

(もっと読む)

発振装置

【課題】水晶振動子の動作時間の経過に伴う発振周波数の変化を補償して安定した発振周波数が得られる発振装置を提供すること。

【解決手段】基準時から所定の時間が経過した後における第1及び第2の水晶振動子の周波数差と、基準時における第1及び第2の水晶振動子の周波数差と、の差分値ΔF(即ち、第1の水晶振動子における周波数について基準時からの変化分と、第2の水晶振動子における周波数について基準時からの変化分との差分値ΔF)を求める。そして基準時からの時間の経過に対して、第1の水晶振動子の周波数の変化分と第2の水晶振動子の周波数の変化分との比率が同じであるとして取り扱ったときの当該比率を経時変化の補正係数とし、差分値ΔFに対応する値と経時変化の補正係数とに基づいて、発振装置の出力を作り出すための水晶振動子の周波数について補正値を取得する。

(もっと読む)

インテグレーテッドPLLを備えたPWMコントローラ

【課題】PWMコントローラチップのサイズ、コスト及び製造上の複雑を減らす。

【解決手段】位相ロックループ(PLL)を用いた電子部品に電力を供給するためのパルス幅変調(PWM)コントローラが、提供される。PWMコントローラは、基準信号を受信する入力ノードと、位相ロックループ(PLL)とを備えている。このPLLは、位相信号を受信し且つ前記誤り訂正信号に関係する周波数を有する発振器信号を生成する発振器と、前記発振器に結合され、前記基準信号を受信し、且つ前記基準信号と、フィードバック信号との間の位相差に基づいて前記位相信号を生成させる位相周波数検出器(PFD)と、前記PFDに結合され、周期的にPFDが前記位相信号を生成することができるようにする抑制回路と、前記PFDに結合され、前記位相信号が同時に活性である時間の長さを制限するように動作可能なフィードフォワード回路とを備えている。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

半導体装置及びその測定方法

【課題】従来の測定方法では、測定電流の精度を十分に確保できない問題があった。

【解決手段】本発明の半導体装置の測定方法は、外部端子TMと、出力信号の位相及び周波数に応じてチャージポンプ回路12を制御する位相周波数比較器11と、周波数制御電圧生成ノードVNDに対する電流を出力するチャージポンプ回路12と、チャージポンプ回路12が出力する電流に応じて周波数制御電圧を周波数制御電圧生成ノードVNDに生成するループフィルタ14と、周波数制御電圧に応じて出力信号の周波数を制御する電圧制御発振器15と、を有する半導体装置の測定方法であって、外部端子TMを介してチャージポンプ回路12の出力電流を含む第1、第2の測定電流のいずれか一方を測定し、外部端子TMに流れるリーク電流を含む第3の測定電流を測定し、第1、第2の測定電流とリーク電流との差分に基づき流出電流IS1又は流入電流IS2の電流値を算出する。

(もっと読む)

局部発振器

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

クロック切り替え回路

【課題】クロック切り替えの時間を短縮すること。

【解決手段】本発明は、光ケーブルを介して入力された光信号から抽出したクロック信号と、自回路内部のクロック源からのクロック信号との切り替えを行うクロック切り替え回路に適用される。本発明のクロック切り替え回路は、光信号からクロック信号を抽出するクロック抽出部と、前記クロック抽出部にて抽出されたクロック信号を、互いに異なる分周数で分周する複数の分周器と、前記複数の分周器にそれぞれ対応して設けられ、対応する分周器にて分周されたクロック信号のクロック周波数が所定のクロック周波数と一致する場合に同期信号を出力する複数の同期検出部と、光ケーブル接続が切断された場合、同期信号を出力した同期検出部に対応する分周器にて分周されたクロック信号から、当該クロック信号と同じクロック周波数成分を持ったクロック源からのクロック信号への切り替えを行うスイッチと、を有する。

(もっと読む)

PLL回路

【課題】 位相ノイズを低減し、設計が容易なPLL回路を提供する。

【解決手段】 PLL3が、基準周波数とVC−TCXO4からの出力を入力し、ロック動作を行い、ロック状態となると、セレクタ6は基準周波数を分周する第1の分周器2の出力を選択し、PLL3が、基準周波数入力断又はロック外れを検出すると、アラーム信号をセレクタ6に出力し、セレクタ6が、PLL3からのアラーム信号が入力されると、第1の分周器2の出力から、VC−TCXO4の出力を分周する第2の分周器5の出力に切り替えて出力し、PLL7が、セレクタ6の出力とVCXO8の出力とを入力し、ロック動作を行うPLL回路である。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

周波数シンセサイザ

【課題】位相雑音を改善することのできる周波数シンセサイザを提供すること。

【解決手段】周波数設定部により設定された周波数の正弦波信号を設定信号出力部からディジタル信号として出力し、これをD/A変換する。ここから出力された正弦波信号と電圧制御発振部の出力周波数に対応する周波数の正弦波信号と、前記D/A変換部からの正弦波信号と、の差分を差動増幅器で増幅し、増幅された信号をA/D変換部を介して、既述の両正弦波信号の位相差を取り出す手段に入力する。この位相差を積分した信号に相当する電圧を電圧制御発振器に制御電圧として入力する。そして差動増幅器の利得をA/D変換部の位相雑音劣化の最大値よりも大きく設定し、これによりA/D変換部の位相雑音劣化をキャンセルする。

(もっと読む)

クロック・データ再生回路及び再生方法並びに局側装置

【課題】バースト信号間の無信号区間に入ったとき、一時的に参照クロック信号と周波数が大きくずれるという現象の発生を防止することができるクロック・データ再生回路及び再生方法並びに当該再生回路を用いた局側装置を提供する。

【解決手段】周波数逓倍部110により、参照クロック信号の周波数をデータ信号相当の周波数に逓倍して逓倍クロック信号とする他、入力選択部111を用いて入力を選択する。すなわち、データ信号としてのバースト信号が入力されているときは、入力されたバースト信号と位相が同期するように再生クロック信号を生成し、バースト信号が入力されていないときは逓倍クロック信号と位相が同期するように再生クロック信号を生成する。

(もっと読む)

位相同期回路及び位相同期方法

【課題】低品質の入力光信号に対しても、安定して同期信号を発生するとともに、入力光信号が有するクロック信号に対する位相誤差検出感度を高くし、同期信号のタイミングジッタを低減し、製造コストを削減することである。

【解決手段】位相同期回路10は、基準信号を発生する基準信号発生部22と、入力光信号と電気信号とを位相比較して第1の位相誤差信号を生成する光位相比較部1と、第1の位相誤差信号と、基準信号と、を位相比較して第2の位相誤差信号を生成し、第2の位相誤差信号における入力光信号のクロック信号周波数に対応する周波数成分のみに応じて入力光信号の位相に同期した出力信号を発生して出力する位相同期部2と、基準信号の分周信号を用いて、位相同期部2から出力された同期信号をSSB変調して電気信号として光位相比較部1に出力する変調部3と、を備える。

(もっと読む)

PLL回路及び発振装置

【課題】クロック信号を安定的に生成するPLL回路及び発振装置を提供すること。

【解決手段】水晶発振回路1は、同水晶発振回路1に設けた駆動可変部の駆動能力をPLL回路50aのループフィルタ59から出力される制御信号Slfの電圧値に応じて制御する。

(もっと読む)

1 - 20 / 74

[ Back to top ]