Fターム[5J106HH02]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御量 (1,632) | 位相 (516)

Fターム[5J106HH02]に分類される特許

1 - 20 / 516

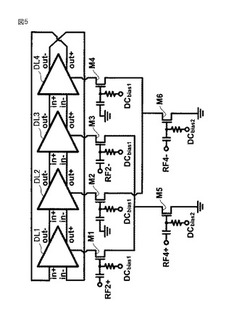

分周回路およびPLL回路

【課題】2分周、8分周、さらには8分周可能な回路規模の小さな低消費電力の注入同期型分周回路の実現。

【解決手段】偶数個Mの遅延要素DL1-DL4を有するリングオシレータ11と、入力発振信号から同期信号を生成して複数個の遅延要素の少なくとも一部に注入する同期信号注入回路と、を有し、入力発振信号の分周信号を出力する分周回路であって、遅延要素のオン・オフする分周トランジスタの一方の被制御端子が注入ノードであり、同期信号注入回路は、M/2個離れた2つの遅延要素の注入ノードに接続されるように並列に設けられた2個の補助注入トランジスタを有する注入差動対M1-M4と、入力発振信号RF4+,RF4-が制御端子に入力され、注入差動対の注入ノードとの接続ノードに、入力発振信号の差動信号を発生するように注入差動対に接続された信号注入トランジスタM5,M6と、を有する分周回路。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

原子発振器

【課題】キャリア光を帯域通過フィルタによって減衰させて、信号検出のS/Nを改善して周波数安定度を高めた原子発振器を提供する。

【解決手段】の原子発振器100は、半導体レーザーにより構成されるLD(光源)1と、LD1に直流電流を与え、LD1の波長を所定の値に設定する中心波長設定部13と、アルカリ金属が封止された原子セル2と、アルカリ金属原子を透過したキャリア光(ωc)と共に第1の共鳴光(ω1)、及び第2の共鳴光(ω2)のうちいずれか一方の光を減衰させる波長フィルタ14と、波長フィルタ14を通過した原子セル2の透過光を検出するPD(光検出器)3と、を備えて構成される。

(もっと読む)

半導体装置

【課題】半導体装置の入出力クロックスキューを抑制する。

【解決手段】I/O電圧電源で駆動される第1のバッファ1及び第2のバッファ8と、I/O電圧電源の電圧レベルを示す電圧判定信号を生成する電圧判定部5と、第1のバッファ1を介して入力された入力クロック信号に基づいて出力クロック信号の位相を調整して第2のバッファへ出力するエコークロック生成部7と、電圧判定信号と位相の調整量との関係を選択するモード情報を記憶する記憶部6と、を有し、エコークロック生成部7は、電圧判定信号とモード情報とに基づいて出力クロック信号の位相の調整量を決定する。

(もっと読む)

デジタルPLL回路、半導体集積回路装置

【課題】デジタルPLL回路の追従可能な周波数レンジを拡大する。

【解決手段】第1カウンタ(21)は、第1クロック信号をカウントして第1カウント値を出力し、第2カウンタ(22)は、第2クロック信号を分周して生成される第3クロック信号をカウントして第2カウント値を出力する。位相検出器(23)は、第1クロック信号と、第3クロック信号との位相差をデジタル値で示す出力値を出力する。位相誤差演算回路(26)は、第1カウント値と、第2カウンタ値と、出力値とに基づいて、位相誤差を演算して出力する。デジタルフィルタ回路(107)は、位相誤差を平滑化して発振周波数を示すコードを出力する。デジタル制御発振器(108)は、コードに応答して第2クロック信号を出力する。キャリブレーション制御回路(112)は、分周比と、第2クロック信号と第1クロック信号との比較結果とに基づいてデジタル制御発振器の発振周波数を調整する。

(もっと読む)

時間−デジタル変換器及びPLL回路

【課題】本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することを目的とする。

【解決手段】本発明は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される複数の遅延素子21と、複数の遅延素子21が出力する複数の遅延クロック信号を、PLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする複数のラッチ回路22と、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する遅延時間調整回路32と、を備えることを特徴とするTDC2である。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

デューティ補正付き位相調整回路及びシリアライザ

【課題】クロックのばらつきが引き起こすジッタを抑制することが可能なデューティ補正付き位相調整回路及びシリアライザを提供することを目的としている。

【解決手段】正クロック信号及び負クロック信号が入力され前記正クロック信号と前記負クロック信号のデューティ及び位相を調整した正クロック出力信号及び負クロック出力信号を出力する。

(もっと読む)

クロック生成回路、及びクロック生成方法

【課題】一種類の多相クロックより多くの周波数の種類の単相クロックを得ることができるクロック生成回路及びその方法を提供する。

【解決手段】少なくともn個の位相補間器を有し、周波数がfで位相差が1/(f×m)づつ異なるm相クロックを、周波数がfで位相差が1/(f×n)づつ異なるn相クロックに変換するクロック変換回路1と、前記n相クロック信号の一部又は全部を用いて、周波数(f×n)/Aの単相クロック信号を生成する単相クロック生成回路2と、前記位相補間器に設定する内分比を制御する制御回路とを有し、前記各位相補間器は、前記m相の内の異なる二つのクロックを入力し、それらのタイミング差を、制御回路により設定した内分比で分割した遅延時間のクロックを生成して出力し、前記制御回路は、基準クロックと、回路の末端で分配されたクロックとのタイミングとが一致するように内分比を制御する。

(もっと読む)

アナログデジタル変換器及び無線受信機

【課題】アナログデジタル変換器のサンプリングクロックのジッタの影響を、低消費電力でデジタル補正する。

【解決手段】アナログデジタル変換器のサンプリングクロックを、サンプリングクロックよりも低周波数かつ低ジッタの基準クロックを源振とする位相同期ループ(PLL)により生成する。サンプリングクロックと基準クロックが同期するタイミングにおけるタイミング誤差を時間デジタル変換器(TDC)によりデジタル値に変換する。なお、基準クロックが存在しないサンプリングタイミングにおけるタイミング誤差については、検出されたタイミング誤差を補間して生成する。これにより、各サンプリングタイミングにおけるサンプリングクロックのジッタ値を取得する。当該ジッタ値からサンプリング電圧誤差を算出し、アナログデジタル変換器の出力をデジタル補正する。

(もっと読む)

周波数調整回路、位相同期回路、通信装置及び記憶装置

【課題】帯域制限フィルタを含むPLLのロックアップ時間を短縮する。

【解決手段】実施形態によれば、周波数調整回路200は、レジスタ213と、デジタルアナログ変換器220と、帯域制限フィルタ250と、バッファアンプ240とを含む。レジスタ213は、第1の動作モードの終了時にデジタル制御コード12を保存し、第3の動作モードの開始時に出力する。第1の動作モードにおいて、制御電圧15を持つアナログ制御信号14が電圧制御発振器110の制御端子に供給される。第2の動作モードにおいて、アナログ制御信号14がバッファアンプ240に供給され、バッファアンプ240は帯域制限フィルタ250を駆動し、帯域制限フィルタ250は制御電圧15を生成する。第3の動作モードにおいて、アナログ制御信号14が帯域制限フィルタ250に供給され、帯域制限フィルタ250は制御電圧15を生成する。

(もっと読む)

多相クロック発生回路、及び多相クロック発生方法

【課題】回路規模の増加を抑えかつ出力信号のジッタ特性を低下させずに、複数の動作周波数に対応できる多相クロック発生回路を提供する。

【解決手段】多相クロック発生回路は、位相の異なる複数のリファレンスクロック信号が入力され、該リファレンスクロック信号が取り得る複数の周波数ごとに設けられた遅延パスであって該リファレンスクロック信号に対して予め定められた位相差を生じさせる複数の遅延パスと、リファレンスクロック信号の周波数に基づいて、複数の遅延パスのうち、リファレンスクロック信号の周波数に対応する遅延パスを選択するスイッチ部と、スイッチ部が選択した遅延パスにより、位相差が変更された複数のリファレンスクロック信号から所定の位相差を有する複数のクロック出力信号を生成する位相補間回路とを備える。

(もっと読む)

半導体装置

【課題】アナログ電圧を使用することなく、クロック信号を高精度且つ広範囲に遅延させる。

【解決手段】入力ノード110aと出力ノード110bとの間に直列接続された複数のワンショットパルス生成回路201〜20nを備える。ワンショットパルス生成回路201〜20nのそれぞれは、入力されたクロック信号の一方のエッジに応答して、ワンショットパルスを生成する。ワンショットパルスのパルス幅は、カウント値RCNTに基づいて可変である。これにより、カウント値RCNTを変化させることによって、ディレイライン110の遅延量を広範囲且つ高精度に変化させることが可能となる。しかも、アナログ電圧を使用しないことから、アナログ電圧の生成回路やその安定化回路などを設ける必要もなくなり、回路設計が容易となる。

(もっと読む)

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

半導体装置

【課題】電流消費を削減する。

【解決手段】第1のクロック信号(ICLK)を受け、第1のクロック信号を可変である遅延量に応じて遅延させた第2のクロック信号(LCLK)を出力する遅延回路(31)と、第2のクロック信号を受け、遅延された第3のクロック信号(RCLK)を出力するレプリカ回路(32)と、第1および第3のクロック信号の位相差が所定時間以上であるか否かを検知し、所定時間以上である場合には遅延回路の遅延量を変化させ、所定時間未満である場合には遅延回路の遅延量を変化させないように制御する位相差検出回路(36)と、を備える。

(もっと読む)

位相周波数比較回路

【課題】雑音特性及び高速動作を維持しながら、消費電力を削減することができる位相周波数比較回路を得ることを目的とする。

【解決手段】出力バッファ回路3が、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からUP信号が出力された場合、アップ信号を出力し、電流制御信号生成回路2から電流制御信号が出力されている期間中、位相周波数比較コア回路1からDN信号が出力された場合、ダウン信号を出力する。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

遅延ロックループ回路及びロックアップ方法

【課題】レイアウト面積の増加を抑えつつロックアップ時間の高速化を実現する。

【解決手段】本発明に係る遅延ロックループ回路1は、遅延ライン3と、初期遅延モニタリング部4と、位相比較部5と、遅延制御部6と、ファイン遅延部7とを備え、初期遅延モニタリング部4は、基準クロックと複数の単位遅延部のうちの一部の単位遅延部が出力する単位遅延クロックとの位相を比較する複数の位相比較用フリップフロップを備え、これら位相比較用フリップフロップの数を単位として当該比較を段階的に繰り返すことにより、全範囲について初期遅延モニタリングを行うものである。

(もっと読む)

位相調整回路及び位相調整方法

【課題】LSIチップ面積の増大を抑制しつつ、製造ばらつきや使用条件の影響を受けない安定的な位相調整を実現する

【解決手段】入力クロックと出力クロックの位相差を調整する位相調整回路を以下のように構成する。その位相調整回路は、出力クロックに遅延を付加するクロック遅延回路と、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスを入力として受け、パルス除去幅設定値によって遅延素子の段数を変化させて、入力クロック、もしくは、入力クロックと出力クロックの位相差のパルスの幅を検出する位相差検出回路とを有することが好ましい。そして、位相差検出回路で検出した入力クロックと出力クロックの位相差が入力クロックに対して目標の位相差になるようにクロック遅延回路にて出力クロックに遅延を付加する。

(もっと読む)

1 - 20 / 516

[ Back to top ]