Fターム[5J106JJ04]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | フィルタ回路 (84)

Fターム[5J106JJ04]に分類される特許

1 - 20 / 84

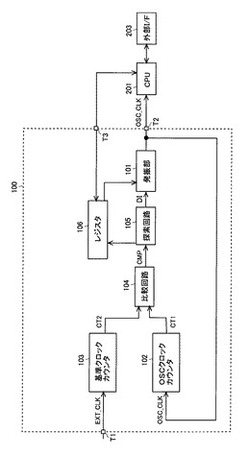

クロック発振回路

【課題】発振周波数のトリミングを行うクロック発振回路であって、CR発振回路の特性に起因する発振周波数のばらつきを低減することが可能なクロック発振回路を提供する。

【解決手段】クロック発振回路は、周波数調整コードに応じた発振周波数のクロック信号を生成する発振部101と、発振部101の発振周波数をカウントするOSCクロックカウンタ102と、外部接続された水晶発振器の発振周波数をカウントする基準クロックカウンタ103と、両発振周波数の比較を行う比較回路104とを備える。また、周波数調整コードの自動探索を行う探索回路105を備える。探索回路105は、周波数調整動作時において、発振部101に対する周波数調整コードの設定と、比較回路104による比較結果に応じた周波数調整コードの更新とを繰り返し行うことにより、周波数調整コードの自動探索を行う。

(もっと読む)

位相同期回路及びテレビジョン信号受信回路

【課題】チューニングラインに設けられるラインフィルタのフィルタ特性の低下を防止すること。

【解決手段】この位相同期回路は、チャージポンプ(35)から出力されるパルス信号を積分するローパスフィルタ(19)と、ローパスフィルタ(19)から電圧制御発振回路(17A)に対して制御電圧を供給する制御電圧供給ライン(LUHF)に設けられたラインフィルタ(20)と、を具備し、ラインフィルタ(20)のキャパシタ(C1)の一端をチャージポンプ(35)の出力端子からCP電流切替回路(36)の抵抗(r)を介してグランドに高周波的に接続した。

(もっと読む)

周波数調整回路、位相同期回路、通信装置及び記憶装置

【課題】帯域制限フィルタを含むPLLのロックアップ時間を短縮する。

【解決手段】実施形態によれば、周波数調整回路200は、レジスタ213と、デジタルアナログ変換器220と、帯域制限フィルタ250と、バッファアンプ240とを含む。レジスタ213は、第1の動作モードの終了時にデジタル制御コード12を保存し、第3の動作モードの開始時に出力する。第1の動作モードにおいて、制御電圧15を持つアナログ制御信号14が電圧制御発振器110の制御端子に供給される。第2の動作モードにおいて、アナログ制御信号14がバッファアンプ240に供給され、バッファアンプ240は帯域制限フィルタ250を駆動し、帯域制限フィルタ250は制御電圧15を生成する。第3の動作モードにおいて、アナログ制御信号14が帯域制限フィルタ250に供給され、帯域制限フィルタ250は制御電圧15を生成する。

(もっと読む)

PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

(もっと読む)

位相ロックループ回路

【課題】電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路と、検出された位相差に応じた電流を第1の容量に出力するチャージポンプ回路と、第1の容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路とを有する位相ロックループ回路にて、チャージポンプ回路による第1の容量への電流の出力完了後の第1の時刻に第1の電圧を保持し、保持された第1の電圧に基づき電圧制御発振回路の入力部に流れるリーク電流に応じた電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して第1の容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】ループフィルタをオンチップ化する際、トランジスタの素子サイズのバラツキによるPLL回路の特性バラツキを軽減して、回路規模と消費電力の増大を軽減する。

【解決手段】半導体集積回路は、位相周波数比較器1とループアッテネータ2とチャージポンプ3とループフィルタ4と電圧制御発振器5と分周器6を具備するフェーズロックドループ回路を内蔵する。アッテネータ2は、サンプリング回路21とカウンタ22とを含む。回路21にサンプリングパルスSPL_CLKと位相周波数比較器1から出力される第1と第2の出力信号が供給され、回路21はサンプリング出力信号を出力する。カウンタ22は回路21から出力される所定個数のサンプリングパルスのカウントアップを完了すると、カウントアップ完了出力信号を出力する。チャージポンプ3は、カウントアップ完了出力信号に応答してループフィルタ4に充電電流または放電電流を出力する。

(もっと読む)

PLL周波数シンセサイザ

【課題】 フラクショナルN方式のPLL(Phase-locked loop;位相同期回路)周波数シンセサイザにおいて生じる、フラクショナルスプリアスを抑圧する。

【解決手段】 可変分周器の分周数を2つ以上の整数値で時間的に切り替えるフラクショナルN方式のPLL周波数シンセサイザにおいて、電圧制御発振器2とループフィルタ7の間に、抑圧周波数および減衰量の制御を可能とする可変ノッチフィルタ8を設けることで、フラクショナルスプリアスを抑圧することができる。

(もっと読む)

原子発振器用の光学モジュールおよび原子発振器

【課題】周波数安定度の高い原子発振器を得ることが可能な原子発振器用の光学モジュールを提供する。

【解決手段】光学モジュール2は、量子干渉効果を利用する原子発振器用の光学モジュール2であって、所定の波長を有する基本波F、当該基本波の側帯波W1,W2、を含む光L1を出射する光源10と、光源10からの光が入射し、当該入射した光のうち側帯波W1,W2を透過させる波長選択部20と、アルカリ金属ガスを封入し、波長選択部20を透過した光L2が照射されるガスセル30と、ガスセル30に照射された光のうちガスセル30を透過した光の強度を検出する光検出部40と、を含み、波長選択部20は、所定の波長範囲の光を透過させる光フィルター部20aと、光フィルター部20aが透過させる光の波長範囲を変化させる光フィルター特性制御部20bと、を有する。

(もっと読む)

無線通信装置

【課題】対象装置からの信号に基づいて当該対象装置と同期をとる構成において、非同期状態から同期状態へ早期に復帰することが可能な無線通信装置を提供する。

【解決手段】無線通信装置201は、対象装置から受信した受信データに基づいて生成された再生タイミング信号に基づいて第1の制御電圧を生成し、電圧制御発振器25に第1の制御電圧を供給することにより、再生タイミング信号の周波数成分のうち、所定の周波数以上の成分が減衰された周波数成分を有し、かつ再生タイミング信号に同期する基準タイミング信号を生成するためのジッタ抑圧部12と、タイミング信号生成部22によって生成される再生タイミング信号の異常を検知し、異常を検知した場合には、第1の制御電圧の代わりに、第1の所定範囲内の電圧である第2の制御電圧を電圧制御発振器25に供給するための発振器制御部13とを備える。

(もっと読む)

回路装置及び電子機器

【課題】低消費電力でキャリブレーションができる回路装置及び電子機器等を提供すること。

【解決手段】回路装置は、無線による送信処理を行う送信回路100と、送信回路100を制御する制御部110とを含む。制御部110は、第1の送信期間では、送信回路100のキャリブレーションパラメーターCLPとして、第1のキャリブレーションパラメーターCLP1を設定し、送信回路100は、第1の送信期間では、第1のキャリブレーションパラメーターCLP1に基づく第1の送信処理を行う。制御部110は、第2の送信期間では、キャリブレーションパラメーターCLPとして、第1の送信処理での送信状態の検出結果に基づいて更新された第2のキャリブレーションパラメーターCLP2を設定し、送信回路100は、第2の送信期間では、第2のキャリブレーションパラメーターCLP2に基づく第2の送信処理を行う。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

PLL回路

【課題】ループフィルタの容量値を抑え、且つ動作を安定させることが可能なPLL回路を提供することを目的としている。

【解決手段】入力信号の位相と電圧制御発振回路の出力信号の位相とを比較し、位相差に応じた信号を出力する位相比較器と、前記位相比較器の出力信号に応じて充放電電流を生成するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑し第一の制御電圧を生成するループフィルタと、前記ループフィルタから出力される前記第一の制御電圧を所定の電圧になるよう第二の制御電圧を生成する制御電圧生成回路と、を備え、前記第一の制御電圧と前記第二の制御電圧とが前記電圧制御発振回路に入力される。

(もっと読む)

光受信装置及びクロック生成方法

【課題】分散値の調整を簡易かつ迅速に行うとともに、分散値の調整時にアンロック状態が発生することを回避すること。

【解決手段】分散補償部は、設定された分散値を用いて光信号の波長分散を補償する。位相差信号生成部は、分散補償部によって補償された光信号に含まれるクロックである外部クロックと、自装置内で用いるクロックである内部クロックとの位相差を算出することにより位相差信号を生成する。分散値調整部は、分散補償部に設定された分散値を調整する。抑制部は、分散値調整部によって分散値が調整された場合に、位相差信号生成部によって生成された位相差信号に現れる変動を抑制する。クロック生成部は、抑制部によって抑制された位相差信号に基づいて、外部クロックの位相と同期した内部クロックを生成する。

(もっと読む)

適応デジタル位相ロックループ

【課題】従来のデジタルPLLで問題であった出力クロックの位相ノイズ及びジッタ性能の低下に対応するアプローチを提供する。

【解決手段】幾つかの実施形態で、デジタルPLLは、例えば位相エラー等の1又はそれ以上の実時間性能パラメータに応答して有効なDPLL帯域幅を変更する動的制御可能なフィルタを有して開示される。高帯域幅が必要とされないとき、それは比較的低いレベルであるよう制御されてよく、それによって、出力クロックのジッタは低下する。他方で、高帯域幅が必要とされるとき、例えば、ループでの位相エラーが高いとき、フィルタは、基準クロックを追跡するためにループの応答性を高めるよう比較的高いループ帯域幅を提供するように制御され得る。

(もっと読む)

PLL回路

【課題】高速かつ確実に低雑音特性を得ることができるPLL回路を得ることを目的とする。

【解決手段】相互に異なる移相量PS14,PS24,PS34がそれぞれ設定されており、N分周された発振信号の位相を設定されている移相量だけ変える移相器4−1〜4−3と、移相量の差分の関係が移相器4−1〜4−3のそれぞれに設定されている移相量の差分の関係と一致する条件の下で、相互に異なる移相量PS15,PS25,PS35がそれぞれ設定されており、R分周された基準信号Refの位相を設定されている移相量だけ変える移相器5−1〜5−3とを設ける。

(もっと読む)

デジタルPLL回路とその制御方法

【課題】比較的簡易な回路構成で、制御時定数を短くしても超高安定な位相同期を実現する。

【解決手段】基準クロックを1/m分周器12で1/m倍し、VCXO11で発生される発振クロックを1/n分周器13で1/n倍し、両クロックを量子化位相比較器14に送り、両クロックのずれ量に相当する量子化位相差δを取得して予測制御器15に送る。予測制御器15では、入力された量子化位相差を、その極性が負から正に反転してから再び負に反転するまで、または正から負に反転してから再び正に反転するまで積分し、この積分値に-0.5倍〜-0.05倍の予測係数を掛けた値を予測重み値として求め、この予測重み値を積分値に加算して制御電圧値を予測する。この予測制御器15で予測された制御電圧値を、D/A変換器16でアナログ電圧に変換し、LPF17によって決まるループ時定数でフィルタリングして、周波数制御電圧としてVCXO11に送る。

(もっと読む)

電流源、電子機器および集積回路

【課題】低電圧駆動において安定した定電流を供給する。

【解決手段】電流源1は、入力電流に応じた周波数の発振信号を出力する電流制御発振部11と、発振信号と基準信号とを比較する比較部13と、比較部13の比較結果に応じた電流を出力するチャージポンプ14と、チャージポンプ14の出力電流により充放電される平滑キャパシタ42を含むローパスフィルタ15と、平滑キャパシタ42に接続され、平滑キャパシタ42が生成する電圧に応じた電流を生成し、入力電流として電流制御発振部11へ供給するループ用変換部16と、ローパスフィルタ15に接続され、ローパスフィルタ15において生成される電圧に応じた電流を生成し、出力電流として出力する出力用変換部17とを有する。

(もっと読む)

PLL回路

【課題】拡散周波数が未知の拡散信号から拡散周波数成分を除去できるPLL回路を提供する。

【解決手段】一の信号の位相と他の信号の位相との差分に応じた差分信号を出力する位相比較器1、差分信号に応じた電流信号を生成するチャージポンプ回路2、電流信号を平滑化して信号n1を生成するループフィルタ9、信号n1をフィルタリングして信号n2、n5を生成するノッチフィルタ5、信号n1の位相と信号n2の位相との差分に基づいて、ノッチフィルタ5によって遮断される遮断周波数を調整する遮断周波数調整回路6、信号n5に基づいて所定の周波数の信号を発振する電圧制御発振回路3によってPLL回路を構成する。ノッチフィルタ5は、ループフィルタ9によって遮断される周波数よりも低い周波数の範囲に上限値と下限値が含まれる所定の範囲の周波数を遮断する。

(もっと読む)

同期および追跡動作モードを有する位相同期ループシステム

【課題】同期モードと追跡動作モードを有する位相同期ループ(PLL)システム。

【解決手段】PLLは、所望の周波数で信号を出力する電圧制御発振器(VCO)を含む。位相検波器がVCOからの出力に結合されている。位相検波器は、VCOからの信号出力の位相を基準信号の位相と比較する。ループフィルタ601がVCOと位相検波器とに結合されている。ループフィルタ601はスイッチ603を含む。スイッチ603が垂直な位置に設定されるとき、VCO信号の位相を基準信号の位相に同期させるために、ループフィルタ601は同期動作モードとなる。スイッチ603を水平な位置に設定することにより、ループフィルタを追跡動作モードに置くことができ、追跡動作モードはVCO信号の位相を調整して、基準信号の位相を追跡する。

(もっと読む)

PLL回路

【課題】ループ内の無駄時間を補償し、所望の特性を取得可能なPLL回路を提供する。

【解決手段】メインパス110は、入力段に配置され、入力信号と実信号との位相検出を行うフェーズディテクタ111と、フェーズディテクタの出力側に配置され、ループの応答特性を決めるためのループフィルタ113と、ループフィルタの出力信号に応じた周波数で発振し、発振信号を実信号としてメイン帰還パスに出力する制御発振器114と、を含み、ローカル帰還パス130は、ループフィルタの出力が入力され、制御発振器のレプリカとして機能するレプリカ部131と、レプリカ部の出力を一巡無駄時間分遅延させる遅延部132と、遅延部の入力信号と出力信号の差分を得る第1の減算器133と、第1の減算部の出力信号からループフィルタ中の内部信号を定数倍した信号を減算し、ループフィルタの入力側に出力する第2の減算器136と、を含む。

(もっと読む)

1 - 20 / 84

[ Back to top ]