Fターム[5J106KK30]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 信頼性の向上 (1,507) | 誤動作防止 (141) | 誤同期防止 (56)

Fターム[5J106KK30]に分類される特許

1 - 20 / 56

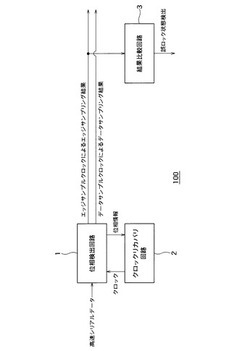

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

誤ロック防止回路、防止方法及びそれを利用した遅延ロックループ

【課題】遅延ロックループにおいて誤ロックが生じた場合、そこから抜け出すために使用される誤ロック防止回路、防止方法及びそれを利用した遅延ロックループを提供する。

【解決手段】誤ロック防止回路はハーモニックロックを検出する検出器とスタックロックを検出する検出器とで構成される。ハーモニックロック検出器は前記遅延クロックを本発明の特徴的な方法でサンプリングする複数個のフリップフロップ及び論理部で構成される。ハーモニックロック検出器では基準クロックと基準クロックから遅延された複数個の遅延クロックの立ち上がりエッジを比較してこれらの立ち上がりエッジが基準クロックの1周期から離れた場合を検出する。スタックロック検出器は位相検出器の出力信号と前記遅延クロックのうち1つを利用した論理回路であり、論理演算の結果で位相検出器をリセットさせる。

(もっと読む)

クロック生成装置、クロック生成方法及びプログラム

【課題】目的の周波数からずれた周波数のクロックをクロックの供給先に与える危険性の少ない、クロック生成装置を提供する。

【解決手段】各クロック供給部10,20に、水晶発振器であるVCXO11,21を目的の周波数で発振させるために設定された基準値と基準値が設定された時を示す設定時情報とを記憶するメモリ14,24と、VCXO11,21の生成するクロックを他のクロック供給部のVCXOの出力するクロックに同期させる同期手段とをそれぞれ備える。メモリ14,24の記憶内容に基づき、最も設定時情報が新しいVCXOを選別し、その選別したVCXOを基準値に基づいて発振させて目的の周波数のクロックを生成させる。他のVCXOには、選別したVCXOの生成したクロックに同期したクロックを生成させる。

(もっと読む)

半導体装置

【課題】入力信号と出力信号の位相差の増大を抑制すること。

【解決手段】本発明の半導体装置は、縦続接続された複数の遅延素子を用いて、入力信号と出力信号の位相を合致させるロック調整動作を行うDLL回路と、リファレンス電位を基準として生成した出力電圧を、複数の遅延素子に供給する遅延素子用電源回路と、出力電圧がリファレンス電位の一定範囲内にあるか否かを検出し、出力電圧が一定範囲内にない場合、ロック調整動作を停止させるDLL動作信号をDLL回路に出力する検出回路と、を有する。

(もっと読む)

同期信号生成装置および同期信号生成方法

【課題】ホールドオーバー状態からGPSロック状態に復帰する際の基地局の状態に応じて、内部パルスおよび内部周波数信号をGPS基準パルスに同期させた状態に復帰させることができる同期信号生成装置および同期信号生成方法を提供することである。

【解決手段】本発明に係る基地局3にパルスを提供する同期信号生成装置は、GPS衛星から受信した信号からGPS基準パルスを生成するGPS受信器11と、内部周波数信号を生成する発振器15と、内部周波数信号を分周して内部パルスを生成する分周器12と、GPS基準パルスと内部パルスとを比較して前記内部パルスを前記GPS基準パルスに同期させる同期部14と、基地局3の状態に応じて、ホールドオーバー状態からGPSロック状態に復帰するときの、同期部14のループタイムを決定する制御部13と、を備える。

(もっと読む)

アンロック検出回路

【課題】2つの信号間の位相差の発生を正確に検出するアンロック検出回路を提供する。

【解決手段】アンロック検出回路は、論理値を基準信号の変化に応じて記憶する第1フリップフロップと、論理値を入力信号の変化に応じて記憶する第2フリップフロップと、当該第1及び第2フリップフロップの出力の否定論理積を算出するNAND回路とを備えた位相比較器と、第1フリップフロップの出力を基準信号の変化に応じて記憶する第3フリップフロップと、第2フリップフロップの出力を入力信号の変化に応じて記憶する第4フリップフロップとを備えた第1アンロック検出器と、NAND回路の出力を基準信号の変化に応じて記憶する第5フリップフロップと、NAND回路の出力を入力信号の変化に応じて記憶する第6フリップフロップとを備える第2アンロック検出器と、第3、第4、第5及び第6フリップフロップの出力の論理和を算出するOR回路とを具備する。

(もっと読む)

冗長PLL回路

【課題】本線系と冗長系との間に生じる出力位相の偏差を抑圧し、出力切替時に出力位相の変化を抑える。

【解決手段】基準クロックによるリファレンス信号から1/n(nは任意の自然数)倍の第1の周波数信号を生成する1/n分周器11と、それぞれVCXO121,131の出力信号から1/m(mは任意の自然数)倍の第2の周波数信号を生成して1/n分周器11で生成される第1の周波数信号と位相比較し、その位相比較結果に基づいてVCXO121,131の出力周波数を制御するPLL回路部11,12と、PLL回路部11,12の出力を選択的に導出する出力選択スイッチ14とを具備する。

(もっと読む)

遅延同期ループ回路

【課題】外部クロック信号が擾乱したとき、擬似ロックを検出し初期化したとき、電源を投入したとき、いずれの場合も確実にロックはずれを防止でき、レイアウトがコンパクトなDLL回路を提供する。

【解決手段】遅延同期ループ回路であって、入力クロックを、制御電圧の大きさに応じて遅延させて帰還クロックを出力する電圧制御遅延手段と、帰還クロックと基準クロックとを比較して位相差を検出し、該位相差に応じて、制御電圧を上昇させるための上昇信号と該制御電圧を下降させるための下降信号とを出力する位相比較器と、上昇信号と下降信号とに応じて制御電圧を決定し、電圧制御遅延手段に出力する制御電圧生成手段と、基準クロックと電圧制御遅延手段からの中間クロックとの論理和に基づき位相比較器をリセットする。

(もっと読む)

クロックデータリカバリ回路及び表示装置

【課題】クロックデータリカバリにおいて擬似ロック発生の検出に要する時間を短縮すること。

【解決手段】クロックデータリカバリ回路は、レシーバ回路と、PLL回路と、擬似ロック検出回路とを備える。レシーバ回路は、所定のパターンを含むシリアルデータを受け取り、クロック信号に同期してシリアルデータをサンプリングしてサンプルドデータを生成する。PLL回路は、サンプルドデータに基づいてクロックデータリカバリを行い、クロック信号を生成する。ここで、擬似ロックパターンとは、PLL回路の擬似ロックが発生している場合にレシーバ回路が上記所定のパターンをサンプリングする結果得られるパターンである。擬似ロック検出回路は、サンプルドデータに含まれる擬似ロックパターンを検出することによって、PLL回路の擬似ロックを検出する。

(もっと読む)

デジタルロック検出装置及びこれを含む周波数合成器

【課題】デジタルロック検出装置及びこれを含む周波数合成器を提供すること。

【解決手段】本発明の一側面は、複数の制御ビートの入力を受け、複数の制御ビートのロッキング(Locking)の可否を通報するビート信号を生成し出力する比較部と、ビート信号から複数の遅延信号を生成した後、複数の遅延信号とビート信号を結合して1つのクロック信号を出力する遅延セルブロックと、クロック信号の遷移時点を検出し、その検出結果を反映するロック表示信号を生成する検出部を含むデジタルロック検出装置及びこれを用いた周波数合成器を提供することができる。

(もっと読む)

広帯域PLL発振回路

【課題】周波数逓倍回路を含む広帯域PLL発振回路において、逓倍回路出力端に高調波等の不要周波数信号を除去するフィルタを必要とせず、簡単な構成によって不要周波数信号に起因して間違った周波数に同期することなく、安定した動作が得られる広帯域PLL発振回路を提供する。

【解決手段】

逓倍回路に同調周波数制御機能を備え、発振周波数に応じて適切な同調周波数になるように制御する。また、PLLロックインまでの時間短縮のためにメモリに記憶した制御電圧情報をVCOに印加する機能を備え、この制御電圧情報によって同時に逓倍回路の同調周波数を制御する。

(もっと読む)

タイミングリカバリー回路

【課題】 構成を簡易にし、同期クロックのずれを小さくしたタイミングリカバリー回路を提供する。

【解決手段】 クロック入力信号に対するデータ入力信号の位相差を検出して位相差信号を出力すると共に異常時に異常信号を出力し、データ入力信号に特定期間変化がない場合に擬似信号を供給する位相比較器100と、VCXO109の制御電圧の中間値若しくはその付近の値の電圧が定電圧として供給され、平滑化された位相差信号と定電圧とを比較し、両信号の差分によりクロック入力信号に対するデータ入力信号の位相が進んでいる場合は位相を遅らせる制御電圧を、位相が遅れている場合は位相を進める制御電圧をVCXO109に出力するオペアンプ105と、オペアンプ105の位相差信号の入力端子とVCXO109の入力端子との接続を、異常信号によりオンにするスイッチ104とを有するタイミングリカバリー回路である。

(もっと読む)

デッドロック検出回路およびデッドロック復帰回路

【課題】誤検出することなく、デッドロック状態を正確に検出することができるデッドロック検出回路を提供する。

【解決手段】デッドロック検出回路は、PLL回路のデッドロック状態を検出するものであり、PLL回路の電圧制御発振器の出力信号を分周して、第1の分周クロックを出力するPLL内蔵分周器と、電圧制御発振器の出力信号を分周して、PLL回路の位相比較器へのフィードバッククロックとなる第2の分周クロックを出力するフィードバック分周器と、第1の分周クロックの周期によって決定される所定の期間に含まれる、第2の分周クロックのクロック数に基づいて、デッドロック状態であるか否かを表す判定信号を出力する誤ロック検出回路とを備えている。

(もっと読む)

DLL回路及びこれを備える半導体装置

【課題】エイリアシングによるエイリアシングによる誤動作の発生が防止されたDLL回路を提供する。

【解決手段】外部クロック信号CLKを遅延させることによって内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110の遅延量を設定するカウンタ回路130と、外部クロック信号CLKの位相に基づいて位相判定信号PD0を生成する位相検出回路140と、外部クロック信号CLKに含まれるジッタ成分が所定の周波数以上であることに応答して、位相判定信号PDに基づいたカウンタ回路130のカウント値の更新を禁止するアンチエイリアス回路200とを備える。これにより、エイリアシングによる誤動作によって内部クロック信号LCLKが誤った方向に連続制御されるという問題がなくなる。

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、短いロッキングタイムを有する多相DLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、 基準クロックを遅延させてDLLクロックを生成するが、制御電圧のレベルに応じて遅延量を調整する遅延手段;制御電圧の初期レベルを制御し、検出イネーブル信号を生成する初期動作制御手段;及び、検出イネーブル信号に応じて前記基準クロック及びDLLクロックの位相を比較して、制御電圧を生成する遅延制御手段を含むことを特徴とする。

(もっと読む)

DLL回路

【課題】本発明は、電圧制御発振部を用いて多相クロックを生成し、そのうちで基準クロックに同期されるクロックを選択して、遅延クロックとして提供するDLL回路を提供する。

【解決手段】本発明は、基準クロックを単位時間だけ遅延させて複数の多相クロックを生成し、複数の多相クロックの何れか一つと基準クロックとの周波数が一致する時にイネーブルされるイネーブル信号を生成するように構成される多相クロック生成部;及び、イネーブル信号がイネーブルされると、制御信号により複数の多相クロックの何れか一つを所定時間遅延させて基準クロックの位相と比較し、複数の多相クロックのうち、基準クロックと位相が一致する多相クロックを遅延クロックとして生成するように構成される多相クロック選択部を含むことを特徴とする。

(もっと読む)

遅延同期ループ回路および表示装置

【課題】所望の単位遅延回路の1個分の遅延追加がなされた場合であっても不安定な単位遅延回路が連続しないようにすること。

【解決手段】本発明は、外部クロックと内部クロックとの位相差を比較する位相比較器1と、位相比較器1からの出力信号により遅延時間を制御するアップダウンカウンタ2と、外部クロックの遅延を制御して内部クロックとするため、アップダウンカウンタ2から出力される信号の複数ビットに対応した複数個の単位遅延回路(Delay-Cell)を備え、この複数個のDelay-Cellを直列に接続するにあたり、アップダウンカウンタ2からの出力における同一ビットの出力により制御されるDelay-Cellが隣り合わないよう接続されるデジタル遅延ライン3とを有する遅延同期ループ回路である。

(もっと読む)

半導体集積回路

【課題】動作モードによって周波数変調を行うか行わないかを選択することによって受信側の負荷を低減することができる半導体集積回路を提供すること。

【解決手段】半導体集積回路1は、2以上の内部回路(ビデオデコーダ11、CPU12など)と、所定の周波数のクロックを発生するPLL31と、周波数を変調させたクロックを発生するSSCG PLL32と、内部回路にPLL31からのクロックか、SSCG PLL32からのクロックのいずれかを選択して内部回路に入力するセレクタ21とを有する。

(もっと読む)

PLL回路

【課題】 発振起動時におけるデッドロック状態の誤認を防止することができるとともに、発振起動終了後においてデッドロック状態に陥った場合であっても正常なロック状態に復帰することができるPLL回路を提供する。

【解決手段】 PLL回路1がデッドロック状態に陥ったことを検出し、電圧制御発振器50の出力信号OUTの発振周波数を制御するコントロール信号CNTの電圧レベルが低下するように、位相比較器10から出力される制御信号UPI,DOUN1を制御するデッドロック検出回路70と、ロジック回路60からのフィードバック信号DivCLKが所定の閾値周波数未満の周波数にある状態からその閾値周波数を越えたことを検出してデッドロック検出回路70を作用させる起動検出回路80を備えた。

(もっと読む)

1 - 20 / 56

[ Back to top ]