Fターム[5J500AK05]の内容

Fターム[5J500AK05]に分類される特許

201 - 220 / 1,226

差動増幅回路、増幅回路及び液晶ディスプレイドライバ

【課題】差動対が線形領域で高精度に動作する差動増幅回路、増幅回路及びこの差動増幅回路を用いた液晶ディスプレイドライバを提供する。

【解決手段】差動増幅回路は、入力電圧V1がゲート端子に与えられるトランジスタM1及びM2と、トランジスタM1、M2のソース端子に出力端が接続される差動対D1、D2と、差動対D1内のトランジスタM3、M4の共通ソース端子に電流を供給する可変電流源I1と、差動対D2内のトランジスタM5、M6の共通ソース端子に電流を供給する可変電流源I2と、を備え、トランジスタM3のゲート端子には入力電圧V2、トランジスタM5のゲート端子には入力電圧V1、トランジスタM4及びM6のゲート端子には入力電圧V3が与えられる。

(もっと読む)

ピークホールド回路、およびこのピークホールド回路を含む出力電圧制御回路

【課題】スピーカアンプに動作電圧を供給する電源回路の出力電圧をそのスピーカアンプの稼動状況に応じて制御する出力電圧制御回路を小型化することを可能にする技術を提供する。

【解決手段】正の電圧BVDDと接地電圧VSSの供給を受け、正の電圧VPPと負の電圧VMMの電位差を各スピーカアンプに動作電圧として供給する電源の作動制御を行う出力電圧制御回路に含まれるピークホールド回路を以下のように構成する。すなわち、ソースが共通接続された3つのPチャネルFET(電界効果トランジスタ)であって、ドレインに出力電圧VMMが、ゲートに各スピーカアンプの出力電圧が与えられる第1および第2のPチャネルFETと、ドレインとゲートに接地電圧VSSが与えられる第3のPチャネルFETを含み、それらソースの共通接続点に現れる電圧を出力するピークホールド回路。

(もっと読む)

電流電圧変換合成出力装置

【課題】負帰還回路を用いずにDAコンバーターの電流出力を電圧出力に高精度で変換しプッシュプル合成して高品質の信号出力を得る、構成簡易で安価な電流電圧変換合成出力装置。

【解決手段】夫々エミッタ入力・ベース電圧固定(接地)・コレクタ出力動作の第1、第2のトランジスタQ10、Q11と、第1〜第3のカレントミラー回路CM1〜CM3を組み合わせて用いる。 カレントミラー回路CM1、CM2は夫々トランジスタQ10、Q11の各コレクタ出力をカレントミラー電流出力する。カレントミラー回路CM3はカレントミラー回路CM1の出力をカレントミラー電流出力する。カレントミラー回路CM2、CM3の各出力の共通接続点とGND間に、抵抗とコンデンサの並列回路が接続される。DAコンバーターからの互いに極性が逆の電流出力信号を、各トランジスタQ10、Q11のエミッタに入力し、カレントミラー回路CM2、CM3の各出力の共通接続点に電流電圧変換された電圧出力信号を得る。

(もっと読む)

差動増幅回路及び液晶ディスプレイドライバ

【課題】線形領域で高精度に動作する差動増幅回路及びこの差動増幅回路を用いた液晶ディスプレイドライバを提供する。

【解決手段】差動増幅回路は、入力電圧V1がゲート端子に与えられるトランジスタM1及びM2と、トランジスタM1のソース端子にドレイン端子が接続されるトランジスタM3、トランジスタM3のゲート端子に入力電圧V1を与えるか否か切り替えるスイッチS1、トランジスタM3のゲート端子に入力電圧V2を与えるか否か切り替えるスイッチS2、及びトランジスタM2のソース端子にドレイン端子が接続され、ゲート端子に入力電圧V3が与えられ、ソース端子がトランジスタM3のソース端子と接続されるトランジスタM4をそれぞれ有する複数の差動対D1〜D4と、差動対D1〜D4のトランジスタM3、M4のソース端子に電流を供給する電流源I1と、を備える。

(もっと読む)

電力増幅回路

【課題】電源の供給が停止された際に安定に立ち下がる電力増幅回路を提供する。

【解決手段】電力増幅回路は、入力信号を増幅する増幅回路と、増幅回路を駆動するためのバイアス電流を生成するバイアス電流回路と、電源電圧が所定レベルよりも低くなると、増幅回路が発振することを防ぐべくバイアス電流回路にバイアス電流の生成を停止させる制御回路と、を備える。

(もっと読む)

充電回路、増幅回路

【課題】消費電力及びノイズを抑制しつつ、昇圧電圧でコンデンサを早く充電可能な充電回路を提供する。

【解決手段】充電回路は、入力されるクロック信号の周波数の上昇に応じて短くなる時間間隔ごとに入力電圧を昇圧した昇圧電圧を生成するチャージポンプ回路と、昇圧電圧を積分してコンデンサに印加する積分回路と、第1クロック信号がクロック信号としてチャージポンプ回路に入力される際にコンデンサの充電電圧が所定レベルとなるまでの時間よりも短い時間で充電電圧が所定レベルとなるよう、第1クロック信号より高い周波数の第2クロック信号をクロック信号としてチャージポンプ回路に出力した後に、第1クロック信号をクロック信号としてチャージポンプ回路に出力するクロック信号出力回路と、を備える。

(もっと読む)

プッシュプル増幅器

【課題】無負荷時の電流を増加させることなく、より大きな出力電流を得ることができるプッシュプル増幅器を提供する。

【解決手段】差動増幅器1、差動増幅器1の出力信号が入力信号として供給される中間回路4、互いに極性の異なるPMOSトランジスタ2、NMOSトランジスタ3を含む相補型のMOSトランジスタ対を有し、PMOSトランジスタ2、NMOSトランジスタ3が差動増幅器1の出力信号と中間回路4の出力信号とをそれぞれ入力してプッシュプル増幅を行う出力増幅回路15と、差動増幅器1及び中間回路4の出力信号の少なくとも一方を入力し、入力された信号に基づいてPMOSトランジスタ2、NMOSトランジスタ3のウェル電圧を制御するためのウェル電圧制御信号を生成し、PMOSトランジスタ2、NMOSトランジスタ3に供給するウェル電圧制御回路5によってプッシュプル増幅器を構成する。

(もっと読む)

差動増幅器およびその制御方法

【課題】高スルーレートの差動増幅器を提供する。

【解決手段】差動増幅器は、差動入力信号を受ける差動対トランジスタ(TN12/TN13、TP12/TP13)と、定電流源(ICS11、ICS12)と、スイッチ(TN11、TP11)とを具備する。定電流源(ICS11、ICS12)は、差動対トランジスタ(TN12/TN13、TP12/TP13)に流れる電流を制御する。スイッチ(TN11、TP11)は、定電流源(ICS11、ICS12)と並列に配置され、差動入力信号の反転動作に同期して差動入力信号の反転動作の遷移時間より短い時間だけ差動対トランジスタTN12/TN13、TP12/TP13)に流れる電流を増加する。

(もっと読む)

光受信器

【課題】帰還抵抗を極端に大きくすることなく、高感度に広帯域な動作を実現できる光受信器を提供する。

【解決手段】同一極性方向に直列接続された2個の受光素子より構成されたバランスドフォトダイオードと、このバランスドフォトダイオードの出力信号が入力されるチェリーホッパー型増幅部と、このチェリーホッパー型増幅部を構成している差動入力ペアトランジスタからのそれぞれの出力信号をレベルシフトするエミッタフォロワ部と、このエミッタフォロワ部の出力信号を前記チェリーホッパー型増幅部の各入力端子に帰還する経路に設けられた第1および第2の帰還抵抗と、この第2の帰還抵抗と前記チェリーホッパー型増幅部を構成している差動増幅回路の一方のトランジスタのベースに接続されている第1のコンデンサとを有することを特徴とする。

(もっと読む)

電流電圧変換回路、光学機器、及び光学ドライブ装置

【課題】ゲインを大きくする場合のノイズの増加及び狭帯域化を抑制する。

【解決手段】電流電圧変換回路は、フォトダイオード1から出力される電流信号を増幅する第1の差動増幅回路10と、第1の差動増幅回路10の出力信号を増幅する第2の差動増幅回路20と、第2の差動増幅回路20の出力信号が入力される反転入力端子を有するオペアンプ30と、オペアンプ30の反転入力端子と出力端子の間に接続された帰還抵抗31とを備える。

(もっと読む)

電力増幅器

【課題】多段接続される増幅器からのバイアス電流の逆流に起因するバイアス変動を効果的に抑制し、安定して信号増幅できる電力増幅器を提案する。

【解決手段】電力増幅器11は、多段接続されるトランジスタTr1,Tr2,Tr3を備え、これらのトランジスタTr1,Tr2,Tr3は、トランジスタTr1,Tr2を含む第一のグループと、最終段のトランジスタTr3を含む第二のグループとにグループ分けされる。バイアス回路31は、第一のグループに属するトランジスタTr1,Tr2にバイアス電流Ib1,Ib2を分岐供給する。バイアス回路32は、第二のグループに属するトランジスタTr3にバイアス電流Ib3を供給する。

(もっと読む)

誤差増幅器

【課題】誤差増幅器における、受動素子の定数のばらつきに起因する帰還回路の定数のばらつきを抑制する。

【解決手段】誤差増幅器における帰還回路の定数が、受動素子の定数だけでなく、能動素子の利得にも依存して決定される構成にする。この誤差増幅器は、能動素子である電圧電流変換器20を含む構成である。また、第1の端子11、第2の端子13、オペアンプ16、第1の抵抗R1、第2の抵抗R2、第1乃至第5のトランジスタ、第1の電流源14および第2の電流源15を一体の集積回路とし、コンデンサC1を外付けしてもよい。

(もっと読む)

演算増幅器

【課題】極力小さな入力端子間電位差で、スルーレートを増大可能とする。

【解決手段】差動接続された第1及び第2のトランジスタ11,12の差動接続部分に第1の定電流源3が接続される一方、第1及び第2のトランジスタ11,12の差動接続部分と反対側に、カレントミラーを構成する第3及び第4のトランジスタ13,14が接続される一方、第1のトランジスタ11とダーリントン接続される第5のトランジスタ15が設けられると共に、そのダーリントン接続に電流供給可能に第2の定電流源4が設けられ、第2のトランジスタ12とダーリントン接続される第6のトランジスタ16が設けられると共に、そのダーリントン接続に電流供給可能に第3の定電流源5が設けられ、さらに、第5のトランジスタ15と差動対をなす電流補償用トランジスタ17が設けられ、その入力及び出力は、第2のトランジスタ12と同一に接続されてなるものである。

(もっと読む)

低ドロップアウト線形レギュレータ(LDO)、LDOを提供するための方法、およびLDOを動作させるための方法

【課題】PSRRが改良された低ドロップアウト線形レギュレータを提供する。

【解決手段】LDOは、差動増幅器と調整されたカレントミラーとを結合し、それぞれ差分信号を受信するように構成された2つのノードを有する。調整されたカレントミラーは、差分信号をシングルエンド信号に変換および増幅するように構成される。LDOは、周波数補償用に構成された第1のコンデンサを有し、第1のコンデンサは、第1の段と第2の段との間に結合される。LDOは、第1のカスコード回路の容量性負荷を平衡化するための第2のコンデンサを有し、第2のコンデンサは、第1の段と電源電圧との間に結合される。第1のカスコード回路は、電源電圧の変動によって生じるコンデンサの入出力間の差電圧を抑制するように構成される。LDOは、差動増幅器の電源の変動を抑制するように構成された第2のカスコード回路を有する。

(もっと読む)

スイッチトキャパシタ型積分器

【課題】待機電流を抑制することによって、低消費電力のスイッチトキャパシタ型積分器を実現する。

【解決手段】φ1において入力信号の電荷をサンプリングするサンプルキャパシタC1と、φ2においてサンプルキャパシタC1の電荷を仮想ノード4を介して累積する蓄積キャパシタC2と、蓄積キャパシタC2にサンプルキャパシタC1の電荷を供給する主トランジスタMP1,MN1と、主トランジスタMP1,MN1のゲート端子と仮想接地ノード4の間に挿入された校正キャパシタC3,C4と、φ1において校正キャパシタC3,C4に対して、仮想ノード4が基準電位Vcmにあるときの主トランジスタMP1,MN1のゲート・ソース間電圧が略閾値電圧となる電位差が生じるように電荷を供給する校正装置12と、を有する。

(もっと読む)

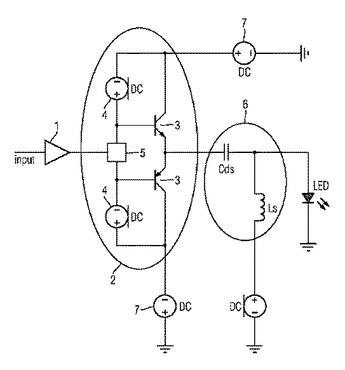

高い出力性能とコンパクトな構造を有する広帯域高線形性LED増幅器

本発明は、発光ダイオードを駆動制御する増幅回路に関する。この増幅回路は、約3オームの小さい出力インピーダンスと、200KHzの下方境界周波数と例えば5MHzの上方境界周波数とを備えた広い帯域幅と、例えば数100mAの出力電流振幅とを有する。この増幅回路は、直流電流供給部(6)によって発光ダイオードを駆動制御するドライバー回路(2)を駆動制御する入力段を有している、という特徴を有している。  (もっと読む)

(もっと読む)

電荷信号をデジタル信号に変換するためのデジタル電荷増幅器および方法

本発明は、圧電測定素子によって出力された正および負の電荷信号Qを測定素子における現在の測定値に比例するデジタル信号Dに変換するための電荷増幅器回路に関する。回路は、検出された電荷Qを電圧U2に変換するための電荷入力および電圧出力を有する電荷増幅器V1を含み、2つの出力を有する補償回路Kが電荷増幅器V1の電圧出力の下流に接続されており、第1の出力は、電荷増幅器V1の電荷入力につながれ、第2の出力は、2つの入力Z+およびZ−を有するカウンタZに接続されている。一方で補償回路Kは、電圧U2に比例する補償電荷Qk+またはQk−を生成することができ、それは、第1の出力によって電荷増幅器V1の電荷入力へ送られて入力信号Qを補償することができ、また他方で補償回路は、生成された各々の補償電荷Qk+またはQk−の大きさに比例する複数のパルスP+、P1を生成することができる。前記パルスは、第2の出力によって補償電荷Qk+またはQk−と逆符号のカウンタZの入力Z−、Z+へ送ることができ、それまでに入力された電荷量子の和に比例する所望のデジタル信号DがカウンタZの出力に得られる。本発明は、さらにそのような回路上で実行される方法に関する。  (もっと読む)

(もっと読む)

出力駆動回路

【課題】出力信号が不安定になる可能性があった。

【解決手段】第1、第2の電源間に直列接続される第1、第2のトランジスタを備えた出力部と、入力パルス信号に応じて、前記第1のトランジスタがオン状態となるとき、前記第1の電源端子と前記第1のトランジスタの制御端子を導通させオン状態に駆動させる第1の駆動部と、一端が第1のノードとの間に接続されるインダクタと、前記第1のスイッチング素子の少なくともオフ後にオン状態となることで、前記第1のノードと前記第1のトランジスタの制御端子を導通し、前記第1の所定の期間後に前記第1のノードに供給される前記インダクタの逆起電力を、前記第1のトランジスタの制御端子に伝達する第2のスイッチング素子と、を有する出力駆動回路。

(もっと読む)

振幅制限増幅回路

【課題】差動出力信号間のオフセット電圧を充分に抑圧し、出力信号のデューティ比の悪化を防ぐこと。

【解決手段】差動振幅制限増幅器30と、該差動振幅制限増幅器の出力差動信号をオフセット電圧抑制のために前記差動振幅制限幅器の入力側にフィードバックする差動アクティブ・ローパスフィルタ回路40と、からなる回路を、2段以上に亘って縦続接続したて構成する。

(もっと読む)

送信回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる送信回路、集積回路装置及び電子機器等を提供すること。

【解決手段】送信回路100は、電圧制御発振回路190を有し、搬送波の信号を生成するPLL回路110と、送信データDTXに基づいて、電圧制御発振回路190の変調用制御電圧信号入力ノードNBに対して、変調用制御電圧信号VMを出力する変調用制御電圧生成回路120と、電圧制御発振回路190の出力信号を増幅するパワーアンプ210とを含む。変調用制御電圧生成回路120は、送信データ出力期間の前の擬似信号出力期間に、擬似制御電圧信号を変調用制御電圧信号VMとして出力する。

(もっと読む)

201 - 220 / 1,226

[ Back to top ]