Fターム[5J500AK11]の内容

Fターム[5J500AK11]に分類される特許

1 - 20 / 216

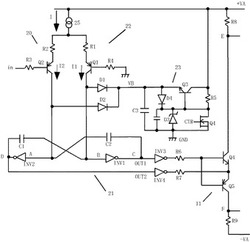

パルス幅変調回路およびスイッチングアンプ

【課題】 電源オフ状態に移行する際に、漏れ電流によって蓄積手段が充電され、2つの出力素子の入力が共にハイレベルになり、出力が共にローレベルになり、次に電源オン状態に移行する際に、パルス幅変調動作を開始することができないとい問題を解決でき、かつ、入力信号に正確に対応したパルス幅変調信号を出力することができるパルス幅変調回路を提供する。

【解決手段】 パルス幅変調回路20は、電源オン状態から電源オフ状態に移行する際に、オン状態に制御されることにより、漏れ電流の原因となる電源電圧V2を接地電位に瞬時に放電させ、0Vにさせるスイッチ手段Q4を備える。スイッチ手段Q4は、ダイオードD1、D2の各カソード側に接続されているので、電流I1、I2によってコンデンサC1、C2を充電する際に、コンデンサC1、C2から電気的に分離された状態になるので、C1、C2の充電に誤差を与えない。

(もっと読む)

D級増幅回路

【課題】D級増幅回路において、確実に電源パンピングの影響をキャンセルする。

【解決手段】第1スイッチ61がオン、第2スイッチ63がオフの時に、電源電圧VDDと接地間の電流をコンデンサ62に充電させ、第1スイッチ61がオフ、第2スイッチ63がオンの時に、コンデンサ62の電圧と基準電圧Vrとをコンパレータ64により比較する。コンパレータ64の出力をパワーリミット回路30に入力し、コンデンサ62の電圧が基準電圧Vrを超える場合には、PWM変調回路20からの出力信号のパルス幅を制限する。

(もっと読む)

基準電圧発生回路

【課題】小規模の付加回路により、基準電圧の温度特性を簡易な調整によって十分に改善することができる基準電圧発生回路を提供する

【解決手段】バイポーラトランジスタ106、バイポーラトランジスタ106と並列に接続されるバイポーラトランジスタ107、バイポーラトランジスタ107のエミッタに一端が接続される抵抗素子104、バイポーラトランジスタ106のベース電位と、バイポーラトランジスタ107のベース電位との差分によって生じる差電圧を発生させる抵抗素子109、バイポーラトランジスタ106のエミッタ電位と抵抗素子104の他端の電位とが等しくなるように動作する演算増幅器105によって基準電圧発生回路を構成し、抵抗素子109が生成する差電圧が、温度によって変化する。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】第1バッファ10の電源端子には、第1電源からの第1電源電圧VCC1が供給される。第2バッファ12の電源端子には、第1電源からの第1電源電圧VCC1が供給される。非反転アンプ14の電源端子には、第2電源電圧VCC2が供給される。起動電圧源16は、その電源端子に第2電源電圧VCC2を受け、起動電圧VSTARTを生成する。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW1をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW1をオフする。

(もっと読む)

センサ信号処理装置

【課題】簡単な構成で入力オフセット電圧の温度依存性が小さいセンサ信号処理装置を提供する。

【解決手段】センサ用電源として第1の電源電圧V´ccを供給されて動作し、センサ出力Vs1、Vs2を出力するセンサ部100と、信号処理用電源として第2の電源電圧Vccを供給されて動作し、センサ出力Vs1、Vs2が入力される差動対を使用する差動増幅部を有して信号処理を行なう信号処理部200と、を有してセンサ信号処理装置1を構成する。この第1の電源電圧V´ccは、信号処理部200の差動増幅部250の入力電圧範囲の下限領域に設定される。

(もっと読む)

受信回路

【課題】正の単一電源で作動(動作)するオペアンプを用いて負の信号レベルの信号を含む受信信号を増幅することのできる受信回路を提供する。

【解決手段】受信回路100は、基準端子11と基準端子11の電圧を基準とする受信信号を出力する信号端子12とを有する信号部10と、正の入力端子21と負の入力端子22と出力端子23とを有し、正の単一電源E2から電圧が印加されて作動するオペアンプ20と、出力端子23と負の入力端子22との間に接続される第1負荷部30と、信号端子12と負の入力端子22との間に接続される第2負荷部40と、カソード側が接地され、アノード側が基準端子11と正の入力端子21とに接続されるダイオード52を含む基準電圧部50と、を備える。

(もっと読む)

受光回路

【課題】受光回路の消費電流を削減する。

【解決手段】一つの実施形態によれば、受光回路は、トランスインピーダンスアンプと出力回路が設けられる。トランスインピーダンスアンプは、フォトダイオード、帰還抵抗、及び第1のトランジスタが設けられる。フォトダイオードは、光信号を電気信号に変換する。帰還抵抗は、フォトダイオードと内部出力端子の間に設けられる。第1のトランジスタは、ゲートにフォトダイオードで光電変換された電気信号が入力され、ドレインが内部出力端子に接続される。出力回路は、第1のトランジスタと同一チャネル型であり、ゲートが内部出力端子に接続され、電流源負荷が接続されるとともにドレイン側から出力信号を出力する第2のトランジスタを含む。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

電力増幅器のバイアス回路および電力増幅器

【課題】コンプリメンタリSEPP回路において、出力抵抗を高くすることなくバイアス電流の安定したバイアス回路を提供する。

【解決手段】バイアス電流を検出する差動増幅器と、所定の電圧値と差動増幅器の出力電圧値との差分を増幅する演算増幅器と、演算増幅器の出力信号を絶縁伝達する絶縁伝達器と、絶縁伝達器の出力に応じたバイアス電圧を出力するバイアス電圧源とを備えたコンプリメンタリSEPP回路のバイアス回路。差動増幅器、演算増幅器、絶縁伝達器の動作により、バイアス電圧源は、バイアス電流が増加すると出力するバイアス電圧を低下させる。

(もっと読む)

バイアス回路及び増幅回路

【課題】低電圧までの広い電圧範囲で動作可能で、バイアス電流の温度係数を設定可能なバイアス回路及び増幅回路を提供する。

【解決手段】電流生成回路と、電圧生成回路と、を備えたことを特徴とするバイアス回路が提供される。前記電流生成回路は、接合部の面積の異なる2つのPN接合の順方向電圧の電圧差に基づいて第1の電流を生成し、前記2つのPN接合のうちの接合部の面積の小さいPN接合の順方向電圧に基づいて前記第1の電流の温度係数と異なる極性の温度係数を有する第2の電流を生成する。前記電圧生成回路は、前記第1の電流と前記第2の電流とを合成した電流から基準電圧を生成する。

(もっと読む)

増幅装置、増幅システムおよび電流電圧変換装置

【課題】適切にオフセット電圧をキャンセルすることが可能な増幅装置、増幅システムおよびこれを用いた電流電圧変換装置を提供する。

【解決手段】実施形態によれば、増幅装置は、メインアンプと、第1のサブアンプと、第2のサブアンプとを備える。前記メインアンプは、第1の入力電圧と第2の入力電圧との差を増幅した電圧を出力する。前記第1のサブアンプは、入力端子同士を短絡したときの出力電圧に基づいて自身のオフセットキャンセルを行い、前記第1の入力電圧および前記第2の入力電圧が入力されたときの出力電圧に基づいて前記メインアンプのオフセットキャンセルを行う。前記第2のサブアンプは、入力端子同士を短絡したときの出力電圧に基づいて自身のオフセットキャンセルを行い、前記第1の入力電圧および前記第2の入力電圧が入力されたときの出力電圧に基づいて前記メインアンプのオフセットキャンセルを行う。

(もっと読む)

受光増幅回路及びそれを用いた光ピックアップ装置

【課題】光ディスクの高倍速化により高い周波数応答特性が必要な場合においても、RF信号成分の信号振幅を低下させない受光増幅回路を提供することを目的とする。

【解決手段】入力された光電流を電圧に変換するとともに、変換した電圧のうち第1カットオフ周波数より低い周波数に対応する電圧のみを出力する電流電圧変換アンプ102と、電流電圧変換アンプ102の後段に接続され、電流電圧変換アンプ102から出力された電圧のうち第2カットオフ周波数より低い周波数に対応する電圧のみを出力するCRローパスフィルタ回路103と、CRローパスフィルタ回路103の後段に接続され、CRローパスフィルタ回路103から出力された電圧を増幅する電圧増幅アンプ104と、少なくとも電圧増幅アンプ104と接続され、電圧増幅アンプ104から出力された電圧を加算増幅するRF増幅加算アンプ105と、を備える。

(もっと読む)

電力増幅器

【課題】出力電力に応じて高電力モードおよび低電力モードを切り替え可能で、FETの製造ばらつきを両モードで補償可能な電力増幅器を提供する。

【解決手段】本発明の電力増幅器によれば、高電力モードおよび低電力モードで回路状態を切り替えることによって、バイアス回路部に供給される基準電圧を切り替え、トランジスタのばらつきを補償する。低電力モードでは電源電圧が基準電圧の1/2となるように調整し、高電力モードでは基準電圧をバイアス回路部に伝達する抵抗の値を調整することでアイドル電流の調整を実現する。

(もっと読む)

半導体装置

【課題】シングルエンド−差動変換器を備えた半導体装置において、理想的な出力差動電流特性が得られる周波数の上限を向上させる。

【解決手段】入力電圧Vinを、パッケージ3の外部電極PIN1に入力し、外部電極PIN1、ボンディングワイヤWire1、チップ2の入力端子PAD1、シングルエンド−差動変換器1の入力端子Tin1を介してゲート接地のMOSトランジスタM1のソースに伝達する。また、外部電極PIN1、ボンディングワイヤWire2、チップ2の入力端子PAD2、シングルエンド−差動変換器1の入力端子Tin2を介してソース接地のMOSトランジスタM2のゲートに伝達する。

(もっと読む)

電圧レギュレータ回路

【課題】複雑な制御を必要とせず、集積回路のトランジスタの閾値電圧バラツキに応じて所望の動作速度に適した電源電圧を提供することができる。

【解決手段】被安定電圧が入力される入力端子1と、安定化された電圧が出力される出力端子2と、入力端子1および出力端子2と電位差を有する一定電圧に設定される共通端子3と、正入力端子および負入力端子を有する差動増幅器4と、差動増幅器4の出力に基づいて入力端子1から出力端子2に流れる電流を制御する電流制御素子5と、出力端子2と共通端子3との間の電位差を分圧し、差動増幅器4の正入力端子に帰還させる分圧回路6と、出力端子2から電力を供給されるが出力端子2の電圧に依存せず、共通端子3の電圧を基準とする当該集積回路のトランジスタの閾値電圧に比例した電圧を差動増幅器4の負入力端子に出力する閾値参照電圧源7とを備える。

(もっと読む)

スイッチングアンプ

【課題】 2つの出力素子の入力が共にハイレベルになり次に電源オン状態に移行する際に動作を開始することができないとい問題を解決する。

【解決手段】 電源制御手段16は、スイッチングアンプ10が電源オフ状態に移行する場合に、スイッチSWがオフ状態になり、コンデンサC102を強制的に放電させ、第2電源電圧V2に対する基準電位V3を強制的に低下させる。基準電位V3に対するロジック電源電圧Vddは、基準電位V3と同じだけ低下していくので、基準電位V3から見たロジック電源電圧Vddは固定される。定電流回路は、第2電源電圧V2に対する基準電位V3の低下に伴い、定電流Iを減少させ、第1の電流I1および第2の電流I2を減少させる。従って、基準電位V3から見たロジック電源電圧Vddが低下しないうちに、第1の電流I1、第2の電流I2を減少させ、パルス発生手段の動作を正常な状態で終了できる。

(もっと読む)

電力増幅器

【課題】 オフセット補正後の電力増幅器の動作開始時に電力増幅器に接続されたスピーカからポップ音が発生するのを防止する。

【解決手段】 直流電圧発生回路170は、D級増幅器内の差動増幅器のオフセットキャンセルを行わせるためにD級増幅器の出力端子T21およびT22に直流電圧を供給する。この直流電圧発生回路170の出力端子T30と接地線との間には放電用抵抗RDISとNチャネルトランジスタ183が介挿されている。オフセットキャンセルが終わった後、D級増幅器の増幅動作が開始される前の安定期間に、Nチャネルトランジスタ183はONとされ、出力端子T21およびT22に接続された容量C1およびC2の充電電荷が放電用抵抗RDISおよびNチャネルトランジスタ183を介して放電される。これによりポップ音の発生を防止することができる。

(もっと読む)

アンプ

【課題】より簡素な構成で電磁誘導等による音質へのノイズの影響を一層低減させる装置を提供すること。

【解決手段】定電圧回路1からの直流電圧を定電圧供給線50および定電圧用アース線51を介して外部機器200側の定電圧回路10に電源供給する場合、定電圧用アース線51、外部機器内の接地点であるgnd部15、信号用アース線56およびアンプ内の接地点であるgnd部2を通るグランドループが形成されてノイズの原因になるが、スイッチ5の操作によって、演算増幅器3の反転端子と接地点(gnd部2)とが非導通状態となって、グランドループが形成されないことになる。この結果、ノイズが低減され音質劣化を防止することが可能になる。

(もっと読む)

高周波増幅回路

【課題】低出力モードで出力電力を変化させても、ゲインの差が殆ど生じない高周波増幅回路を実現する。

【解決手段】高周波増幅回路100Aは増幅用トランジスタ10を備える。増幅用トランジスタ10のベースは、バラスト抵抗素子52を介してエミッタフォロワ用トランジスタ20のエミッタに接続する。エミッタフォロワ用トランジスタ20のベースには、抵抗素子51を介してバイアス電源が接続されている。エミッタフォロワ用トランジスタ20のコレクタには、抵抗素子53を介してモード制御電源が接続されている。抵抗素子53は固定抵抗値の抵抗素子である。モード制御電源は、可変電圧型であり、モードに応じて直流のモード制御電圧Vmodeを発生する。モード制御電圧Vmodeは、低出力モード時には低電圧となり、高出力モード時には高電圧となる。

(もっと読む)

受信回路

【課題】本発明の実施形態は、閾値電圧のオフセットレベルを変化させることにより、チャタリングを抑制することが可能な受信回路を提供する。

【解決手段】実施形態に係る受信回路は、光信号を受信し、前記光信号に対応した光電流を出力する受光素子と、前記光電流を信号電圧に変換して出力する信号電圧生成部と、 前記信号電圧を第1の閾値もしくは第2の閾値と比較する比較器と、前記比較器に入力する基準電圧を出力する基準電圧生成部と、前記比較器の出力に基づいて、前記基準電圧を前記第1の閾値および前記第2の閾値のいずれかに切り替えるスイッチと、を備える。

(もっと読む)

1 - 20 / 216

[ Back to top ]