Fターム[5J500DN14]の内容

増幅器一般 (93,357) | 増幅部構成 (1,575) | 負荷回路構成 (326) | 能動素子を用いるもの(能動負荷) (301) | ベース(ゲート)共通接続能動負荷 (94)

Fターム[5J500DN14]に分類される特許

21 - 40 / 94

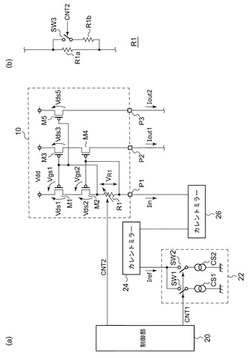

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

アンプ

【課題】第1のアンプと、第1のアンプの出力が入力される第2のアンプとを含むアンプにおいて、ツノが発生せず、安定した動作が行なえるアンプを提供する。

【解決手段】第1のアンプは、ゲートに基準電圧が入力されるトランジスタM1と、トランジスタM1のドレインと電源電圧との間に接続されたトランジスタM4と、トランジスタM1のソースと接地電圧との間に接続された定電流源とから構成されて、トランジスタM1のドレインとトランジスタM4との接続部から出力し、第2のアンプは電源電圧と接地電圧との間で直列に接続されトランジスタM6と少なくとも1つ以上の抵抗から構成されて、トランジスタM6のゲートに第1のアンプの出力が入力されると共に、トランジスタM6と抵抗との接続部から出力電圧を出力し、第1のアンプの出力と電源電圧の間に、ゲートに基準電圧が入力されるトランジスタM7でなるスイッチが設けられている。

(もっと読む)

差動増幅回路、増幅回路及び液晶ディスプレイドライバ

【課題】差動対が線形領域で高精度に動作する差動増幅回路、増幅回路及びこの差動増幅回路を用いた液晶ディスプレイドライバを提供する。

【解決手段】差動増幅回路は、入力電圧V1がゲート端子に与えられるトランジスタM1及びM2と、トランジスタM1、M2のソース端子に出力端が接続される差動対D1、D2と、差動対D1内のトランジスタM3、M4の共通ソース端子に電流を供給する可変電流源I1と、差動対D2内のトランジスタM5、M6の共通ソース端子に電流を供給する可変電流源I2と、を備え、トランジスタM3のゲート端子には入力電圧V2、トランジスタM5のゲート端子には入力電圧V1、トランジスタM4及びM6のゲート端子には入力電圧V3が与えられる。

(もっと読む)

差動増幅回路及び液晶ディスプレイドライバ

【課題】線形領域で高精度に動作する差動増幅回路及びこの差動増幅回路を用いた液晶ディスプレイドライバを提供する。

【解決手段】差動増幅回路は、入力電圧V1がゲート端子に与えられるトランジスタM1及びM2と、トランジスタM1のソース端子にドレイン端子が接続されるトランジスタM3、トランジスタM3のゲート端子に入力電圧V1を与えるか否か切り替えるスイッチS1、トランジスタM3のゲート端子に入力電圧V2を与えるか否か切り替えるスイッチS2、及びトランジスタM2のソース端子にドレイン端子が接続され、ゲート端子に入力電圧V3が与えられ、ソース端子がトランジスタM3のソース端子と接続されるトランジスタM4をそれぞれ有する複数の差動対D1〜D4と、差動対D1〜D4のトランジスタM3、M4のソース端子に電流を供給する電流源I1と、を備える。

(もっと読む)

差動増幅器およびその制御方法

【課題】高スルーレートの差動増幅器を提供する。

【解決手段】差動増幅器は、差動入力信号を受ける差動対トランジスタ(TN12/TN13、TP12/TP13)と、定電流源(ICS11、ICS12)と、スイッチ(TN11、TP11)とを具備する。定電流源(ICS11、ICS12)は、差動対トランジスタ(TN12/TN13、TP12/TP13)に流れる電流を制御する。スイッチ(TN11、TP11)は、定電流源(ICS11、ICS12)と並列に配置され、差動入力信号の反転動作に同期して差動入力信号の反転動作の遷移時間より短い時間だけ差動対トランジスタTN12/TN13、TP12/TP13)に流れる電流を増加する。

(もっと読む)

RFシングルエンド/差動変換器

例えば、通信受信機中で使用するための非常に差動なシングルエンド/差動変換器を設計するための技術。例示的な実施形態では、cascompトランジスタを含む補助電流経路が、入力トランジスタ及びカスコードトランジスタを含む主電流経路に結合される。トランジスタは、補助電流経路によって生成された混近変調ひずみ結果物が主電流経路によって生成された混近変調ひずみ結果物を打ち消すように、バイアスされる。別の例示的な実施形態では、主電流経路の電流源トランジスタは、受信した入力信号のレベルに応じて適応的にバイアスされる。例示的な実施形態では、上記技術は、シングルエンド低雑音増幅器(LNA)出力電圧を、通信受信機の差動混合器入力にインタフェースするための変換器を設計するために適用されることができる。  (もっと読む)

(もっと読む)

プロセス変動に対してスルーレートを補償するためのプリドライバを有する出力バッファ

【課題】補償回路とプリドライバを組み込んでおり、プロセス変動に対して補償されるスルーレートを有する出力バッファを提供する。

【解決手段】補償回路370は、演算増幅器250と、増幅器の出力に結合されたゲートを有する第2のNFET240、第3のNFET371、及び実行抵抗381から構成される。出力バッファ300は、ICチップのコア150がプリドライバ310に制御信号をアサートする。これに応答して、プリドライバ310は、第1のNFET320にバッファリングされた制御信号をアサートし、第1のNFET320をオンにし、VSSレベルの出力信号をパット230にアサートする。

(もっと読む)

演算増幅器

【目的】位相変動を抑制させて安定した動作が可能な演算増幅器を提供することを目的とする。

【構成】第1及び第2入力信号各々に対応した電流を送出する入力段に対して電流を供給する第1トランジスタ、及び、入力段から送出された電流に応じた電位レベルを有する出力信号を生成する出力段に対して電流を供給する第2トランジスタに、夫々バイアス電圧を供給するにあたり、第1トランジスタにバイアス電圧を供給する為の配線と、第2トランジスタにバイアス電圧を供給する為の配線とを互いに電気的に絶縁する。

(もっと読む)

マルチ・モード増幅器

【課題】オペアンプ及びCCIIの双方として機能する単一のアナログ構成要素を実現する。

【解決手段】増幅器100は、差動増幅回路102、非反転出力ステージ104で構成され、差動増幅回路102は、2つの電圧入力を受け取る入力ステージ106と、電流出力を提供する出力ステージ108とを有する。2つの電流出力IOUT1及びIOUT2が一体に結合されたときに、第1のモードであるオペレーショナル増幅器として機能し、第2の電流出力IOUT2が第2の電圧入力VNに結合されるときに、第2のモードであるタイプ2の電流搬送器(CCII)として機能する。

(もっと読む)

差動増幅回路

【課題】高精度且つ広範囲なオフセット調整を可能にする。

【解決手段】差動対に発生するオフセットを調整するために能動負荷を変化させるオフセット調整回路を有する差動増幅回路1であって、同一のトランジスタサイズを有する複数のトランジスタ31a,31b,33a,33bを備えて構成される微調整用セル部21,22と、前記微調整用セル部21,22のトランジスタ31a,31b,33a,33bよりも大きいトランジスタサイズを有するトランジスタ35a,35b,37a,37bを備えて構成されるシフト用セル部23,24とを有して構成される。

(もっと読む)

コンパレータ回路

【課題】フォールデッドカスコード接続の差動増幅段を有するコンパレータにおいて、オフセットの温度依存性を減らし検出精度を向上させる。

【解決手段】ソース共通接続された一対の差動MOSトランジスタを有する差動入力段(11)と、差動MOSトランジスタのドレイン端子にフォールデッドカスコード接続されたカスコード段(12)と、差動入力段とカスコード段に共通に接続された電流回路(Mn11〜Mn13,Mn21〜Mn23)と、カスコード段の出力ノードに接続された出力段(13)とを備えたコンパレータ回路において、前記電流回路は、カスコード段のMOSトランジスタのキャリア移動度の温度特性に起因する動作点の変動をキャンセルするような温度特性を付与された電流を流すように構成した。

(もっと読む)

差動増幅器

【課題】トランジスタの製造ばらつき等があっても、低電源電圧で動作し、広範囲の入力電圧に対してプッシュプル動作の出力電流が得られる差動増幅器を提供する。

【解決手段】差動増幅器1は、第1の導電型のトランジスタで構成され、入力信号を受けて第1の差動電流I11、I12を出力する第1の差動対10と、第1の差動電流I11、I12に基づき、第1の吐き出し側出力電流I18及び第1の吸い込み側出力電流I16をそれぞれ第1の出力端子OP及び第2の出力端子ONに対して出力する第1の電流増幅部11と、第2の導電型のトランジスタで構成され、入力信号を受けて第2の差動電流I1C、I1Dを出力する第2の差動対20と、第2の差動電流I1C、I1Dに基づき、第2の吐き出し側出力電流I1K及び第2の吸い込み側出力電流I1Iをそれぞれ第1の出力端子OP及び第2の出力端子ONに対して出力する第2の電流増幅部21と、を有する。

(もっと読む)

差動入力を有する直交出力低雑音トランスコンダクタンス増幅器

低雑音トランスコンダクタンス増幅を提供するためのデバイスが提示される。前記デバイスは、差動RF入力信号を受信するように構成されたPMOSトランスコンダクタンス部と、前記PMOSトランスコンダクタンス部に結合されたPMOSカスコード部と、前記RF差動入力信号を受信するように構成されたNMOSトランスコンダクタンス部と、前記NMOSトランスコンダクタンス部に結合されたNMOSカスコード部と、を含み、前記PMOSカスコード部及びNMOSカスコード部は、差動直交出力信号及び差動同相出力信号を提供する。RF信号を増幅するための方法も提示される。前記方法は、差動RF入力信号を受信することと、前記差動RF入力信号を電流信号に変換することと、前記電流信号をバッファリングして差動直交出力信号及び差動同相出力信号を提供すること、とを含む。  (もっと読む)

(もっと読む)

オペアンプ回路及びオペアンプ回路の駆動方法

【課題】CMOSオペアンプ回路において、パワーダウン状態の解除後に定常状態に安定するまでの動作速度を高速化することができるオペアンプ回路及びオペアンプ回路の制御方法を提供する。

【解決手段】パワーダウン時はSW1により電圧VDD2をノードN1に印加し、出力端OUT1から電圧VDD2が出力されるため、位相補償用コンデンサC1の両電極に電位差が生じ、電荷が蓄積され、定常状態に切り替わると蓄積されていた電荷が放電され、Nチャネル型MOSトランジスタTN3のゲートがONするため、瞬時に出力端OUT2の出力値が引き下げられた後、安定状態に落ち着く。

(もっと読む)

検出回路

【課題】プロセス変動等によるサンプルごとのしきい値のばらつきを低減させることができ、高速動作を行うことができる、入力検出及び/又は切断検出を行う検出回路を得る。

【解決手段】1対のシリアルデータ信号が対応する入力端に入力される差動増幅回路で構成された第1検出用レシーバ2と、1対のシリアルデータ信号が対応する入力端に入力される差動増幅回路で構成された第2検出用レシーバ3と、対応する入力端に入力された各基準電圧Vrp及びVrmにそれぞれオフセットを加えて出力する差動増幅回路で構成されたリファレンスレシーバ7の各差動増幅回路は、前記各シリアルデータ信号が対応してゲートに入力されるMOSトランジスタからなる1対の入力トランジスタを有し、該各入力トランジスタのサブストレートゲートに電圧差を設けてそれぞれオフセットが設けられるようにした。

(もっと読む)

差動増幅回路

【課題】差動増幅回路のオフセット電圧を小さくする。

【解決手段】本発明の差動増幅回路は、差動入力信号を受け取るNMOSトランジスタ対を備えるN型入力段2と、N型入力段2に接続された出力段4と、前記差動入力信号を受け取るPMOSトランジスタ対を備えるP型入力段3と、P型入力段3に接続された出力段5と、出力端子OUTとを備えている。出力段5は、出力段4に含まれるNMOSトランジスタをPMOSトランジスタに置き換え、PMOSトランジスタをNMOSトランジスタに置き換え、接地端子を電源端子に置き換え、電源端子を接地端子に置き換えた構成を有している。出力端子OUTは、出力段4の出力と出力段5の出力に共通に接続されている。

(もっと読む)

出力装置及び半導体集積装置

【課題】データパターンに関わらず、低消費電流を図ることができる出力装置を提供する。

【解決手段】外部から入力されたデータ信号を差動信号に変換して出力するドライバ回路9からの差動信号を出力する出力装置であって、ドライバ回路9から入力された差動信号を低振幅で差動出力する中継バッファ部11と、中継バッファ部11から出力される差動信号が入力され、振幅を増幅して出力する増幅アンプ部12と、ドライバ回路9に比べて高い駆動力で差動出力をするデータ出力部13とを備える。

(もっと読む)

演算増幅器

【課題】大きいGB積を得ることができる演算増幅器を提供する。

【解決手段】増幅段20は、カレントミラー回路12と差動対11との一方の接続点がゲートに接続される第1のPMOSトランジスタM6と、カレントミラー回路12と差動対11と他方の接続点がゲートに接続されるPMOSトランジスタM8と、PMOSトランジスタM6を駆動させる電流源21と、PMOSトランジスタM6と電流源21との接続点がゲートに接続されるNMOSトランジスタM9とを有し、NMOSトランジスタM9とPMOSトランジスタM8とでプッシュプル出力段を構成する。

(もっと読む)

差動増幅回路

【課題】動作電源電圧マージンを損なう事無く、チップ面積を増大させずに、入力オフセット電圧を小さくすることができる差動増幅回路を提供する。

【解決手段】1対のNチャネルMOSトランジスタM1、M2からなる差動トランジスタ対1と、差動トランジスタ対1のソースに接続された定電流源回路2と、1対のPチャネルMOSトランジスタM3、M4からなるカレントミラー負荷回路3と、カレントミラー負荷回路3の各ドレインの一方の電位と他方の電位を等しくするように、ゲートバイアスおよびドレインバイアスを発生するバイアス発生回路4とを備えている。

(もっと読む)

増幅回路及びこれを備える光ピックアップ

【課題】帰還回路内のスイッチを用いずに電圧増幅度を切り替え可能な増幅回路を提供する。

【解決手段】本発明による増幅回路3bは、差動入力部81A及び81Bと、該差動入力部81A及び81Bのうちのいずれか一方を選択するスイッチ79A及び79Bと、を備え、該スイッチ79A及び79Bにより選択された差動入力部を用いた増幅処理を行うオペアンプ70bと、オペアンプ70bの出力端と差動入力部81Aの入力端との間に設けられ、所定抵抗値の抵抗を有する第1の帰還回路と、オペアンプ70bの出力端と差動入力部81Bの入力端との間に設けられ、上記所定抵抗値とは異なる抵抗値の抵抗を有する第2の帰還回路と、を備えることを特徴とする。差動入力部の選択により電圧増幅度を切り替え可能であるので、帰還回路内のスイッチを用いずに電圧増幅度を切り替え可能となっている。

(もっと読む)

21 - 40 / 94

[ Back to top ]