Fターム[5J500NG01]の内容

Fターム[5J500NG01]に分類される特許

1 - 20 / 170

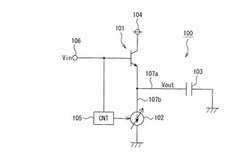

トランジスタ回路

【課題】少ない電流量で出力電圧の歪みを低減できるトランジスタ回路を提供する。

【解決手段】エミッタまたはソースと、コレクタまたはドレインと、これらエミッタまたはソース及びコレクタまたはドレイン間の電流量を制御する電圧が印加されるベースまたはゲートと、を備え、コレクタまたはドレインが容量性負荷103に接続されるバイポーラトランジスタまたはMOSトランジスタと、バイポーラトランジスタまたはMOSトランジスタのコレクタまたはドレインに接続され、電流を供給する機能付電流源102と、ベースまたはゲートに入力される電圧の大きさに応じて機能付電流源102の電流を制御するコントロール回路105と、によってトランジスタ回路を構成する。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

信号変換回路ならびにそれを用いた増幅回路,送信装置および通信装置

【課題】 不要パルスの発生が抑制された信号変換回路およびそれを用いた増幅回路,送信装置,通信装置を提供する。

【解決手段】 第1信号S1がソース端子に、第2信号S2がゲート端子に入力されるトランジスタ7と、第1信号S1と第2信号S2とが入力されて、第1信号S1と第2信号S2との位相差の情報を有する第3信号S3を出力する第1回路5と、第1信号S1と第3信号S3とが入力されて、第1信号S1の位相を所定の値だけシフトさせた位相を有する信号に、第1信号S1と第2信号S2との位相差に応じてバイアス電圧を加えた信号である第4信号S4を出力する第2回路6と、ソース端子がトランジスタ7のドレイン端子に接続されているとともにゲート端子に第4信号S4が入力されて、第1信号S1と第2信号S2との位相差に応じてデューティ比が変化する第5信号S5をドレイン端子から出力するトランジスタ9とを有する信号変換回路とする。

(もっと読む)

適応線形通信デバイス

【課題】バッテリ寿命に対する悪影響を最小にしつつ、受信機コンポーネントの線形性を増大させる。

【解決手段】無線通信デバイス100は、バイアスに依存した線形性を有するコンポーネント116と、無線通信デバイスと大容量電源102との間の接続の検出に応じてバイアスを変更するように構成されたプロセッサ108と、を含むことができる。無線通信デバイスが無線通信デバイスと大容量電源との間の接続のないときに、高効率モードで動作するように構成されている場合のバイアス依存コンポーネントを有する無線通信デバイスを動作させる方法は、大容量電源が無線通信デバイスに接続されているかどうかを決定することと、大容量電源が無線通信デバイスに接続されているかどうかに基づいてバイアス依存コンポーネントのオペレーションを変化させることと、を含むことができる。

(もっと読む)

受信回路

【課題】正の単一電源で作動(動作)するオペアンプを用いて負の信号レベルの信号を含む受信信号を増幅することのできる受信回路を提供する。

【解決手段】受信回路100は、基準端子11と基準端子11の電圧を基準とする受信信号を出力する信号端子12とを有する信号部10と、正の入力端子21と負の入力端子22と出力端子23とを有し、正の単一電源E2から電圧が印加されて作動するオペアンプ20と、出力端子23と負の入力端子22との間に接続される第1負荷部30と、信号端子12と負の入力端子22との間に接続される第2負荷部40と、カソード側が接地され、アノード側が基準端子11と正の入力端子21とに接続されるダイオード52を含む基準電圧部50と、を備える。

(もっと読む)

増幅装置、送信装置

【課題】出力信号の歪みを抑えつつ効率を向上することのできる増幅装置、送信装置を提供する。

【解決手段】実施形態に係る増幅装置は、飽和出力電力が互いに異なる複数の増幅回路を具備している。実施形態に係る増幅装置は、入力端子に入力された入力信号の包絡線信号を検出する検波器と、前記検波器が検出した包絡線信号の信号電圧を、それぞれ異なる参照電圧と比較する複数の比較器と、前記複数の比較器の比較結果に基づいて前記複数の増幅回路のいずれか一つを選択する切替制御部とを具備している。そして、実施形態に係る増幅装置は、前記入力端子を前記切替制御部が選択した増幅回路の入力に接続するとともに、前記切替制御部が選択した増幅回路の出力を出力端子に接続する切替部とを具備することを特徴としている。

(もっと読む)

増幅回路および窒化物半導体装置

【課題】大電力入力時に、出力電力の低下またはゲインの低下を抑制し、かつドレインアイドル電流のドリフトが生じた場合に、ゲインの低下またはひずみ特性の劣化を抑制すること。

【解決手段】Si基板またはSiC基板と前記Si基板またはSiC基板上に形成された窒化物半導体層とを有し、かつ高周波信号がゲート端子に入力されるFET10からなるパワーアンプ11と、前記パワーアンプのドレインアイドル電流を検出する検出部12と、前記検出されたドレインアイドル電流が所定値より小さい場合は、前記ドレインアイドル電流に応じたゲートバイアス電圧を前記パワーアンプのゲート端子に出力し、前記検出されたドレインアイドル電流が所定値以上の場合は、固定値のゲートバイアス電圧を前記パワーアンプのゲート端子に出力する制御部14と、を具備する増幅回路

(もっと読む)

電力増幅器、及び、電子装置

【課題】

出力の線形性を改善した電力増幅器、及び、電子装置を提供する。

【解決手段】

電力増幅器は、所望波が差動入力される一対の第1増幅部と、前記第1増幅部の出力側に接続される一対の第2増幅部と、前記第2増幅部の出力側に接続されるトランスと、電源から前記第1増幅部に電力を供給するとともに、前記トランスを介して前記第2増幅部に電力を供給する電力供給線と、前記第1増幅部と前記第2増幅部との間に接続され、前記所望波を前記第2増幅部に通過させるとともに、前記所望波の二次歪み成分を遮断する遮断回路とを含む。

(もっと読む)

衛星信号生成ユニットによって生成された信号を増幅するためのシステム

【課題】スペクトル占有を制限できる増幅するシステムを提供する。

【解決手段】−有限インパルス応答を伴う第1の帯域通過デジタルフィルタF1および第1のデジタル/アナログコンバータCNA1を備える第1の経路V1と、−周波数置換手段MTFと、−増幅装置DAと、を備えるシステムにおいて、−有限インパルス応答を伴う第2の帯域通過デジタルフィルタF2、前記第2のデジタルフィルタF2の出力側に配置されたゲイン手段G、位相従属型の数値制御式発振器NCO、および第2のデジタル/アナログコンバータCNA2を備える第2の経路V2と、−前記第1および第2の経路V1、V2の信号を合計するための再結合装置Sと、をさらに備える。

(もっと読む)

可変利得増幅回路およびそれを用いた受信回路

【課題】連続して入力される信号の増幅または減衰が可能であるとともに、広い利得可変範囲及び高い線形性を実現することが出来る可変利得増幅回路およびそれを用いた受信回路を提供する。

【解決手段】本発明の可変利得増幅回路では、増幅トランジスタのゲートに入力される信号のレベルを低くする(図1(a)の状態(A)〜(D))ために、第1可変利得増幅部の利得が最小になったとき、第2可変利得増幅部が備える第1抵抗および第2抵抗にバイアス電圧を印加する。

(もっと読む)

電力増幅器

【課題】中低出力動作時でも動作効率を十分に向上させることができる電力増幅器を得る。

【解決手段】増幅素子Tr1,Tr2のベースには入力信号が入力され、コレクタにはコレクタ電圧が印加され、エミッタは接地されている。バイアス回路Bias1,Bias2は、バイアス電流を増幅素子Tr1,Tr2のベースに供給する。バイアス回路Bias1,Bias2は、コレクタ電圧が所定の閾値より低くなるとバイアス電流を低減させるバイアス電流低減回路12を有する。

(もっと読む)

バイアス回路を備えたパワーアンプ装置

【課題】ゲート電圧固定バイアス制御方式の歪み特性に優れている利点と、オートバイアス制御方式の個体差や温度変化によらずオペレーションのセット電流値を一定にすることが出来る利点を兼ね備えたパワーアンプ装置を提供する。

【解決手段】FETによる初段アンプ、後段アンプを含むパワーアンプと、入力段に第1のモニター抵抗を接続したオートバイアス回路とを備える。前記オートバイアス回路は前記初段アンプにだけオートバイアスを組み込むために、前記初段アンプ、後段アンプにそれぞれ、前記初段アンプのドレイン電流が一定になるようにセットされたゲート電圧がかかるように接続構成すると共に、主電源の電圧から前記初段アンプには前記第1のモニター抵抗を経由してドレイン電圧がかかり、かつ前記後段アンプには前記主電源の電圧を前記第1のモニター抵抗で分圧したドレイン電圧がかかるように接続構成した。

(もっと読む)

高周波増幅回路

【課題】低出力モードで出力電力を変化させても、ゲインの差が殆ど生じない高周波増幅回路を実現する。

【解決手段】高周波増幅回路100Aは増幅用トランジスタ10を備える。増幅用トランジスタ10のベースは、バラスト抵抗素子52を介してエミッタフォロワ用トランジスタ20のエミッタに接続する。エミッタフォロワ用トランジスタ20のベースには、抵抗素子51を介してバイアス電源が接続されている。エミッタフォロワ用トランジスタ20のコレクタには、抵抗素子53を介してモード制御電源が接続されている。抵抗素子53は固定抵抗値の抵抗素子である。モード制御電源は、可変電圧型であり、モードに応じて直流のモード制御電圧Vmodeを発生する。モード制御電圧Vmodeは、低出力モード時には低電圧となり、高出力モード時には高電圧となる。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に含まれる増幅回路における入出力特性の線形性が劣化するのを抑えるとともに、増幅器自体における入出力特性の線形性が劣化するのを抑えることができる半導体装置を提供する。

【解決手段】本発明は、外部と接続する複数の端子を有する配線基板72に、半導体チップ71を実装してパッケージングしてある半導体装置である。半導体装置は、半導体チップ上に形成してある、少なくとも一つの差動増幅器61と、平衡信号線路を差動増幅器61と接続し、半導体チップ71上に形成してある、少なくとも一つのバラン62とを備える。差動増幅器61の接地配線と、バラン62の接地配線とは、半導体チップ71上に分離して形成してあり、差動増幅器61の一つの接地配線と配線基板72とを接続するボンディングワイヤ77の数が、バラン62の一つの接地配線と配線基板72とを接続するボンディングワイヤの77数より多い。

(もっと読む)

バイアス制御回路

【課題】増幅器の歪み特性を緩和しつつ、低レベル高周波信号に対する利得低下を抑制する。

【解決手段】高周波信号を増幅する増幅器(20)のバイアスを制御するためのバイアス制御回路(10)は、高周波信号の包絡線を検波する検波器(11)と、増幅器(20)に一定のバイアス電流を供給する第一のバイアス回路(12)と、高周波信号の包絡線のレベル変動に追従して変動するバイアス電流を増幅器に供給する第二のバイアス回路(14)とを備える。

(もっと読む)

電力増幅器、電力増幅器の制御方法、電力増幅器の制御プログラム

【課題】全周波数帯域に渡ってドライブ段増幅器のドライブ量を最適化して、終段増幅器のオーバードライブを防止できるようにすると共に、電力増幅器全体の効率を向上させる。

【解決手段】バックオフ検出器22の検出出力からドライブ段増幅器12のバックオフ量を検出し、このバックオフ量が所定値となるように、ドレイン電圧制御回路30により、ドライブ段増幅器12のドレイン電圧を制御することで、ドライブ段増幅器12のドライブ量を全周波数帯域に渡って最適化する。そして、電力増幅器1の総合利得が所望の利得となるように、可変アッテネータ制御回路33で可変アッテネータ11の減衰量を制御する。ドライブ段増幅器12のドライブ量が最適化されることから、オーバードライブによる終段増幅器13の破損を防止でき、また、効率の向上が図れる。

(もっと読む)

増幅装置

【課題】電力効率の低下を抑制する。

【解決手段】増幅部1は、電力ノードN1に供給される電力によって入力信号を増幅する。電源部2は、電力ノードN1に固定電圧の電力を供給する。電源部3は、入力信号のエンベロープに基づくエンベロープ信号と、電力ノードN1の電圧とに基づいて、電力ノードN1に可変電圧の電力を供給する。AS部4は、電源部2が電力ノードN1に電力を供給し、電源部3が電力ノードN1に電力を供給しない固定電圧電力モードにおいて、電力ノードN1のインピーダンスを下げる。合成部5は、固定電圧電力モードにおいて、電源部3がAS部4による電力ノードN1の電圧変化によって、電力ノードN1に電力を供給しないように、エンベロープ信号にキャンセル信号を合成する。

(もっと読む)

増幅回路、増幅回路への電力供給制御方法及び送信装置

【課題】増幅された信号のACLR特性の劣化を防止するとともに、増幅制御による電力供給の適正化を図る。

【解決手段】 増幅回路(2)、増幅回路への電力制御方法又は送信装置であって、増幅器(4)と、検出部(6)と、制御部(8)を備える。検出部が増幅器が出力する出力電力を検出し、制御部(8)は、この検出出力により求められるピーク電力対平均電力比(PAR)に対する増幅器の飽和点が最適値になるように増幅器(4)の動作を制御する構成である。

(もっと読む)

増幅装置

【課題】直流電圧が含まれていることを検出する検出部がアンプ回路にとって負荷として機能しない増幅装置を提供する。

【解決手段】増幅装置1は、電圧源V1から供給される電源電圧に基づいて、スピーカーの負側入力端に供給するための基準電圧を生成する基準電圧生成部2と、入力信号を増幅して、スピーカーの正側入力端に出力するアンプ回路A1と、第1閾値電圧と第2閾値電圧とを生成する閾値電圧生成部4と、基準電圧が第1閾値電圧以上である場合、又は、基準電圧が第2閾値電圧以下である場合にアンプ回路からの出力電圧に直流電圧が含まれることを示す信号を出力し、基準電圧が第1閾値電圧よりも小さく、かつ、基準電圧が第2閾値電圧よりも大きい場合にアンプ回路からの出力電圧に直流電圧が含まれないことを示す信号を出力する検出部5とを備える。

(もっと読む)

高周波信号処理装置

【課題】送信パワーばらつきの低減と高調波歪みの低減を実現可能な高周波信号処理装置を提供する。

【解決手段】例えば、飽和領域に動作点が定められたプリドライバ回路PDRと、線形領域に動作点が定められ、高いQ値を持つインダクタL1aによって線形増幅動作を行う最終段ドライバ回路FDRとを備える。例えば、電圧制御発振回路VCOによって直接変調された信号は、その振幅レベルのばらつきがPDRによって抑圧され、PDRで生じ得る高調波歪み成分(2HD,3HD)がFDRのL1a等によって低減される。

(もっと読む)

1 - 20 / 170

[ Back to top ]