Fターム[5K029KK31]の内容

直流方式デジタル伝送 (8,390) | 監視;試験 (418) | 監視、試験、制御信号を用いるもの (37)

Fターム[5K029KK31]の下位に属するFターム

パルストリオ信号を用いるもの

位相検出型用信号を用いるもの (7)

Fターム[5K029KK31]に分類される特許

1 - 20 / 30

信号伝送システムおよび信号伝送方法

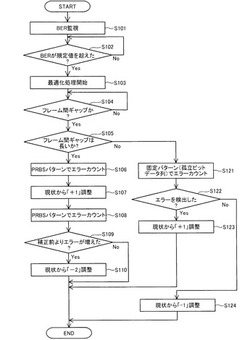

【課題】通信装置等のデータ伝送を行うシステムにおいて、その運用中に、データの伝送を妨げることなく、伝送損失を補正することのできる信号伝送システムを提供することを目的とする。

【解決手段】伝送システムは、第1の回路と、第2の回路と、第1の回路から第2の回路に差動信号によってデータを伝送する伝送線路と、差動信号の伝送の間隙を監視する監視部と、監視部によって監視された間隙において、差動信号の伝送損失を補正する補正部と、を備える。

(もっと読む)

伝送試験装置、伝送試験方法及び伝送試験プログラム

【課題】伝送路にエラーを継続的に発生させること。

【解決手段】伝送路における伝送試験を行う伝送試験装置100は、判定部133と、キラーパターン転送部132とを有する。判定部133は、伝送路において試験データに生じた異常の割合を示す異常発生率を取得し、該異常発生率が所定の基準値を下回ったか否かを判定する。キラーパターン転送部132は、判定部133により異常発生率が所定の基準値を下回ったと判定された場合、試験データを変更して送信する。

(もっと読む)

信号伝達装置及びこれを用いたモータ駆動装置

【課題】ドライバチップの異常検出期間が短過ぎると、異常パルス信号のパルス生成が停止された後、異常判定期間の経過前に異常パルス信号のパルス生成が再開されてしまい、コントローラチップでドライバチップの異常を認識することができなくなるおそれがあり、2つの回路を絶縁しつつ一方の異常を確実に他方に伝達することのできる信号伝達装置、及びこれを用いたモータ駆動装置を提供する。

【解決手段】信号伝達装置100は、第1回路110と第2回路120との間を絶縁しながら信号伝達を行うものであり、第1回路110は、第2回路120から伝達される異常パルス信号Sbを監視して第2回路120の異常有無を判定し、第2回路120は、第2回路120で異常が検出されてから少なくとも第1回路110で第2回路120の異常有無が判定されるまで異常パルス信号Sbを異常状態に保持する。

(もっと読む)

バスシステム

【課題】共通バスに接続された複数の電子機器の動作確認が短時間でできる安価なバスシステムを提供する。

【解決手段】車両ネットワークシステム1の下位ネットワークN2では、共通データ信号線43aに、電子機器33〜36と、中継コネクタユニット22と、が接続されている。各電子機器33〜36は、中継コネクタユニット22からの動作確認命令信号を受信したとき、共通データ信号線43aから所定時間にわたり電流を引き込む。各電子機器は、それぞれ同一の基準引込量の電流を引き込むように構成されている。中継コネクタユニット22は、各電子機器に対して動作確認命令信号を同報送信したのち、共通データ信号線43aから引き込まれる電流量を測定して、この電流量及び基準引込量から電子機器の応答数を算出し、この応答数及び電子機器の接続数に基づいて、各電子機器が正常に動作しているか否かを判定する。

(もっと読む)

通信インタフェース装置、送信制御方法および切断処理制御方法

【課題】リンク断転送機能により生じるネットワーク擾乱を防止する。

【解決手段】通信インタフェース装置10は、クライアント装置2との間でクライアント信号を送受信する送受信部50と、クライアント信号の受信停止を検出する検出部51と、伝送路網3上においてクライアント信号を伝送するためのパスの出口の伝送装置4bへ、クライアント装置2bとの間でクライアント信号を送受信するための接続を切断させる指示信号を送信する指示信号送信部61と、第1待機時間に亘ってクライアント信号の受信停止が継続するまで指示信号の送信を停止する指示信号制御部71を備える。

(もっと読む)

パルスマスク試験機能を備えた伝送システム

【課題】接続線路等の外的要因を考慮して波形整形できるとともに、自局装置と対向局装置が双方向接続されない場合でもパルスマスク試験を行うことを可能にする。

【解決手段】自局装置2は、送信線6a、6bにパルスマスク信号を送出するパルスマスク信号送信部6と、対向局装置3から送信される調整情報に基づいてパルスマスク信号の出力レベルを調整するパルスマスク信号調整部13と、送信線6b又はパルスマスク信号調整部13を第2の接続線路5に選択的に接続するスイッチ部11とを備える。対向局装置3は、受信線21a、21bを介してパルスマスク信号を受信するパルスマスク信号受信部21と、受信したパルスマスク信号をマスクデータと照合するパルスマスク照合部26と、パルスマスク信号の出力レベルの調整量を演算する演算部27と、受信線21b又は演算部27を第2の接続線路5に選択的に接続するスイッチ部30とを備える。

(もっと読む)

信号発生装置及び発生方法

【課題】シリアル・データ・パターンに符号間干渉ISI効果及び帯域幅拡張プリエンファシスBWEPE効果を与える。

【解決手段】CPU60は、表示器36上にユーザ・インタフェースを発生して、シリアル・データ・パターン用のパラメータと、このシリアル・データ・パターンの帯域幅拡張プリエンファシス効果及び符号間干渉効果の少なくとも一方のパラメータとを設定する。CPUは、シリアル・データ・パターン・パラメータ、符号間干渉効果のパラメータ及び帯域幅拡張プリエンファシス効果のパラメータを用いて、波形記録ファイルを作成する。波形発生器70は、波形記録ファイルを受け、符号間干渉効果のパラメータ及び帯域幅拡張プリエンファシス効果のパラメータにより定義された符号間干渉効果及び帯域幅拡張プリエンファシス効果の少なくとも一方を有するシリアル・データ・パターン・アナログ出力信号を発生する。

(もっと読む)

誤り率測定装置及び誤り率測定方法

【課題】CDRを用いずにデータの受信を可能にする。

【解決手段】データ処理部4は、シフトされたデータの変化点に基づくヒストグラム上で計数値が最大値を示すビットの位置を変化点とし、この変化点から次の変化点までの略中央にデータの取得位置が来るべくシフト量を算出する。タイミング制御部6は、リファレンスクロックと同期が取れ、入力データのビットレートに応じたクロックを出力し、このクロックの周期を、シフト量が所定の限界処理ビットを超えたときに入力データをシフトするクロックの1周期だけ増減して調整する。FIFO5は、ドロップされたデータを順次取り込んで保持する。この保持されたデータは、シフト量が限界処理ビットを超えたか否かに応じたタイミング制御部6のクロックのタイミングにより取り出される。

(もっと読む)

高速シリアル転送デバイス試験方法、プログラム及び装置

【課題】高速シリアル転送デバイスでの同期外れ等障害の検証に特化した試験パターンを作成して対象装置内で連続的に転送することで、同期外れ等を短時間に検証可能とする。

【解決手段】試験パターン作成部10は、高速シリアル転送デバイスが有する複数のシリアル転送チャネルの各々に、符号変換テーブルによる変換後データでビット0又は1の同値が連続転送されるように変換前データを並べた試験パターンを作成する。基本パターン設定部22は、高速シリアル転送デバイスにおけるバイト順序方式と符号変換のRD値を考慮したうえで基本パターンを設定する。基本パターン再設定部24は高速シリアル転送デバイスにおけるビット転送順序のチャネル使用方法に合わせて基本パターンを再設定する。基本パターン並替え部26は使用チャネル数やビット転送順序等のチャネル使用方法に合わせて各チャネルに基本パターンが転送されるように並び替える。

(もっと読む)

伝送回路および信号伝送方法

【課題】主信号および補助信号を少ない配線数の伝送路で伝送する信号伝送技術を提供する。

【解決手段】主信号および補助信号を伝送する伝送回路は伝送路と重畳・分離部とを有する。重畳・分離部は、主信号を伝送路に送信する送信回路と伝送路から主信号を受信する受信回路のいずれか一方または双方に備えられ、伝送路上の信号に自回路からの補助信号を重畳し、伝送路上の信号から、自回路からの補助信号と他回路からの補助信号のいずれか一方または両方を分離する。

(もっと読む)

高分解能出力ドライバ

それぞれ、量子化ステップより実質的に大きい、公称インピーダンスを有し、量子化ステップより実質的に小さい、インピーダンスステップだけ、相互にインクリメント的に異なる、比較的に少数のサブドライバブランチまたはスライスを有する、高分解能出力ドライバ。一実装では、かかる「差動」または「非一様」サブドライバスライスは、n choose k等化器の個別の要素を実装し、各かかる差動サブドライバスライスは、一様要素インピーダンス較正DACによって実装される。別の実装では、一様スライス等化器の各構成要素は、差動スライスインピーダンス較正DACによって実装され、さらに別の実装では、差動スライス等化器の各構成要素は、差動スライスインピーダンス較正DACによって実装される。付加的セットの実装の実装では、等化およびインピーダンス較正機能は、階層的実装のネスト化された「DAC内のDAC」配設においてではなく、個別の並列セットのドライバブランチにおいて、双方向に実装される。かかる双方向配設を通して、等化器および較正器量子化の倍増が回避され、それによって、規定の範囲および分解能を満たすために要求されるサブドライバスライスの総数を減少させる。 (もっと読む)

アダプタ装置および伝送路評価システム

【課題】パッド付の伝送路の伝送特性についての評価装置による評価を可能にする、評価装置に接続されるアダプタ装置およびこれを備える伝送路評価システムを実現する。

【解決手段】試験信号が入力された評価対象伝送路2から出力される出力信号に基づき評価対象伝送路2の伝送特性を評価する評価装置3に接続されるアダプタ装置1は、評価対象伝送路2の入力端へ入力される試験信号と同じ信号が入力される入力端を有する基準伝送路11と、評価対象伝送路2の出力端から出力される出力信号から、基準伝送路11の入力端に生じた試験信号の反射成分と評価対象伝送路の入力端に生じた試験信号の反射成分との差を増幅した反射成分増幅信号と、基準伝送路11における試験信号の通過損失分と評価対象伝送路2における試験信号の通過損失分との差を増幅した通過損失分増幅信号と、を減算して生成される信号を評価装置3への評価信号とする生成手段12と、を備える。

(もっと読む)

CPRIインターフェース回路

【課題】

CPRI(Common Public Radio Interface)規格準拠の通信装置をインターフェースするCPRIインターフェース用論理内部のfast C&M(Control & Management)データ用論理の正常動作を維持し、また、仮に、異常な動作状態にスタックした場合であっても、正常な動作状態に復帰させる。

【解決手段】

CPRIインターフェース用論理の外部からCPRIの転送フォーマットに基づいてfast C&Mデータの入出力状況を監視することにより、fast C&Mデータ用論理の動作状態を推定する。ここで、推定結果がアイドル状態であった場合、fast C&Mデータ用論理を強制的に初期化する。

(もっと読む)

伝達特性測定装置、伝達特性測定方法、および、電子デバイス

【課題】被試験回路の伝達特性を測定する。

【解決手段】被試験回路の入出力間の伝達特性を測定する伝達特性測定装置であって、予め定められた周波数のキャリア信号に予め定められた周波数とは異なる周波数の加算信号を加算した試験信号を生成して、被試験回路に入力する試験信号入力部と、被試験回路が出力する出力信号を測定した結果に基づいて、加算信号の周波数における被試験回路の伝達特性を測定する伝達特性測定部とを備える伝達特性測定装置を提供する。被試験回路は、半導体チップに形成されてもよい。被試験回路は、半導体チップに入力される信号を補正して出力し、半導体チップには、被試験回路の出力信号を、キャリア信号の周波数でサンプリングするサンプリング回路が更に形成されてもよい。

(もっと読む)

ノイズ試験システムおよびノイズ試験方法

【課題】試験用の差動ノイズを差動信号に対して高精度に重畳する。

【解決手段】ノイズ発生器10から発生されたノイズを、ディバイダ20によりポジ側遅延回路31およびネガ側遅延回路32に分配する。ポジ側遅延回路31、ネガ側遅延回路32から出力されるノイズは、結合コンデンサと抵抗とを介して、差動伝送路を構成するポジ側、ネガ側の各信号線に印加される。抵抗の抵抗値は、ポジ側、ネガ側の各信号線の特性インピーダンスより十分高く設定されている。そして、ポジ側遅延回路31およびネガ側遅延回路32の各遅延量は、ノイズ発生器10から発生されるノイズの周波数と、上記の各抵抗を通じて差動伝送路に印加する差動ノイズの振幅とから決定される遅延差を互いに有するように設定される。

(もっと読む)

シリアルデータの劣化検出回路を有する制御回路

【課題】受信した光信号に異常が発生する前に光信号の劣化を検出する。

【解決手段】シリアル通信機能を備えた制御機器において、シリアル通信機能により受信したシリアルデータの立上りあるいは立下りエッジの位相を検出し、シリアルデータの立上りあるいは立下りエッジの位相と基準クロックの位相との間の位相差を位相データとして出力する位相検出回路12と、位相検出回路12から出力される位相データが予め設定された範囲を超えたか否かを判定し、位相データが予め設定された範囲を超えたと判定したときワーニングを出力する位相判定回路13と、を備える。

(もっと読む)

インターフェース・コネクタ接続状態判断装置及びその方法

【課題】メイン電源を投入する前にブレードなどの挿入基板と収納ユニットなどの被挿入基板との間のインターフェース・コネクタが完全に接続されているか否かを判断する。

【解決手段】 挿入基板から被挿入基板に交流テスト信号を出力する手段と、被挿入基板で挿入基板に折り返された交流テスト信号にエラーが含まれているか否かを判断し、エラーが含まれている場合には、挿入基板と被挿入基板との間のインターフェース・ユニットが不完全に接続されていると判断する手段と、を備える。

(もっと読む)

試験装置

【課題】双方向差動インタフェースを有するDUTの試験装置を提供する。

【解決手段】メインドライバアンプAMP0は、DUT102に送信すべきパターンデータPATにもとづいて第1差動信号Vdを生成する。第1レプリカドライバアンプAMP1は、パターンデータPATにもとづいて第2差動信号Vcpを生成する。第2レプリカドライバアンプAMP2は、パターンデータPATにもとづいて第3差動信号Vcnを生成する。第1コンパレータCMP1は、ノードN1とノードN2の電圧を比較し、第2コンパレータCMP2はノードN3とノードN4の電圧を比較する。

(もっと読む)

シリアルデータ通信システム、及びシリアルデータ通信方法

【課題】マスター装置からスレーブ装置へシリアルデータを送信する際において、通信エラーを即座に知ることができる。

【解決手段】マスター装置からスレーブ装置に送信されるシリアルデータTxDには、同じ構成のダミーデータdummyが2バイト以上連続するように付加されており、スレーブ装置は該ダミーデータdummyを認識した場合には、通信エラー処理を行うようになっている。いま、ノイズ等の影響により、シリアルデータが符号TxD2に示すようにΔtだけシフトしてしまったとすると、期間A5及びA6ではETXもシフトしているために認識されず、データ受信終了の処理はされない。しかし、A7の期間では、1つ目の0xFFの一部と2つ目の0xFFの一部とが受信されて0xFFが認識されることになるので、スレーブ装置は通信エラー処理を即座に行うことができる。

(もっと読む)

差動信号送信装置、差動信号送受信システム、差動信号制御方法及び差動信号制御プログラム

【課題】高速シリアル伝送におけるパラレルシリアル変換によって生成された差動信号を出力する差動信号送信装置において、固定されたエラー以外のエラーを発生させる。

【解決手段】シリアルパラレル変換を行い、差動データを出力するSERDES部2と、制御部4に対して、出力バッファ5と擬似障害バッファ6のアウトプットイネーブル及び駆動能力の制御を指示する指示部3と、指示部3からの指示に基づいて、出力バッファ5と擬似障害バッファ6の制御を行う制御部4と、SERDES部2から出力された差動データを入力し、アウトプットイネーブルおよび駆動能力を制御し、SERDES部2から入力された差動データを制御部4の制御に従って出力する出力バッファ5と擬似障害バッファ6とを備え、出力バッファ5と擬似障害バッファ6の各々の出力の正論理(+)と負論理(−)が逆に接続される。

(もっと読む)

1 - 20 / 30

[ Back to top ]