Fターム[5K047AA05]の内容

デジタル伝送方式における同期 (12,489) | 目的、効果 (2,701) | 同期品質の向上 (1,344) | タイミング品質の向上 (665)

Fターム[5K047AA05]の下位に属するFターム

位相ジッタ吸収 (104)

ケーブル長依存の伝送遅延変化の補償 (27)

スキュー補正 (110)

無信号時にもクロック供給 (10)

Fターム[5K047AA05]に分類される特許

61 - 80 / 414

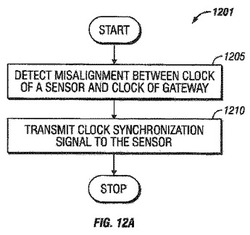

ワイヤレスセンサの分散処理のための方法及び装置

本願開示のある態様は、圧縮センシング(CS)のための方法に関する。CSは、任意に高い分解能を用いて信号を復元するためにシャノン/ナイキストサンプリング定理により提案されるものより著しく少ないセンサ測定値を使用することができる信号処理概念である。この開示において、医療及びフィットネス用途向けのボディエリアネットワーク(BAN)において信頼できる通信と低い電力のロバスト・センサをサポートするために、CSフレームワークがセンサ信号処理のために適用される。 (もっと読む)

受信装置

【課題】送信データ量の増加を抑えつつ、撮像装置の動作に同期して表示処理を行うことができる受信装置を提供する。

【解決手段】RF回路14は撮像装置1から送信データを受信する。表示回路18は送信データから表示用の表示信号19を作成する表示処理を行う。ID検出回路20は送信データから特定パケットを抽出し、撮像位相検出回路22は特定パケットの受信タイミングを複数回計測する。表示位相調整回路24は、計測の結果を用いて表示信号19の位相調整処理を行う。

(もっと読む)

複数の演算装置相互のデータ受信タイミング算出方法並び装置及び複数の演算装置の位相を同期させる同期方法並びに装置

【課題】高分解能で受信タイミングを把握することができる複数の演算装置相互のデータ受信タイミング算出方法並び装置を提供する。

【解決手段】複数の演算装置相互にデータを送信し、前記複数の演算装置それぞれへの前記データの受信タイミングを算出する複数の演算装置相互のデータ受信タイミング算出方法において、前記演算装置のうちの1つを送信装置、他の演算装置を受信装置とし、前記送信装置から、シーケンシャル番号をふったデータを前記受信装置に送信し、前記受信装置は、前記データを内部に保有するバッファメモリに蓄積するとともに、前記バッファメモリに蓄積されたデータからシーケンシャル番号を2回以上連続で読み取り、該シーケンシャル番号の変化から前記データの受信タイミングを算出し、前記送信装置として使用する演算装置を前記データの送信1回ごとに順次変えていき、各送信装置から受信装置への受信タイミングを算出する。

(もっと読む)

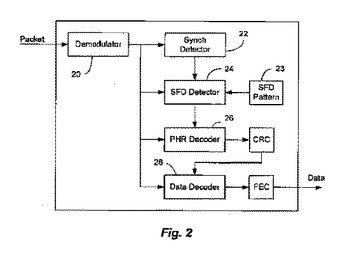

無線デジタル通信システムにおけるフレーム開始デリミタの検出

順方向誤り訂正は、柔軟性を提供し且つSFDを見逃すことを減少するためにフレーム開始デリミタ(SFD)の検出と関連して使用される。入力信号内の候補SFDは、通常より低い検出閾値を使用して識別され、対応するマーカはバッファに格納される。格納されたマーカ毎に、候補SFDに続く物理層ヘッダが誤り訂正技術を用いて復号化され、訂正不能誤りが存在するかを判定する。訂正不能誤りが存在する場合、候補は拒否され、次の候補が評価される。訂正不能誤りが存在しない場合、候補は有効なSFDであると宣言され、残りの信号が復号化される。2つの検出閾値が誤り符号化パケット及び非符号化パケットの双方を許可するネットワークにおいて採用されてもよい。より高い性能を助長するSFDパターンを選択する技術が更に開示される。  (もっと読む)

(もっと読む)

光周波数分割多重送信システムにおける同期プロセス

本発明は、光直交周波数分割多重(OOFDM)トランシーバの受信部において受信速度を向上させることのできる同期方法を開示する。 (もっと読む)

電子回路ユニット、シリアル伝送システム、および伝送制御方法

【課題】基準CLKのための専用のCLKユニットや各ユニット内のPLLを必要としない構成で、低コスト、低消費電力を実現しながらも、データエラーを引き起こすことのないようにする。

【解決手段】他の電子回路ユニットからシリアル伝送によりデータ受信を行う電子回路ユニットについて、上記電子回路ユニットおよび上記他の電子回路ユニットは、基準クロックを発生させるクロック発生器をそれぞれ備え、上記電子回路ユニットは、当該電子回路ユニットにおける基準クロックおよび上記他の電子回路ユニットにおける基準クロックのずれを監視する監視手段と、上記監視手段により検出された基準クロックのずれを該電子回路ユニットの上記クロック発生器に補正させる補正指示手段と、を備える。

(もっと読む)

多重通信装置および多重通信システム

【課題】LINプロトコルによるシングルマスタ方式の多重通信装置に採用するマイコンに内蔵のクロック発振子が要因となり、そのクロック周波数が規定値からずれる場合があっても、このクロック周波数の変動に伴う誤差を補正が可能となるようにする。

【解決手段】LIN通信プロトコルに基づくシリアル通信によりマスタ・ノードと複数のスレーブ・ノード間で通信する多重通信装置であり、商用交流電源から生成した直流電源をマスタ・ノードに供給するとともに、前記商用交流電源から生成した電源周期信号を前記マスタ・ノードのマイコンに供給し、該マイコンにおいて前記電源周期信号によりクロック発振周波数の変動に伴う誤差の補正を行う。

(もっと読む)

通信システムおよび通信装置

【課題】ある通信装置からクロック信号を送信し、このクロック信号を受信した通信装置が受信したクロック信号を基準にデータの送受信を行う通信システムにおいて、データ送受信の基準タイミング(送受信基準)の「ずれ」を補正する回路を備えることなく、送受信基準の「ずれ」量を減少させるができる技術を提供する。

【解決手段】マスタ装置である通信ECU10は、クロック通信線5に対して、各通信ECU10,40がデータの送受信の際に互いに同期をとるためのクロック信号を送出する。そして、通信ECU10,40は、クロック通信線5からクロック信号を受信する。すると、各通信ECU10,40は、受信したクロック信号をデータ送受信時の基準タイミングである送受信基準として、クロック通信線5以外のデータ通信線6,7に対してデータの送信およびデータの受信を行う。

(もっと読む)

データ受信装置、データ受信方法及びプログラム

【課題】より安定した高速データ転送を可能とするデータ受信装置、データ受信方法及びプログラムを提供する。

【解決手段】データ受信装置は、スクランブルされ送信されたデータを受信データとして受け取り、送信側とのタイミングを調整するエラスティックバッファ回路7と、エラスティックバッファ回路7でタイミング調整されたデータをデスクランブルする際のタイミングを調整するSKP補完回路9と、SKP補完回路9から入力されるデータをデスクランブルするデスクランブル回路10とを有する。受信データは、送信側とのタイミングを調整するためのSKPオーダードセットを有し、SKP補完回路9は、SKPオーダードセットに含まれるSKPシンボルの数が所望の個数となるように、正常なSKPシンボルを最初に受信後、既存データをSKPシンボルに置換して必要数出力する。

(もっと読む)

通信システムに用いられるノード

【課題】バスを介して通信する通信システムに用いられるノードにおいて、通信を高速化しても、往復分の伝播遅延および同期補正についての制約が満たされやすくすること。

【解決手段】受信状態では、バス信号109に基づいて生成される受信クロック信号106が示すタイミングをSP(サンプリング・ポイント)とし、サンプリング回路205が受信信号104をサンプリングする。送信状態では、送信クロック信号101が遅延した遅延クロック信号が示すタイミングをSPとし、サンプリング回路205が受信信号104をサンプリングする。また、送信権がある状態では送信クロック信号101は受信クロック信号106とクロック公差がほぼ無い。よって、遅延クロック信号103は受信クロック信号106よりも遅延することになる。よって、送信状態では受信状態よりも遅いタイミングで受信信号104をサンプリングすることになる。

(もっと読む)

電子機器、その制御方法及びプログラム

【課題】簡単な構成で、かつ、後段の論理回路のセットアップタイム、ホールドタイムのマージンを確保しつつ、メタステーブルの発生を抑制できるようにする。

【解決手段】アナログデータを処理するアナログデータ処理部102、アナログデータ処理部102から出力されるアナログデータが入力されるデジタルデータ処理部103、デジタルデータ処理部103に供給する動作クロックの遅延量を制御する遅延制御部104を備えており、安定したデータを取得できるアナログチャンネル、例えば温度センサ114用のアナログチャンネル1から入力されるデータをデジタルデータに変換する際、サンプリングタイミングを変化させ、データが変動する境界(サンプリングタイミング)を検出することにより、デジタルデータ処理部103に供給する動作クロックの遅延量を決定する。

(もっと読む)

半導体装置およびデータ転送方法

【課題】複数のクロックドメイン間での非同期データ転送を汎用的に行うことができるようにする。

【解決手段】データ転送元の第1クロックドメイン10と、データ転送先の第2クロックドメイン20と、前記第1クロックドメインの第1データDATAを前記第2クロックドメインの第2データD3に乗せ換えるデータ乗せ換え回路40,21,22,23と、を有する半導体装置であって、前記データ乗せ換え回路は、前記第1データDATAおよび前記第2データD3を直接比較して第1制御信号ENを出力する第1論理回路23を有するように構成する。

(もっと読む)

データ処理回路での2ティア・サンプリング補正のシステムおよび方法

【課題】データ処理のシステムおよび方法を提供すること。

【解決手段】たとえば、アナログ−ディジタル変換器と、ディジタル補間回路と、位相誤差回路と、位相調整制御回路とを含むデータ処理回路を開示する。アナログ−ディジタル変換器は、少なくとも部分的に粗制御によって調節されるサンプリング位相でアナログ・データ入力をサンプリングし、一連のディジタル・サンプルを提供する。ディジタル補間回路は、少なくとも部分的に微細制御に基づいて一連のディジタル・サンプルのサブセットの間で補間する。位相誤差回路は、位相誤差値を計算する。位相調整制御回路は、少なくとも部分的に位相誤差値に基づいて粗制御および微細制御を判定するように動作可能である。

(もっと読む)

ネットワーク同期方法と同期化回路

【課題】簡単な構成で高応答性を実現したネットワーク同期方法と同期化回路を提供する。

【解決手段】同期パケットのマスタカウンタ値と、そのタイミングでのスレーブカウンタ値の差分から経路ジッタを算出する。直近のものを含めた複数個の経路ジッタを記憶する。記憶された複数個の経路ジッタのうち最小経路ジッタを抽出する。各経路ジッタと最小経路ジッタの差分から予測経路ジッタを形成する。スレーブカウンタ値に予測経路ジッタを加えて補正後スレーブカウンタ値を算出する。直近のものを含めた複数個の補正後スレーブカウンタ値を記憶する。直近のものを含めた複数個の同期パケットのマスタカウン値を記憶する。記憶された2つの補正後スレーブカウン値の差分と、それに対応し2つのマスタカウンタ値の差分との比から周波数偏差を算出してネットワーク同期を行う。

(もっと読む)

トランスポート・パケットを含む信号の受信機

【課題】 多重化およびトランスポート・パケット化装置の同期をとる。

【解決手段】 圧縮された多層のビデオ信号のトランスポート層または多重層のような、中間層の信号の同期を発生させる装置は、システムの符号化端末において、システム・クロック22に応答する計数器23を含んでおり、計数値は処理装置13により所定のスケジュールに従ってトランスポート層における信号に詰め込まれる。システムの受信端末において、逆トランスポート処理装置18は、補助トランスポート・データからのPCR、および制御信号をシステム・クロック発生器27に供給する。クロック発生器27はこれらの信号に応答し、少なくとも逆トランスポート処理装置18の動作に同期するシステム・クロック信号を発生する。このシステム・クロック信号は、処理要素のタイミングを制御する為に、受像機システム制御装置26に供給される。

(もっと読む)

高精度な同期方法およびシステム

第1の基準クロックと、基準クロックの周波数に従属されるべき第2のクロックとの間でクロックを同期させる方法であって、これらの2つのクロックが共通クロックを共有する方法において、以下のステップ:

− 基準クロックおよび共通クロックを使用した、タイムスタンプの整数部の計算と、

− 基準クロックに対してローカルなシステムクロックの生成と、

− システムクロック信号と基準クロック信号との間の位相シフトの計算と、

− システムクロック信号と共通クロック信号との間の位相シフトの計算と、

− タイムスタンプの小数部の計算と、

− 第2のクロックへの小数のタイムスタンプの送信と、

− 共通クロックおよび受信されたタイムスタンプを使用した、第2のクロックを従属化することと

を含む方法。  (もっと読む)

(もっと読む)

通信装置

【課題】受信信号に連続データが含まれる場合においても受信信号の変化点に動的に追従し、最適なサンプリングクロックを選択すること。

【解決手段】本発明に係る通信装置は、サンプリングクロックを更新するタイミングにおいてビット境界信号を毎回記憶する現在情報記憶部130と、受信信号の変化点が検出された場合には現在情報記憶部130に記憶された信号を取り込み記憶し、受信信号の変化点が検出されなかった場合には記憶している信号の更新を行わない過去情報記憶部140と、受信信号の変化点が検出された場合には、現在情報記憶部130に記憶された信号に基づいてN相のクロックの中から受信信号のサンプリングに使用するCLKSEL2を選択し、受信信号の変化点が検出されなかった場合には、過去情報記憶部140に記憶された信号に基づいてCLKSEL3を選択するクロック選択部44と、を備える。

(もっと読む)

通信装置

【課題】シリアルデータの入力遅延を計測して、データ転送レートを下げずにデータ通信を行なうことが可能な通信装置を提供すること。

【解決手段】イニシエータは、ターゲット2に対してシリアルデータの入力遅延検出モードであることを示すADJUST信号を出力するSIO制御部20と、ターゲット2から出力されるシリアルデータの入力遅延値を検出する入力遅延検出回路53と、入力遅延検出回路53によって検出された入力遅延値に基づいて、ターゲット2から出力されるシリアルデータのラッチタイミングを調整する遅延調整回路57とを含む。また、ターゲット2は、SIO制御部20からシリアルデータの入力遅延検出モードであることを示す信号を受けたときに、入力遅延値検出用のシリアルデータを出力するデータ出力回路202を含む。したがって、データ転送レートを下げずにデータ通信を行なうことが可能となる。

(もっと読む)

データ処理装置及びデータ処理方法、受信装置及び受信方法、同期検出装置及び同期検出方法、並びにコンピューター・プログラム

【課題】受信したパケットに付加されている既知シーケンスからなる同期ワードを非正規化相関演算して正確に同期検出を行なう。

【解決手段】受信軟判定値から非正規化相互相関値を算出し閾値との大小比較に基づいて相互相関極大値検索ウィンドウを決定した後、受信硬判定値から非正規化相互相関値を算出し、検索ウィンドウ内で当該相互相関値が極大となる同期ワード位置に決定するので、例えば周波数特性が大きく変化し又は非線形歪みの大きな通信環境下でも、少ない演算量でより正確な同期検出を行なうことができ、ひいては少ない演算量で正確なデータ受信が可能となる。

(もっと読む)

同期化回路及び同期化方法

【課題】エンコードデータの遷移中にサンプリングが行われても、正しいデコード結果を得ることができる同期化回路及び同期化方法を提供すること。

【解決手段】本発明にかかる同期化回路1は、エンコード回路11と、デコード回路13と、を備えている。エンコード回路11は、ワンホット型のエンコードデータ14を、第1のクロックCLK1に基づき出力する。エンコードデータ14は、sビット幅であり、m個(ただし、mは2以上、かつs−2以下の整数とする)の連続するアクティブビットと、非アクティブビットと、を有する。また、デコード回路13は、エンコードデータ14が、第2のクロックCLK2で読み出された同期化エンコードデータ15のアクティブビットの数を検出する。そして、検出したアクティブビットの数と、エンコードデータ14のアクティブビットの数と、に基づいて、デコード値を決定する。

(もっと読む)

61 - 80 / 414

[ Back to top ]