Fターム[5K047AA05]の内容

デジタル伝送方式における同期 (12,489) | 目的、効果 (2,701) | 同期品質の向上 (1,344) | タイミング品質の向上 (665)

Fターム[5K047AA05]の下位に属するFターム

位相ジッタ吸収 (104)

ケーブル長依存の伝送遅延変化の補償 (27)

スキュー補正 (110)

無信号時にもクロック供給 (10)

Fターム[5K047AA05]に分類される特許

21 - 40 / 414

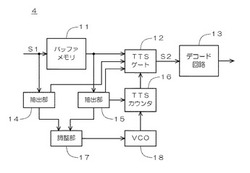

映像受信装置

【課題】ビットレートが低い場合であってもデコードの開始が遅れることを回避することが可能な映像受信装置を得る。

【解決手段】映像受信装置4は、それぞれにタイムスタンプ50が付加された複数のトランスポートパケットTPを含むトランスポートストリームS1を一時的に記憶するバッファメモリ11と、基準クロックを発生するVCO18と、基準クロックに基づいてカウント動作を行うTTSカウンタ16と、各トランスポートパケットTPに付加されているタイムスタンプ50の値と、TTSカウンタ16のカウント値とに基づいて、バッファメモリ11からの各トランスポートパケットTPの出力を制御するTTSゲート12と、バッファメモリ11に入力されたトランスポートパケットTPの滞留時間に基づいて、基準クロックの周波数を調整する調整部17と、を備える。

(もっと読む)

送信装置、送信方法、受信装置、及び受信方法

【課題】マルチパスフェージング環境においても正確な同期タイミングを得ることができる送信装置、送信方法、受信装置、及び受信方法を提供すること。

【解決手段】送信データ列を周波数領域に変換した信号を時間領域信号に変換した信号を送信する送信装置において、第1のプリアンブルパターンの各ビットをn(nは2以上の整数)ビット及びk(kはk≠nである2以上の整数)ビット連続させたビット列を含む第2及び第3のプリアンブルパターンと前記第1のプリアンブルパターンとのうち少なくとも2つのプリアンブルパターンを出力するプリアンブルパターン生成部と、前記プリアンブルパターン生成部から出力された前記少なくとも2つのプリアンブルパターンを含む前記送信信号を送信する送信部とを備える。

(もっと読む)

位相調整装置

【課題】デジタル画像データとクロックとの位相を調整する場合に、投影画像による目視判断などを行わないで自動的に調整する。

【解決手段】データセレクタ104は、遅延回路101から並列に供給される互いに所定時間遅延時間の異なる複数の遅延クロックのうち、セレクト端子に供給されるnビットカウンタ値に応じた1種類の遅延時間の遅延クロックを選択する。ラッチ回路105は、デジタルデータをデータセレクタ104から出力された遅延クロックの立ち上がり及び立ち下りでラッチする。4段シフトレジスタ106は、ラッチ回路105からのデジタルデータを、データセレクタ104から出力された遅延クロックをシフトクロックとして4段シフトする。コンパレータ107は、4段シフトレジスタ106の入力デジタルデータと出力デジタルデータとを比較し、比較結果が一致する場合は、ラッチが正しくできていると判断する。

(もっと読む)

通信回路及びサンプリング調整方法

【課題】サンプリングクロックのタイミングを受信データのタイミングに合わせる通信回路及びサンプリング調整方法を提供することを目的とする。

【解決手段】入力される通信データのビットレートに対しm倍の周波数であり、通信データの1ビット周期にmより小さい奇数であるnパルス連続するサンプリングクロックを用いてサンプリングを行うサンプリング回路12と、通信データの1ビット周期にサンプリングされたn個の受信データの多数決により多数と判定された値の受信データを出力する多数決回路14と、n個の受信データのうち先頭近傍のデータが他のデータと異なっているときサンプリングクロックを所定量だけ遅らせ、n個の受信データのうち最後尾近傍のデータが他のデータと異なっているときサンプリングクロックを所定量だけ進めるサンプリングクロック調整手段24,34,35とを有する。

(もっと読む)

光パケットスイッチ装置

【課題】伝送路の帯域利用効率を向上できる光パケットスイッチ装置を提供する。

【解決手段】光パケットスイッチ装置10は、光スイッチ制御部13と、光スイッチ部16とを備える。光スイッチ制御部13は、光電変換部と、CDR部と、シリアル/パラレル変換部と、分周部と、パラレルデータ信号の中からフレーム同期パターンを検出すると共に、パラレルデータ信号の先頭ビットに対して何ビットずれた位置にフレーム同期パターンが格納されているかを示す遅延ビット数を検出する同期パターン検出部と、ヘッダを解析して、光パケット信号の光パケット長および方路情報を検出するヘッダ解析部と、ヘッダ解析部で検出された光パケット長および方路情報と、同期パターン検出部で検出された遅延ビット数情報とに基づいて、競合する光パケット信号の通過/破棄を判定する出力競合判定部34とを備える。

(もっと読む)

信号処理装置、及び信号処理方法

【課題】簡易な回路構成で入出力クロックの誤差を吸収すること。

【解決手段】所定数のデータと、第1のクロックに同期し、データが有効な区間でアクティブな状態をとる第1のイネーブル信号と、が入力される入力部と、第1のクロックよりも高速な第2のクロックを基準に、第1のイネーブル信号が非アクティブな状態をとる区間のクロック数をカウントするカウント部と、第2のクロックを基準に、所定数に等しいクロック数分だけ第2のイネーブル信号をアクティブな状態にし、カウント部によりカウントされたクロック数分だけ第2のイネーブル信号を非アクティブな状態にするイネーブル信号制御部と、第2のイネーブル信号を出力するイネーブル信号出力部と、第2のイネーブル信号がアクティブな状態をとる区間に、第2のクロックに同期して所定数のデータを出力するデータ出力部と、を備える信号処理装置が提供される。

(もっと読む)

受信装置及び方法、並びにプログラム

【課題】クロックの同期を確実にとることができるようにする。

【解決手段】短時間平均値監視部114は、バッファ112に順次蓄積される受信データの数秒ごとの蓄積容量の平均を示す短時間平均値を取得し、長時間平均値監視部115は、バッファ112に順次蓄積される受信データの数分ごとの蓄積容量の平均を示す長時間平均値を取得する。クロック制御部116は、取得された長時間平均値の評価結果に応じて、デコーダ113が受信データの処理を行うためのクロックの周波数を制御するとともに、取得された短時間平均値に基づいてパケットロスなどの異常が検出された場合、クロックの周波数の調整を停止し、その異常が検出されてから所定の時間が経過した後、クロックの周波数の調整を再開する。本発明は、例えば、ネットワークを利用した動画配信において動画を受信する受信装置に適用することができる。

(もっと読む)

データ送信装置及びデータ転送装置並びにデータ転送方法

【課題】ビット欠けが発生せずデータ受信装置に適した周波数でシリアルデータ転送できるようにする。

【解決手段】転送の一区間を繰り返して示すデータ転送サイクル信号5を受け、このデータ転送サイクル信号5からストローブパルスを繰り返して発生しこのストローブパルスにより連続してデータを受信するデータ受信装置に向けて、送信クロックに同期させてデータ転送サイクル信号5を送信するとともに、このデータ転送サイクル信号5に同期させてデータを連続して送信するデータ送信装置1において、データ送信装置1は、制御部2により、データ受信装置の受信クロックの周波数情報に基づいて、データを転送する一区間を示すデータ転送サイクル内に予め定めた数以上の受信クロックのクロック数が入るようにデータ転送サイクル幅4を決定し、送信部3により、制御部2が決定したデータ転送サイクル幅4を有するデータ転送の一区間内で一のデータを送信する。

(もっと読む)

位相同期装置および位相同期方法

【課題】無線回線を介して接続された装置間の位相同期を行うことが可能な位相同期装置を得ること。

【解決手段】マスタ側無線装置3は、マスタ装置1からの受信パケットから、位相同期の基準となるタイミングを抽出し、基準となるタイミングに同期して、スレーブ側無線装置4へパケットを送信するタイミングを決定し、受信パケットをスレーブ側無線装置4へ送信し、スレーブ側無線装置4は、マスタ側無線装置3からの受信パケットから、位相同期の基準となるタイミングを抽出し、抽出したタイミングと自装置内の動作タイミングとを比較して検出した位相差に基づいて、周波数偏差を検出し、位相差および周波数偏差に基づいて、自装置内の動作クロックの周波数を制御し、基準となるタイミングに同期してスレーブ装置2へパケットを送信するタイミングを決定し、受信パケットをスレーブ装置2へ送信する。

(もっと読む)

非圧縮データ送信装置及び受信装置

【課題】非圧縮データを、光通信網等を用いて効率的に長距離伝送する。

【解決手段】OC−192フレーマ115は、SDI/OC−192クロック変換部114から収容ワード数を入力し、所定のタイミングクロックを出力指示としてSDI/OC−192クロック変換部114に出力すると共に、この出力指示に対応するデータ及びRTS値を入力し、タイミングクロック毎に、収容ワード数、データ及びRTS値等をタイミングクロックに対応する位置に収容し、OC−192フレームを生成してスクランブラ116に出力する。これにより、SDIクロックによるHD−SDI信号のデータ列をOC−192基準クロックによるデータ列に変換することができ、クロック変換を実現することができる。そして、OC−192フレームの光信号は、伝送路3を介して受信装置2へ送信される。

(もっと読む)

2チャンネルネットワークシステム

【課題】ピュアアロハの低消費電力特性と、スロッテドアロハの高い周波数利用効率とを備えたネットワークシステムが求められている。

【解決手段】起動時は、従来のピュアアロハと同様に通信を行うが、各端末局は中央局からの受信確認信号を時計信号として用い、これに同期するようにパケット送信を行うことで、擬似的にスロッテドアロハとする。中央局の受信確認信号は、周期的なクロックパルスに同期して送信し、端末局は受信した受信確認信号に同期したクロック信号を生成し、当初の非同期状態から同期状態でパケット送信を行う形態に移行する。端末局の受信部は、パケットの送信後の所定の期間だけ動作状態にする。また、端末局の受信部は、動作状態期間を変化させて、受信確認信号を探索し、受信確認信号を受信できるように上記期間を維持することで、受信した受信確認信号に同期したクロック信号を生成する。

(もっと読む)

シリアルデータ受信装置

【課題】ノイズが発生した場合に正しいデータを取得することができるシリアルデータ受信装置を提供する。

【解決手段】調歩同期シリアル通信によるデータを受信するシリアルデータ受信装置は,受信データの立ち下がりを検出する立ち下がり検出部と,立ち下がりの検出に応じて,それぞれ異なるタイミングでビット長毎にサンプリングするための複数のサンプリングタイミングを生成するサンプリングタイミング生成部と,複数のサンプリングタイミングそれぞれで,スタートビットからストップビットまでのビット数又はそれより長い所定ビット数分サンプリングされた複数のデータ列を取得し,当該複数のデータ列のうち,少なくともスタートビットとストップビットが正常なデータ列を選択するデータ処理部とを備える。

(もっと読む)

クロック再生装置、クロック再生方法および制御プログラム

【課題】アダプティブクロック再生法を用いて同期を取っている時にパケット固定遅延を検出した場合でも、安定して送信端末と受信端末との同期を取る。

【解決手段】クロック再生装置10は、クロック出力手段50から受信したクロックに同期させてバッファ60からパケットを出力させると共に、バッファ60の蓄積量を計測して出力するバッファ制御手段20と、遅延の有無を監視し、遅延を検出した場合、遅延量を算出して出力する遅延検出手段30と、バッファ制御手段20から受信した蓄積量に基づいてクロック制御値を生成して出力すると共に、遅延検出手段30から遅延量を受信した場合、該遅延量に対応する期間、所定のクロック制御値を出力するクロック制御手段40と、クロック制御手段40から受信したクロック制御値に基づいてクロックを生成して出力するクロック出力手段50と、を備える。

(もっと読む)

偏差検出装置及び方法

【課題】伝送フレームのクロックとクライアント信号のクロックとの周波数偏差を高精度かつ高速に検出することが可能な偏差検出装置及び方法を提供すること。

【解決手段】本発明の一態様は、クライアント信号のクロックと伝送フレームのクロックとの周波数偏差を検出する偏差検出装置であって、前記クライアント信号のクロックをカウントする第1カウンタと、前記伝送フレームのクロックに複数の位相差を付与する位相シフタと、前記複数の位相差が付与された伝送フレームの各クロックを並列的にカウントする第2カウンタと、前記第2カウンタから出力される各クロックのカウント値を加算する加算処理部と、前記加算された合計カウント値を前記複数の位相差が付与された伝送フレームの各クロックの個数により平均化し、算出された平均値を前記周波数偏差として出力する平均処理部とを有する偏差検出装置に関する。

(もっと読む)

CDR回路、受信装置、および通信システム

【課題】簡易な回路構成で、高速かつジッタ入力に強く、信号エラーの発生を抑止することが可能なCDR回路、受信装置、および通信システムを提供する。

【解決手段】CDR回路310は、遅延素子312−1〜312−4を含み、定期的に信号遷移の挿入されたデータ入力をトリガとしてクロックを抽出する分周器320と、分周器で抽出されたクロックに同期して入力データ信号をラッチするラッチ315−1〜315−8とを有する。

(もっと読む)

差動4位相偏移変調の位相補間ベースのクロック及びデータの回復

【課題】方法は、N個の入力ストリームを受け取る工程を含む。

【解決手段】N個の入力ストリームおける入力データ・ビットに基づいて、回復されたクロック信号を生成する工程であって、回復されたクロック信号はクロック周波数及び回復されたクロック位相を有する工程と、回復されたクロック位相に対する個別の位相オフセットにおける個別の位相及びクロック周波数を有する回復されたクロック信号に基づいてN個の入力ストリームのうちの一入力データ・ビットストリームに対するクロック信号を生成する工程と、N個のそれぞれのクロック信号と、N個の入力ビットストリームそれぞれとの間の位相差を検出する工程と、それぞれの位相差をなくすようN個のクロック信号の位相を調節する工程である。

(もっと読む)

データ再生回路、局側光送受信装置及びデータ再生方法

【課題】高速かつ消費電力の低いバーストCDR回路を提供することを目的とする。

【解決手段】複数のクロックを生成する多位相クロック生成手段と、サンプリングデータを出力するサンプリング手段と、データの変化位相を検出する変化位相検出手段と、識別位相を決定する識別位相決定手段と、識別位相のクロックでサンプリングされたデータを選択し再生データを出力するデータ選択手段と、識別位相の変動が収束したかを判定し、収束した場合に収束通知信号を出力する収束判定手段と、その信号に基づいて変化位相検出手段の変化位相検出動作を予め定めた時間の間中止させる検出動作制御手段と、前記時間の間識別位相決定手段に収束位相を保持させる識別位相保持手段とを有し、変化位相検出動作を中止している時間の間は収束位相でサンプリングされたデータを選択して再生データを出力することを特徴とする。

(もっと読む)

ホストコントローラ、情報処理装置、およびサンプリング方法

【課題】 メモリカードからのデータを正しく得ることができ且つデータの転送効率を向上させることができるようにすること。

【解決手段】 実施形態によれば、ライトデータに対して返されるCRCステータスを対象に、位相が異なる複数のクロックに従ってサンプリングを行うことによって複数の値を取得する動作を繰り返す複数のデータ入力手段(25〜27)と、前記複数のデータ入力手段により取得された複数の値の中から、前記CRCステータスの値として正しく取得された値を識別し、データ転送が成功したか否かを示す判定結果を所定のデバイスに通知する制御手段(21)とを具備するホストコントローラが提供される。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

通信装置およびクロック同期方法

【課題】リング網において障害発生時のクロックソースの切替に要する時間を短縮する。

【解決手段】実施の1形態のノード10は、リング網36における第1方向の伝送路を介して伝送された第1クロック情報と、リング網36における第2方向の伝送路を介して伝送された第2クロック情報の少なくとも一方を用いて当該ノードの動作をマスタクロックに同期させる。ノード10は、リング網36における第1方向の伝送路で障害が検出された場合、第2クロック情報を用いてマスタクロックへの同期処理を実行させるための付加情報を第1クロック情報に設定してリング網の第1方向へ送出する。それとともに、その付加情報を第2クロック情報にも設定してリング網の第2方向へ送出する。

(もっと読む)

21 - 40 / 414

[ Back to top ]