Fターム[5K047MM46]の内容

デジタル伝送方式における同期 (12,489) | 装置、回路、機能 (2,875) | 基本回路、機能 (1,980) | PLL (330)

Fターム[5K047MM46]の下位に属するFターム

Fターム[5K047MM46]に分類される特許

1 - 20 / 286

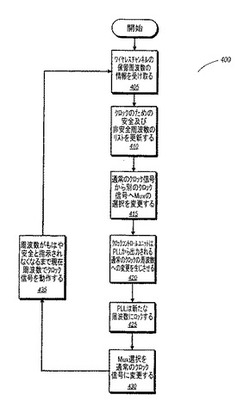

受信器PLL管理を伴う機敏なクロッキング

【課題】干渉を回避するためにクロック信号の周波数を変更する方法及び装置を提供する。

【解決手段】一実施形態において、第1のインターフェイスに搬送されるデータは、第1の周波数のクロック信号に同期される。信号は、別の周波数で第2のインターフェイスに搬送される。第2のインターフェイスに信号が搬送される周波数の変更に応答して、第1のインターフェイスに関連したクロックコントロールユニットが、第2の周波数へのクロック信号の変更を開始する。第2の周波数は、第2のインターフェイスに信号が搬送される周波数との干渉を生じないように選択される。クロック周波数の変更は、インターフェイスのクロックラインにおける擬似的アクティビティを防止するように遂行される。

(もっと読む)

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

半導体集積回路装置、及び、クロックデータ復元方法

【課題】インターポレータ方式のクロックデータ復元回路において、インターポレータ回路の広帯域化を行わず、マルチレートに対応したクロックデータ復元回路を実現する。

【解決の手段】インターポレータ回路の生成クロックを分周し、リカバリクロックを生成する。また、インターポレータ回路が生成するクロックの位相を制御するポインタは分周前のクロックを使い、その他の回路は分周後のリカバリクロックを使い動作する。

(もっと読む)

受信回路及びエラー検出方法

【課題】設計時のタイミング調整を容易とする受信回路及びエラー検出方法を提供すること

【解決手段】本発明にかかる受信回路は、位相の異なる複数のクロックを用いて、矩形波としてデータが遷移する受信シリアルデータビット列をサンプリングして、前記サンプリングされた受信シリアルデータビットを用いて受信データビット列を生成するDL回路部1と、前記サンプリングされた前記受信シリアルデータビットのうち、所定期間内に位相の異なるクロックを用いてサンプリングされた前記受信シリアルデータビットの値が一致するか否かを比較した結果に基づいて前記受信データビット列のエラー区間を検出するPD回路部2と、を備えるものである。

(もっと読む)

通信装置及び通信方法

【課題】PLL回路をベースとしたCDR回路を使用したトランシーバ間において、再同期を高速に行うことを目的とする。

【解決手段】PLL回路により構成されるクロック抽出部16に、受信信号を受信していない非受信状態の場合には、受信信号を受信している受信状態から非受信状態へ移行する時点におけるクロック信号の位相を示す位相情報を保持しておく受信側位相保持部22を追加する。データ送信時には、受信側位相保持部22が保持した位相情報を用いて生成されたクロック信号を用いて送信データを送信する。

(もっと読む)

通信装置、通信制御方法

【課題】周波数偏差に起因するクロックまたは時刻情報のずれを精度よく算出する通信装置、及び通信方法を提供すること

【解決手段】基準クロック生成部20は、クロック信号を出力する。無線部10は、クロック信号に基づいて、情報の送受信を行う。距離推定部40は、情報を送受信した時刻を示す複数の時刻情報に基づいて対向する通信装置との推定距離を算出する。補正部50は、推定距離と、予め設定された対向する通信装置との装置間距離と、の差分に基づいて、時計部30の生成する時刻情報または基準クロック生成部20の生成するクロック信号の補正処理を行う。

(もっと読む)

信号配線システム及びジッタ抑制回路

【課題】従来は、信号配線のジッタ量を削減しつつ、回路規模の増大化を抑制することが難しかった。

【解決手段】差動信号を出力する出力部と、前記出力部からの前記差動信号を受信する受信部と、前記受信部が受信する前記差動信号のジッタ量を、抑制係数に応じて抑制するジッタ抑制回路と、前記出力部からの前記差動信号を伝達し、前記ジッタ抑制回路の前記抑制係数に応じた配線長を有する信号配線部と、を有する信号配線システム。

(もっと読む)

クロック・データ再生部及びその電力制御方法並びにPONシステム

【課題】PONシステムの端末装置におけるクロック・データ再生部が省電力状態から起動する時の無駄な電力消費を低減し、かつ、迅速に確実な通信が可能となるようにする。

【解決手段】通常モード又は省電力モードの設定が可能であり、電圧制御型発振器243を含み、入力信号からクロック信号及びデータ信号を抽出する位相ロックループLpを備えたクロック・データ再生部24Aは、参照クロック信号を逓倍して出力する参照クロック逓倍回路249を備えるとともに、同じ電圧制御型発振器243を含み、位相ロックループLpが省電力モードから通常モードに移行する前に、参照クロック逓倍回路249を用いて電圧制御型発振器243による同期発振のトレーニングを行う周波数トレーニングループLfを備えている。

(もっと読む)

GPSジッタ低減装置

【課題】後段側の装置を軽量に設計することのできるGPSジッタ低減装置を得る。

【解決手段】位相比較調整処理部105は、GPS11が出力する1PPSと、出力パルス生成部104から出力される平滑化された1PPSとの位相差をカウントし、位相差目標値と比較して、固定値にて調整を実施する。出力パルス生成部104は、移動平均処理部103の出力と、位相比較調整処理部105の調整値に基づいて平滑化した1PPSを生成する。

(もっと読む)

無線通信装置

【課題】対象装置からの信号に基づいて当該対象装置と同期をとる構成において、非同期状態から同期状態へ早期に復帰することが可能な無線通信装置を提供する。

【解決手段】無線通信装置201は、対象装置から受信した受信データに基づいて生成された再生タイミング信号に基づいて第1の制御電圧を生成し、電圧制御発振器25に第1の制御電圧を供給することにより、再生タイミング信号の周波数成分のうち、所定の周波数以上の成分が減衰された周波数成分を有し、かつ再生タイミング信号に同期する基準タイミング信号を生成するためのジッタ抑圧部12と、タイミング信号生成部22によって生成される再生タイミング信号の異常を検知し、異常を検知した場合には、第1の制御電圧の代わりに、第1の所定範囲内の電圧である第2の制御電圧を電圧制御発振器25に供給するための発振器制御部13とを備える。

(もっと読む)

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

【課題】システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。

【解決手段】各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

複数のデバイスおよび柔軟なデータ整列を用いるメモリコントローラを有するシステムにおけるクロック再生およびタイミング方法

【課題】システムは、メモリコントローラおよび直列接続されている複数の半導体デバイスを備える。各デバイスはデータを格納する。コントローラは、デバイスの動作を同期させるクロックを供給する。

【解決手段】各デバイスは、イネーブル信号によって選択的にイネーブルまたはディセーブルされるPLLを備える。選択デバイスのPLLはイネーブル信号によってイネーブルされ、他のデバイスはディセーブルされる。イネーブルされたPLLは、90°の倍数の位相シフトで複数の再生クロックを供給する。データ転送は、再生クロックのうちの1つのクロックと同期する。ディセーブルされたPLLのデバイス内で、データ転送は入力クロックと同期する。イネーブルおよびディセーブルされたPLLにより、各デバイスはソース同期クロッキングおよび共通同期クロッキングを行う。最後のデバイスのデバイス識別子の最下位ビットがクロック整列を決定する。

(もっと読む)

シリアル通信装置及びその制御方法

【課題】内部回路との間で所定の同期クロックを用いて通信を行う送受信回路と、入力される基準クロックに基づいて上記同期クロックを発生するPLL回路とを備えたインターフェース回路を備えたシリアル通信装置において、インターフェース回路及び内部回路の誤動作を防止する

【解決手段】遅延回路5は、基準クロックREFCLKの周波数が100MHzで安定した後に発生されるリセット信号PERST#を、所定の遅延時間Δtだけ遅延させて内部リセット信号PERST2を発生し、リンクコントローラ31に出力する。PHY回路2は、リセット信号PERST#に応答してリセットされ、リンクコントローラ31は、内部リセット信号PERST2に応答してリセットされる。また、遅延時間Δtは、PLL回路23の回路仕様に基づいて予め計算されたロックアップ時間より長く設定される。

(もっと読む)

半導体装置

【課題】従来の半導体装置は、送信クロックの周波数が安定するまでに多くの時間を要する問題があった。

【解決手段】本発明の半導体装置は、送信クロックCLKから生成される受信クロックRCLKと入力信号RDと間の位相の進み又は遅れを示す位相差信号を生成し、受信クロックRCLKの位相を入力信号RDの位相に追従させる制御を行う位相追従ループと、受信クロックRCLKの周波数を入力信号RDの周波数に追従させる制御を行う周波数追従ループと、を有し、入力信号RDからデータ信号Sout及びデータ信号に対応する同期クロックSCLKの抽出を行うクロックアンドデータリカバリ回路13と、位相差信号に基づき生成される周波数差信号FPに応じて周波数調整信号Fadjにより示される値を増減させる周波数誤差調整器14と、周波数調整信号Fadjに基づき送信クロックCLKの周波数を増減させる発振器12と、を有する。

(もっと読む)

PONシステムの局側装置、クロックデータ再生回路及びクロック再生方法

【課題】 想定外の伝送レートの入力信号が入力されても、次の入力信号に対するクロックとデータの再生を適切かつ高速に行えるようにする。

【解決手段】 本発明は、位相ロックループと周波数ロックループのうちのいずれか一方に切り替え可能なデュアルループ方式のクロックデータ再生回路50に関する。この再生回路50は、各ループのうちのいずれか一方を選択的に動作させるセレクタ53と、各ループにおいてそれぞれ制御電圧を発生させ、周波数ロックループの動作中に制御電圧をいったん入力信号の到来前の中立状態に戻す電圧発生回路54と、を備える。

(もっと読む)

データ受信回路

【課題】高速で高精度のデータ受信を可能にするデータ受信回路の提供を図る。

【解決手段】入力データDataを受け取って遅延した遅延データを出力する可変遅延回路2と、データ取り込みクロックCLK1に従って前記遅延データを取得するデータ取得用フリップフロップ31と、クロック信号CLKを受け取ってフラクショナルクロックを出力するフラクショナルPLL回路1と、前記フラクショナルクロックCLK2に従って前記遅延データの位相検出を行う位相検出用フリップフロップ32と、該位相検出用フリップフロップの出力信号および前記データ取得用フリップフロップの出力信号から前記可変遅延回路における遅延量を制御して位相調整を行う位相調整回路4と、を有する。

(もっと読む)

位相同期装置、位相同期方法、およびプログラム

【課題】シンボル周期と非同期でサンプリングされた受信信号に基づくシンボル同期を、複数シンボル分並列してより迅速に行うことができるようにする。

【解決手段】離散サンプルを行うことによって得られたN個の受信信号の位相の、推定される受信シンボルの位相に対する位相誤差が位相誤差検出回路212により検出される。位相オフセットの更新に用いられる補正値として、時間に依存しない位相誤差補正値mP,kと、時間に依存する周波数誤差補正値mI,kがループフィルタ213により位相誤差に基づいて計算される。2つの補正値に基づいてNCO214により位相オフセットφk+1が計算され、オフセットφk+1に基づいて補間FIRフィルタ211により補間処理が行われることによって、受信シンボルが求められる。本発明は、データを受信する受信装置に適用することができる。

(もっと読む)

クロック位相同期回路

【課題】従属同期網に於けるクロック位相同期回路に関し、誤接続によるクロックループ接続状態の有無を判定する。

【解決手段】基準となる上位局からのリファレンス入力と電圧制御発振器1の出力信号又は分周器4により分周した信号との位相差を位相比較器3により求め、その位相差に対応した制御値を算出し、制御値に従った制御電圧を電圧制御発振器1に入力し、リファレンス入力に位相同期したクロックを出力するクロック位相同期回路であって、位相比較器3により求めた位相比較出力信号を基に、電圧制御発振器1の制御値を求める制御値演算部2と、この制御値演算部2により求めた制御値に所定の変動量を所定時間だけ加算して、制御値の変動経過を監視する監視制御部6とを備え、制御値算出部7により求めた制御値に、所定の変動量を所定時間加算したことによる制御値の変化を基に正常な従属同期網を構成しているか否かを判定する構成を備えている。

(もっと読む)

データ受信回路

【課題】 1つの高速クロックをもとに,高速データレート及び低速データレートに対応したデータを出力できるデータ受信回路を提供する。

【解決手段】 レシーバ回路3において,クロック信号発生部37のクロックとに基づいて,高速モードの場合に,デマルチプレクサ部33が,データラッチ部31のデータラッチ出力から,高速モードにおける33bitパラレルデータ及び312.5MHzクロック#1を生成する。また,低速モードの場合に,バウンダリ検出・低速データ抽出部34が,データラッチ部31のデータラッチ出力から中間パラレルデータを生成して,中央部でビットデータを抽出して低速モードにおける4bitパラレルデータを出力し,高速モードと低速モードのデータ周期比率をもとにクロックを調整して,12.5MHzクロック#2を生成する。

(もっと読む)

1 - 20 / 286

[ Back to top ]