国際特許分類[H01L21/20]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 基板上への半導体材料の析出,例.エピタキシャル成長 (11,073)

国際特許分類[H01L21/20]の下位に属する分類

物理的析出を用いるもの,例.真空蒸着,スパッタリング (536)

固体を析出させるガス状化合物の還元または分解を用いるもの,すなわち化学的析出を用いるもの (7,439)

液相成長を用いるもの (330)

国際特許分類[H01L21/20]に分類される特許

2,701 - 2,710 / 2,768

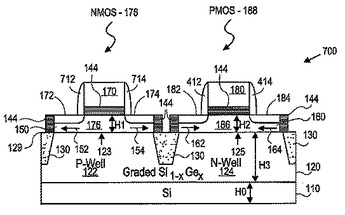

CMOS用歪トランジスタの集積化

【解決手段】CMOSデバイスに関連する本発明の様々な実施形態は、(1)選択的に蒸着されたシリコン材料が、第1の領域における傾斜シリコンゲルマニウム基板材料の格子面間隔より小さい、シリコン材料の格子面間隔によって引き起こされる引っ張り歪を経験するべく、傾斜シリコンゲルマニウム基板の第1の領域上に選択的に蒸着されたシリコン材料のNMOSチャンネル、および(2)選択的に蒸着されたシリコンゲルマニウム材料が、第2の領域における傾斜シリコンゲルマニウム基板の格子面間隔よりも大きい、選択的に蒸着されたシリコンゲルマニウム材料の格子面間隔によって引き起こされる圧縮歪を経験すべく、基板の第2の領域上に選択的に蒸着されたシリコンゲルマニウム材料のPMOSチャンネルを有する。

(もっと読む)

(もっと読む)

MIS型電界効果トランジスタ

下地SiGe層1上に歪みSi層2をエピタキシャル成長させ、ゲート絶縁膜3aとゲート電極4aを形成した後、ゲート電極4aをマスクにして、下地SiGe層1及び歪みSi層2に不純物をイオン注入し(図2(a))、活性化のための熱処理を行ってソース・ドレイン領域6を形成する(図2(b)、(c))。このとき、歪みSi層2の膜厚は、最終的なMISFETのソース・ドレイン領域6の不純物濃度が最大となる深さをTp(=Rp)としたとき、2Tp以下にする。 (もっと読む)

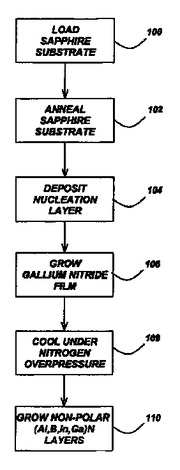

非極性(Al、B、In、Ga)N量子井戸

非極性a面GaN/(A1、B、In、Ga)N多重量子井戸(MQW)を製造する方法。a面MQWは、有機金属化学気相成長法(MOCVD)によって適切なGaN/サファイアテンプレート層上に成長し、井戸幅は20Å〜70Åの範囲である。a面MQWからの室温光ルミネセンス(PL)放射エネルギーは、自己無頓着ポアソン−シュレディンガー(SCPS)計算を使用してモデリングされた正方井戸傾向を伴った。最適PL放射強度は、a面MQWについて52Åの量子井戸幅で得られる。  (もっと読む)

(もっと読む)

MOSFET構造体内に歪みSiチャネルを形成する方法

基板(1)上に歪みSi層を形成する方法が、Si表面上のエピタキシャルSiGe層(4)の形成と、エピタキシャルSiGe層(4)の上部にSi層のエピタキシャル成長による歪みSi層の形成とを含み、Si層はエピタキシャル成長によって歪み状態にされ、基板(1)が、支持層(1)と、埋込み二酸化シリコン層(BOX)と、単結晶Si表面層(3)とを有するシリコン・オン・インシュレータ基板であり、その方法は、更に、Si表面層(3)をアモルファスSi層(3B)に、且つ、エピタキシャルSiGe層(4)の一部分をアモルファスSiGe層(5)に変換するためのSi表面層(3)とエピタキシャルSiGe層(4)のイオン注入であって、エピタキシャルSiGe層(4)の更なる部分が残存単結晶SiGe層(6)であるイオン注入を含み、アモルファスSi層(3B)と、アモルファスSiGe層と、残存単結晶SiGe層(6)とが、埋込み二酸化ケイ素層(BOX)に隣接しているアモルファスSi層(3B)と共に埋込み二酸化ケイ素層(BOX)上の積層(3B、5、6)を形成する。  (もっと読む)

(もっと読む)

スタック状テンプレート層の局部的なアモルファス化及び再結晶化によって形成される、選択された半導体結晶配向を有するプレーナ型基板

【課題】 異なる配向の半導体が共通のBOX層上に配置された、プレーナ型ハイブリッド配向半導体基板構造体を形成するための、より簡単で優れた方法を提供すること。

【解決手段】 異なる結晶配向の半導体層を有するプレーナ型基板を製造するための、スタック状テンプレート層の局部的なアモルファス化及び再結晶化を用いる方法が提供される。本発明の方法を用いて構築されるハイブリッド配向半導体基板構造体、及び、デバイスの性能を高めるために異なる表面配向上に配置された少なくとも2つの半導体デバイスを含む種々のCMOS回路と一体化されたこうした構造体が提供される。

(もっと読む)

多層アニール誘導無秩序化

【課題】 量子井戸混合(QWI)方法に関し、光半導体デバイス生成時にエネルギーバンドギャップを変更して、QWI処理を空間的に制御し、複数のバンドギャップをウエハ上と、デバイスと、基板表面に生成する。

【解決手段】 半導体基板表面の第1領域を、QWI開始材料を利用してパターニングし、基板に第1の熱処理サイクルを行い、第1領域に第1のバンドギャップを生成し、基板の表面の、第1領域と異なる第2領域を、QWI開始材料を利用してパターニングし、基板に第2の熱処理サイクルを行い、第2領域に第2のバンドギャップを生成し、累積バンドギャップを前記第1領域に生成し、累積バンドギャップでは前記第1および第2熱処理サイクルの結果が累積されている。

さらなる工程で累積バンドギャップを追加する。

(もっと読む)

半導体材料の中から選択された材料製の層から形成された多層ウェハの表面処理

本発明は、特異な熱特性を有する材料を備えた多層ウェハを処理する方法に関し、この方法は、二次欠陥を生じ得る高温熱処理ステップを含み、この方法は、高温熱処理ステップの前にウェハ表面準備ステップを含むことを特徴とする。 (もっと読む)

Si:C−OIおよびSGOI上のシリコン・デバイスならびに製造方法

【課題】より費用効果が高くより簡略な、大きな引張り応力および圧縮応力をそれぞれnFETおよびpFETのチャネル中で生成する方法を提供すること。半導体構造および製造方法を提供すること。

【解決手段】この製造方法は、基板中に浅いトレンチ分離(STI)(25)を形成するステップと、基板上に第1の材料(30)および第2の材料(40)を設けるステップとを含む。第1の材料(30)および第2の材料(40)は、熱アニール・プロセスによって基板中に混合され、それぞれnFET領域の第1のアイランド(50)、およびpFET領域の第2のアイランド(55)を形成する。第1のアイランド(50)および第2のアイランド(55)の上に、材料層を形成する。STIは、緩和して、第1のアイランド(50)および第2のアイランド(55)の緩和を促進する。第1の材料(30)は、堆積または成長させたGe材料とすることができ、第2の材料(40)は、堆積または成長させたSi:CまたはCとすることができる。第1のアイランド(50)および第2のアイランド(55)の少なくとも一方の上に、歪みSi層を形成する。

(もっと読む)

レーザによりポリシリコン薄膜をアニールする光学系

被加工物の薄膜における配向又は結晶成長の変換を実行するためのガス放電レーザ結晶化装置であって、パルスドーズ制御に対してパルスを用いて光パワー及び高繰り返しレートでレーザ出力光パルスビームを生成するXeFレーザシステムを構成する主発信パワー増幅器MOPA又はパワー発信器パワー増幅器と、レーザ出力光パルスビームから伸長され

た細いパルス化作用ビームを発生させる光学系とを、有するガス放電レーザ結晶化装置について開示している。その装置において、レーザシステムはPOPAレーザシステムとして構成され、第1レーザPOユニットから第2レーザPAユニットに第1出力レーザ光パルスビームを方向付けるように動作されるリレー光学系と、第1レーザ出力光パルスビームの拡大として第2レーザ出力光パルスビームを発生するように、パルス又は−3nsec内で第1及び第2レーザユニットにおいてガス放電の発生のタイミングを合わせるタイミング及び制御モジュールとを更に有することが可能である。そのシステムは、発信器レーザユニットにおいて発散制御部を有することが可能である。発散性御部は不安定発振制御部を有することが可能である。そのシステムは、レーザと被加工物との中間にビームポインティング制御機構及びビーム位置制御機構を更に有することが可能である。ビームパラメータ計測法は、ビームポインティング制御機構に対するアクティブフィードバック制御部とビーム位置制御機構に対するアクティブフィードバック制御部とを与えることが可能である。  (もっと読む)

(もっと読む)

半導体基板を作製する方法

【課題】絶縁体上歪み半導体(SSOI)基板を作製する方法が提供される。

【解決手段】この方法で、歪み半導体は、あらかじめ形成された絶縁体上半導体基板の絶縁体層の上に直接配置された50nm未満の厚さを有する薄い半導体層である。本発明のSSOI基板を形成する際に、ウエハボンディングは使用されない。

(もっと読む)

2,701 - 2,710 / 2,768

[ Back to top ]