国際特許分類[H01L21/20]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 基板上への半導体材料の析出,例.エピタキシャル成長 (11,073)

国際特許分類[H01L21/20]の下位に属する分類

物理的析出を用いるもの,例.真空蒸着,スパッタリング (536)

固体を析出させるガス状化合物の還元または分解を用いるもの,すなわち化学的析出を用いるもの (7,439)

液相成長を用いるもの (330)

国際特許分類[H01L21/20]に分類される特許

2,731 - 2,740 / 2,768

結晶シリコン系薄膜太陽電池の製造方法及びそれを用いて形成した太陽電池

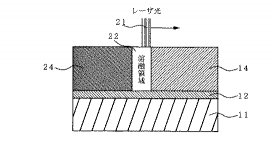

【課題】高い変換効率を有し、高スループットの結晶シリコン系薄膜太陽電池の製造方法及びそれを用いて形成した太陽電池を提供するものである。

【解決手段】本発明に係る結晶シリコン系薄膜太陽電池40の製造方法は、基板上に結晶性シリコン層を有する結晶シリコン系薄膜太陽電池を製造する際に、上記結晶性シリコン層とは異なる材料からなる異種基板11上に、順に、結晶性シリコン前駆体層14よりも融点が高い物質で構成される電極層12、非晶質シリコン又は結晶成分を含む非晶質系シリコンからなる結晶性シリコン前駆体層14を形成し、その前駆体層14に半導体レーザのレーザ光21を照射し、前駆体層14を溶融・結晶化して上記結晶性シリコン層24を形成するものである。

(もっと読む)

マスクを通るラテラル成長による窒化ガリウム基板の製造とそれから製作されたデバイス

多段を用いたエピタキシャルラテラルオーバーグロースにより窒化ガリウム基板の成長を行う。開口部領域を有するマスクされた基板上で、選択的成長により最初に三角形ストライプを作成すると、大部分の貫通転位は90°曲がる。第2段では、成長条件を変化させてラテラル成長速度を高め、平坦な(0001)面を生じさせる。この段階で、表面上の転位密度は<5×107cm-2である。転位は主に、2つのラテラル成長したファセットがぶつかり合って合体した合体領域に存在する。転位密度をさらに低下させるため、2回目のマスキング工程を開口部が1回目のそれの真上にくるように行う。合体領域の貫通転位(TD)は上層には伝播しない。したがって、転位密度は全表面にわたって<1×107cm-2まで低下する。  (もっと読む)

(もっと読む)

ヘテロエピタキシのためのコンプライアント基板、ヘテロエピタキシャル構造、及びコンプライアント基板を製造する方法

【課題】ヘテロエピタキシ用のコンプライアント基板と、ヘテロエピタキシャル構造と、ヘテロエピタキシ用のコンプライアント基板を製造する方法を提供する。

【解決手段】コンプライアント基板1は、キャリア基板2と、埋込層3と、単結晶の最上層4とを含み、埋込層3は上記キャリア基板2と最上層4との間にあり、最上層の領域及び/又は上記埋込層と上記最上層との間の界面の又はその近傍の領域5が弱められる。

(もっと読む)

薄膜トランジスタを備えた平板表示装置

【課題】 薄膜トランジスタを備えた平板表示装置を提供する。

【解決手段】 各駆動薄膜トランジスタの活性層の結晶粒の差によって、そして、駆動薄膜トランジスタの活性層のサイズを変更せずホワイトバランスを合せ、各副画素に最適の電流を供給することによって適正な輝度を得、寿命を短縮させないようにするためのものであって、自己発光素子を備えた複数の副画素を含む画素と、前記各副画素に備えられて少なくともチャンネル領域を有する半導体活性層を備え、前記自己発光素子に各々接続されて電流を供給するものであって、前記活性層の少なくともチャンネル領域が前記副画素別にその結晶粒のサイズまたは形状が相異なるように備えられた駆動薄膜トランジスタと、を含むことを特徴とする平板表示装置。

(もっと読む)

薄膜トランジスタを具備したフラットパネルディスプレイ

【課題】 駆動用TFTの活性層の大きさを変更せずに、同じ駆動電圧を加えた状態でもホワイトバランスを合わせられるフラットパネルディスプレイを提供する。また、各副画素に最適の電流を供給することによって適正な輝度を実現し、寿命が長いフラットパネルディスプレイを提供する。

【解決手段】 自発光素子を具備する複数の副画素を含む画素と、前記副画素の各々に備えられた、少なくともチャンネル領域を有する半導体活性層を具備し、前記自発光素子に電流を供給するために前記自発光素子に接続されてなる、駆動用薄膜トランジスタ(20r、20g、20b)とを含むフラットパネルディスプレイであって、前記半導体活性層のチャンネル領域が、少なくとも2つの前記副画素に関して相異なる方向に配置されてなることを特徴とするフラットパネルディスプレイである。

(もっと読む)

半導体装置の製造方法

【課題】閾値電圧の絶対値を低く抑えながら、オフリーク電流を低下させることができる半導体装置の製造方法を提供する。

【解決手段】Nチャネル型TFT形成予定領域内のpoly−Si層4にリンを注入することにより、n+領域8を形成した後、Pチャネル型TFT形成予定領域にのみ開口部が存在するレジストマスク9を用いて、ボロンのイオン注入を行うことにより、Pチャネル型TFTのソース・ドレイン領域となるp+領域10を形成する。次に、レジストマスク9を残存させたまま、水素注入を行うことにより、Pチャネル型TFT形成予定領域内において、チャネル領域(poly−Si層4)及びソース・ドレイン領域(p+領域10)の水素化処理を行う。このような方法によれば、Nチャネル型TFTに対する水素化処理が行われないため、Nチャネル型TFTにおける不要な閾値電圧の遷移が防止され、オフリーク電流の上昇を回避することができる。

(もっと読む)

半導体装置、および薄層歪緩和バッファ成長方法

本発明は、半導体基板を含み、その上部に少なくとも薄層歪緩和バッファを有し、本質的に3層のスタックから成っている半導体装置に関するものであり、その薄層歪緩和バッファは半導体装置のアクティブ部分でなく、さらに、薄層歪緩和バッファを形成する前記3層が本質的に一定のGe濃度を有することを特徴としている。前記3層は以下の通りである:Si1−xGexの第1エピタキシャル層、xはGe濃度である;前記第1エピタキシャル層上の、Si1−xGex:Cの第2エピタキシャル層、Cの量は少なくとも0.3%である;前記第2層上のSi1−xGexの第3エピタキシャル層。

(もっと読む)

(もっと読む)

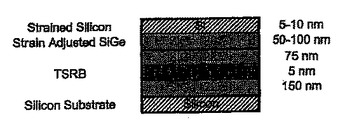

歪みシリコン・オン・インシュレータ(SSOI)およびこれを形成する方法

【課題】 コストが低く歩留まりの高い、引っ張り歪みSOI層を形成するための方法および引っ張り歪みSOI層の構造を提供する。

【解決手段】 歪みSiベースの層を製造するための方法、この層に製造されるデバイス、ならびに、かかる層およびデバイスを含む電子システムを開示する。この方法は、基板上にSiGe層をエピタキシャル成長させるステップと、このSiGe層において様々なGe濃度を生成するステップを含む。SiGe層内のGe濃度は、Ge濃度が突然かつ著しく増大する固有のGeオーバーシュート・ゾーンを含む。SiGe層上に、Siベースの層をエピタキシャル堆積させ、これによって引っ張り歪みが与えられる。また、典型的にSiまたはSiGeである歪みSiベースの層を、異なるバルク基板または絶縁体に転写可能であることも開示される。

(もっと読む)

化合物薄膜太陽電池およびその製造方法

【目的】裏面電極上に形成されたp型化合物半導体からなる光吸収層の上にヘテロ接合のためのn型のバッファ層を設けてなる化合物薄膜太陽電池の製造方法にあって、CBD法によりバッファ層を形成するに際して、溶液の混合および温度を制御することによって光吸収層の界面へのn型ドーパントの拡散とバッファ層の形成の最適化を図って接合性の良い特性の安定したpn接合を得ることができるようにする。

【構成】光吸収層の界面へn型ドーパントを拡散させる第1の工程と、表面反応律速領域による第1のバッファ層61を形成する第2の工程と、供給律速領域による第2のバッファ層62を第1のバッファ層に重ねて形成する第3の工程とをとるようにする。

(もっと読む)

シリコン結晶化方法

【課題】 短い時間で良質の結晶成長をなすことができるポリシリコンの結晶化方法を提供する。

【解決手段】 非晶質シリコン薄膜が蒸着された基板110にあって、固定手段とレーザー発生装置間の遮断領域と階段状の透過領域で構成されたマスクにレーザービームを照射して、前記非晶質シリコン薄膜に照射された領域が溶融した領域との界面でグレーンが各々成長して、第1グレーン領域114aと核生成領域と第2グレーン領域114bで構成された階段状の領域を形成する第1結晶化段階と;前記マスクを横長さだけ移動して、同一な照射した後に再結晶化して、重畳された部分のグレーンが成長して、横方向に新しい結晶領域が形成される第2結晶化段階を含む方法。

(もっと読む)

2,731 - 2,740 / 2,768

[ Back to top ]