国際特許分類[H01L21/20]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 基板上への半導体材料の析出,例.エピタキシャル成長 (11,073)

国際特許分類[H01L21/20]の下位に属する分類

物理的析出を用いるもの,例.真空蒸着,スパッタリング (536)

固体を析出させるガス状化合物の還元または分解を用いるもの,すなわち化学的析出を用いるもの (7,439)

液相成長を用いるもの (330)

国際特許分類[H01L21/20]に分類される特許

2,691 - 2,700 / 2,768

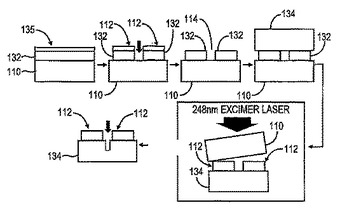

材料層の分離方法

リフトオフ工程を用いて、材料層と基板との間の界面を照射することによって基板から材料層を分離する。一実施例では、層を、基板上のダイに対応する複数のセクションに分離し、均一なビームスポットを整数の数のセクションをカバーするような形状にする。  (もっと読む)

(もっと読む)

歪みシリコンオンインシュレータ構造を製造する方法およびそれによって形成された歪みシリコンオンインシュレータ構造

【課題】シリコンの活性層を基板から分離する埋め込み絶縁層の活性層の下にある領域の厚さを増加させることによって形成されるシリコン活性層の局所的に歪んだ領域を有するシリコンオンインシュレータ(SOI)デバイスおよび構造を提供する。

【解決手段】絶縁層の活性層の下にある肥厚領域からその上にある歪んだ領域へと伝達される応力が、活性層の閉じ込められた領域において担体移動度を増加させる。シリコン活性層およびその上に形成されたデバイスは、隔置された歪んだ領域内の担体移動度の増加から恩恵を受けることができる。

(もっと読む)

採取薄膜の品質改善熱処理方法

本発明はドナー基板(10)から採取する層(1’、2)を備える構造(30)の形成方法に関するものであり、該ドナー基板は採取前にゲルマニウムを含む半導体材料でできた第一層(1)を具備し、該方法は以下のステップ、すなわち(a)ゲルマニウムを含む前記第一層(1)の厚さ内で脆化ゾーン(4)を形成するステップ、(b)受容基板(20)へドナー基板(10)を接着するステップ、(c)エネルギーを供給するステップであって、それにより脆化ゾーン(4)でドナー基板(10)を脆化するステップを含み、ドナー基板に少なくとも二つの異なる核種を共注入してステップ(a)を実施し、300℃〜400℃の間に含まれる温度で30分〜4時間熱処理を行ってステップ(c)を実施することを特徴とする。  (もっと読む)

(もっと読む)

半導体装置の製造方法および半導体検査装置

本発明に係る半導体装置の製造方法および半導体検査装置により、図2のフローに示すように、レーザ処理工程13で、SPC工程12処理後の基板の中から抜き取られたモニタ基板に、異なるレーザパワーで、異なる場所にレーザ処理を行い、基板全領域に多結晶シリコン膜を形成した後、最適パワー検査抽出工程14でモニタ基板上に形成された膜質の異なる多結晶シリコン膜を検査装置で測定し、レーザパワーの最適値が求められ、レーザ処理工程13で後続のSPC工程処理後の基板表面に、最適なレーザパワーに設定されたレーザが照射され、基板全領域で高品質な多結晶シリコン膜が製造される。  (もっと読む)

(もっと読む)

ナノチューブ・コンタクトを用いた半導体デバイスおよび方法

【課題】 1つ以上の半導体層に対して接触抵抗を低下するコンタクト層を備えたナノチューブを含む電子および光電半導体デバイスを提供する。

【解決手段】 半導体デバイスは、少なくとも1つの半導体層と、半導体層と電気的に接触する金属層と、金属層と半導体層との間に介在するカーボン・ナノチューブ・コンタクト層とを含む。コンタクト層は、金属層を半導体層に電気的に結合し、低い比接触抵抗を有する半導体コンタクトが得られる。コンタクト層は、可視光範囲の少なくとも一部において、実質的に光透過膜となることができる。

(もっと読む)

高速CMOS共存Ge−オン−インシュレータ光検出器の構造および製作方法

【課題】SiCMOS技術と共存可能な高速高効率光検出器を作る問題に対処すること。

【解決手段】本構造は、薄いSOI基板の上のGe吸収層から成り、分離領域、交互になるn型およびp型コンタクト、および低抵抗表面電極を利用する。本デバイスは、下の基板で生成されたキャリアを分離するために埋込み絶縁物を利用して高帯域幅を、Ge吸収層を利用して広いスペクトルにわたった高量子効率を、薄い吸収層および狭い電極間隔を利用して低電圧動作を、さらに平面構造およびIV族吸収材料の使用によってCMOSデバイスとの共存性を、達成する。本光検出器を製作する方法は、薄いSOIまたはエピタキシャル酸化物へのGeの直接成長および高品質吸収層を達成するための後の熱アニールを使用する。この方法は、相互拡散に利用可能なSiの量を制限し、それによって、下のSiによるGe層の実質的な希釈を起こすことなく、Ge層をアニールすることができるようになる。

(もっと読む)

シリコン結晶化方法

【課題】本発明はレーザービームの発生装置の負荷を減少させ、寿命を増加させることができるシリコン結晶化方法、それを用いたシリコン結晶化装置、それを用いた薄膜トランジスタ、それを用いた薄膜トランジスタの製造方法及び表示装置を提供する。

【解決手段】300Hzより大きいパルス周波数を有する光が発生される。光は所定時間の間少なくとも一つのアモルファスシリコン薄膜に照射され初期ポリシリコン結晶を形成させる。光は所定方向に移送され初期ポリシリコン結晶を成長させる。減少された出力エネルギーを有するレーザービームがアモルファスシリコン薄膜上に照射されアモルファスシリコン薄膜をポリシリコン薄膜で結晶化させ、レーザービーム発生装置の負荷は減少され寿命は増加される。

(もっと読む)

決定可能な熱膨張係数を有する基板

本発明は、結晶材料から選択された材料で作られた転写層(20)を受ける目的の複合支持基板(10)に関し、したがって、その集合体は、エピタキシャル用基板(30)を形成し、主要表面と平行に対称な長手方向の平面(100)を有し、且つ規定の温度Tで第1熱膨張係数を有し、対称平面のどちらの側にも横方向に延在する中央第1層(1)と、少なくとも1対の横方向の層(2、2’;3、3’)、即ち、互いに向き合う層を有する各対の層であって、前記対称平面に関して、ほぼ対称である複合支持基板(10)内の配列、前記温度Tで互いにほぼ同一である第2熱膨張係数、互いにほぼ同一である厚さ、である前記各対の層と、からなり、並びに、前記複合支持基板(10)が前記温度Tで転写層(20)の材料の熱膨張係数に近い全体的熱膨張係数を前記温度Tで有するように、前記複合支持基板(10)の層を構成する材料が、選択されていることを特徴とする。本発明は、前記複合支持基板上に有効層を形成する工程及びエピタキシャル基板を含む構造にも関係する。  (もっと読む)

(もっと読む)

ダイアモンド基板上炭化珪素並びに関連するデバイス及び方法

ワイドバンドギャップ材料内に、接合温度低下、動作中の高電力密度化、及び定格電力密度における信頼性向上を達成する高電力デバイスを形成する方法を、結果的に得られる半導体構造及びデバイスと共に開示する。本方法は、ダイアモンドの層を炭化珪素ウェハに添加して、得られる複合ウェハの熱伝導率を高め、その後、炭化珪素の上におけるエピタキシャル成長を支持するためにその十分な厚さを保持しつつ、複合ウェハの炭化珪素部分の厚さを削減し、複合ウェハの炭化珪素面を、その上におけるエピタキシャル成長のために、準備し、第III族窒化物ヘテロ構造を、ウェハの準備した炭化珪素面に添加することを含む。  (もっと読む)

(もっと読む)

シャロウトレンチ分離プロセスおよび構造

集積回路(IC)を製造する方法は、シャロウトレンチ分離(STI)技術を利用する。シャロウトレンチ分離技術は歪みシリコン(SMOS)プロセス中において使用される。トレンチ(34)を形成した後、歪み材料(36)を形成する。このプロセスは、埋込酸化膜(BOX)層(14)上の化合物半導体層16上で利用される。  (もっと読む)

(もっと読む)

2,691 - 2,700 / 2,768

[ Back to top ]