国際特許分類[H01L21/265]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 波または粒子の輻射線の照射 (3,567) | 高エネルギーの輻射線を有するもの (2,981) | イオン注入法 (2,159)

国際特許分類[H01L21/265]の下位に属する分類

マスクを用いるもの (145)

国際特許分類[H01L21/265]に分類される特許

21 - 30 / 2,014

半導体装置の製造方法

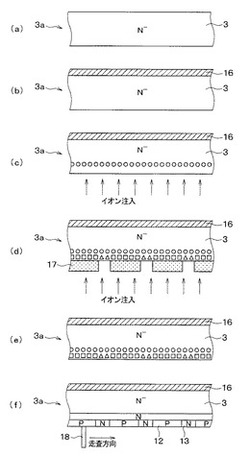

【課題】レーザを照射して不純物を活性化させる半導体装置の製造方法において、半導体基板の裏面に凹凸が形成されることを抑制することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板3aを用意し、半導体基板3aの裏面から活性化層12、13を構成するための不純物をイオン注入するイオン注入工程を行う。その後、半導体基板3aの裏面から、第1レーザ18aと、第1レーザ18aよりエネルギーが低くされていると共に波長が長くされており、第1レーザ18aの照射スポットと少なくとも一部が重なる照射スポットとされた第2レーザ18bとを同時に照射しながら走査し、第1レーザ18aによって不純物を活性化させて活性化層12、13を形成する活性化工程を行う。

(もっと読む)

エネルギー線照射装置及びワーク搬送機構

【課題】エネルギー線照射システムにおいて、ワークに効率的にエネルギー線を照射できるようにしながらも、飛躍的なコンパクト化を可能とする。

【解決手段】エネルギー線IBを所定の照射領域Pに向かって射出するエネルギー線射出機構と、前記エネルギー線IBが照射される対象物である第1ワークW1を、前記照射領域Pを含む第1周回軌道O1に沿って周回させる第1周回機構1と、前記エネルギー線が照射される対象物である第2ワークW2を、前記照射領域P1を含む第2周回軌道O2に沿って周回させる第2周回機構2とを具備し、各周回軌道によって形成される仮想の周回面と垂直な方向から視たときに、前記第1周回軌道O1で囲まれる領域と前記第2周回軌道O2で囲まれる領域との少なくとも一部が重なるように構成した。

(もっと読む)

半導体装置、半導体基板、半導体装置の製造方法、及び半導体基板の製造方法

【課題】エピタキシャル層に残存する転位の数を少なくする。

【解決手段】第2エピタキシャル層200は、第1エピタキシャル層100上にエピタキシャル成長している。第1エピタキシャル層100は、エピタキシャル成長層110及び欠陥層120を有している。欠陥層120は、エピタキシャル成長層110の上、かつ、第1エピタキシャル層100の表層に位置している。欠陥層120の欠陥密度は、5×1017cm−2以上である。欠陥層120を突き抜けた欠陥は、第2エピタキシャル層200の内部でループを形成している。

(もっと読む)

イオン注入装置及びイオン注入方法

【課題】正確なドーズ量制御を実現できるイオン注入方法を提供する。

【解決手段】ウエハ17へのイオン注入中に、イオンビーム電流を計測するとともに、真空ビームライン室20または真空処理室30内で動作する構造体の位置の変化に応じて変化する真空コンダクタンスの変化を求め、さらに上記真空ビームライン室または真空処理室内に設置された真空計21で計測される1個所ないし複数個所の真空度の変化を検知し、上記求めた真空コンダクタンスと1個所ないし複数個所の真空度とを用いてイオンビーム電流量を補正し、ウエハに注入するドーズ量を制御する。

(もっと読む)

熱処理方法

【課題】シリサイドの横方向への異常成長を防止しつつ、シリサイド形成を行うことができる熱処理方法を提供する。

【解決手段】半導体ウェハーWのソース・ドレイン領域にシリコンなどのイオンを注入し、そのイオン注入領域150を非晶質化する。非晶質化されたイオン注入領域150にニッケル膜158を成膜する。ニッケル膜158が成膜された半導体ウェハーWにフラッシュランプから第1照射を行ってその表面温度を予備加熱温度T1から目標温度T2にまで1ミリ秒以上20ミリ秒以下にて昇温する。続いて、フラッシュランプから第2照射を行って半導体ウェハーWの表面温度を目標温度T2から±25℃以内の範囲内に1ミリ秒以上100ミリ秒以下維持する。これにより、ニッケルシリサイドが縦方向に優先的に成長する。

(もっと読む)

対称プラズマ処理チャンバ

【課題】改良されたプラズマ均一性制御のための電気的な、ガス流の、及び熱的な対称性を向上させたプラズマ処理装置を提供する。

【解決手段】処理領域102を囲む蓋アセンブリ110及びチャンバ本体アセンブリ140と、チャンバ本体アセンブリ140内に配置された基板支持アセンブリ160と、チャンバ本体アセンブリ140によって排気領域104を画定する排気アセンブリ190であって、チャンバ本体アセンブリ140は処理領域102を排気領域104と流体接続する基板支持アセンブリ160の中心軸CAの周りに対称的に配置された複数のアクセスチューブ180を含む。

(もっと読む)

貼り合わせSOIウェーハの製造方法

【課題】 本発明は、SOI層の膜厚の面内均一性の良好なSOIウェーハを製造する方法を提供することを目的とする。

【解決手段】 イオン注入層が形成されたボンドウェーハのイオン注入された側の表面とベースウェーハの表面とを絶縁膜を介して貼り合わせた後、前記ボンドウェーハの一部を前記イオン注入層で剥離して、貼り合わせSOIウェーハを作製し、その後、平坦化処理を行う貼り合わせSOIウェーハの製造方法であって、

前記剥離後の貼り合わせSOIウェーハに対し、前記SOI層表面の周辺部の自然酸化膜が除去され、中央部の自然酸化膜が残存するように、水素ガスを含む雰囲気でRTA処理を行い、前記中央部に自然酸化膜が残存した貼り合わせSOIウェーハに対し、前記SOI層の面内膜厚レンジが1.5nm以下となるように前記平坦化処理を行うことを特徴とする貼り合わせSOIウェーハの製造方法。

(もっと読む)

高電子移動度トランジスタ

【課題】電子移動度を低下させることなく、電子密度を高くできる高電子移動度トランジスタを提供する。

【解決手段】Si基板100上に形成されたバッファ層10と、バッファ層10上に形成されたGaN層11と、GaN層11上に形成されたAlGaN層12と、AlGaN層12内に形成されると共に、互いに間隔をあけて形成されたソース電極13とドレイン電極14と、AlGaN層12上かつソース電極13とドレイン電極14との間に形成されたゲート電極15と、ソース電極13とドレイン電極14およびゲート電極15が形成されたAlGaN層12の一部を覆うように形成された絶縁膜16とを備える。上記絶縁膜16中にCsの原子が2×1013cm−2以上存在する。

(もっと読む)

シリコンオンインシュレーター構造体の製造方法

【課題】バブル欠陥が少ない埋込み酸化物層を有する厚さ25nm以下シリコンオンインシュレーター構造体を提供すること。

【解決手段】(a)シリコン層を含むドナー基板及び支持基板を提供するステップであり、両基板の一方のみが酸化物層で覆われているもの、(b)ドナー基板においてシリコン層の境界となる弱帯を形成するステップ、(c)酸化物層をプラズマ活性化するステップ、(d)ドナー基板を支持基板に接合するステップであり、酸化物層が接合界面に配置され、接合が部分真空中で実行されるもの、(e)接合強化アニールを350℃以下の温度で行うステップであり、アニールはドナー基板を弱帯に沿って劈開させるもの、(f)シリコンオンインシュレーター構造体に対し、900℃超の温度で欠陥を修復する熱処理を加えるステップであり、(e)から(f)への温度遷移が10℃/s超の勾配率であるものを含むシリコンオンインシュレーター構造体の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】注入した導電性不純物により形成される結晶欠陥の密度を低減し、歩留まり率が向上するような半導体装置の製造方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板を加熱することにより、半導体基板の基板温度を200から500℃の間の所望の温度に維持すると同時に、半導体基板に導電性不純物をイオン注入法もしくはプラズマドーピング法を用いてドーピングし、ドーピングした導電性不純物を活性化させるための活性化処理を行う。

(もっと読む)

21 - 30 / 2,014

[ Back to top ]