国際特許分類[H01L21/768]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 1つの共通基板内または上に形成された複数の固体構成部品または集積回路からなる装置またはその特定部品の製造または処理;集積回路装置またはその特定部品の製造 (40,275) | グループ21/70で限定された装置の特定部品の製造 (8,583) | 装置内の別個の構成部品間に電流を流すため使用する相互接続を適用するもの (5,422)

国際特許分類[H01L21/768]に分類される特許

1,011 - 1,020 / 5,422

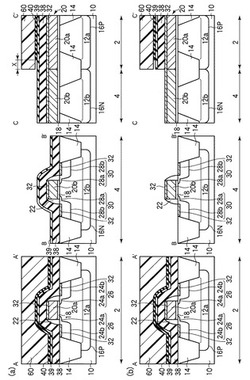

半導体装置及びその製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置及びその製造方法を提供する。

【解決手段】第1応力膜38上に第1ストッパ膜39及び第2ストッパ膜40を形成する工程と、第1領域2を覆う第1マスク60をマスクとし、第1ストッパ膜をストッパとして、第2領域4内の第2ストッパ膜をエッチングするとともに、第1領域のうちの第2領域に近接する部分の第2ストッパ膜をサイドエッチングする工程と、第2ストッパ膜とエッチング特性が異なる第2応力膜42を形成する工程と、第2領域を覆い、第1領域側の端面が第2ストッパ膜上に位置する第2マスクとし、第2ストッパ膜をストッパとして、第2応力膜の一部が第1応力膜の一部及び第2ストッパ膜の一部と重なり合うように第2応力膜をエッチングする工程と、第1領域と第2領域との境界部におけるゲート配線20に達するコンタクトホールを形成する工程とを有している。

(もっと読む)

配線基板、半導体装置、及びそれらの作製方法

【課題】集積化が進む配線基板、又は半導体装置において、導通不良を軽減する。信頼性の高い配線基板、又は半導体装置を歩留まり良く作製する。

【解決手段】多層配線構造を有する配線基板、又は半導体装置において、該配線に用いる導電層の接続構造に曲面を有する導電層を用いる。周囲の絶縁層の除去によって露出された下層の導電層の先端部は曲面であり、下層の導電層上に積層する上層の導電層の被覆性を良好とすることができる。曲面な表面を有するレジストマスクを用いて導電層をエッチング加工することによって曲面な表面を有する導電層を形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の内壁に絶縁膜を形成することにより、接続孔の径を小さくする場合において、接続孔内に導電膜を十分に埋め込むことができるようにする。

【解決手段】接続孔210,220の内壁上に絶縁性の第1膜300を形成し、接続孔210,220の径を細らせる。次いで、第1膜300が形成された接続孔210,220内に、第2膜50を埋め込む。次いで、絶縁膜200の表層を、CMP法を用いて除去する。次いで、接続孔210,220から第2膜50を除去する。次いで、接続孔210,220の第1膜300上および接続孔210,220の底面上にバリアメタル膜330を形成し、さらに接続孔210,220内に導電膜からなるコンタクト310,320を埋め込む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の配線間容量を低減する。

【解決手段】半導体装置の製造方法は、基板の上方に絶縁膜を形成する工程と、絶縁膜を貫通する第1の溝及び絶縁膜の内部で終端する第2の溝を絶縁膜に形成する工程と、絶縁膜の内部で終端する配線溝を絶縁膜に形成する工程と、第1の溝の表面及び配線溝の表面に第1の金属膜を形成するともに、第2の溝の上方を覆うように第1の金属膜を形成する工程と、第1の溝及び配線溝に第2の金属膜を埋め込む工程と、を備える。

(もっと読む)

半導体デバイス製造方法

【課題】バリア金属膜とCVD法によって形成される金属導体膜である銅膜との間の密着性に優れた半導体デバイスの製造方法を提供すること。

【解決手段】基板上に直接にまたは絶縁体膜を介してバリア金属膜を形成する工程と、該バリア金属膜上にCVD法によって銅膜を形成する工程とを含む半導体デバイス製造方法において、該バリア金属膜を形成する工程と該銅膜を形成する工程との間に、加熱条件下アンモニア、水素、またはシランのうちの少なくともいずれか1つを含む第1の還元性ガスに暴露する工程と、該銅膜を形成する工程の後に、加熱条件下第2の還元性ガスに暴露する工程と、を有することを特徴とする。

(もっと読む)

耐透明導電膜ピンホール腐食性に優れた薄膜トランジスタ基板

【課題】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、その製造工程において、腐食防止用塗料の塗布や剥離といった工程を設けることなく、ピンホール腐食を防止できるような薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタにおいて透明導電膜と電極配線膜が直接接続する構造を有する薄膜トランジスタ基板であって、前記透明導電膜の結晶最大粒径が200nm以下である薄膜トランジスタ基板。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】半導体領域または導電領域を被覆する絶縁膜に、溝及び該半導体領域または導電領域に達するコンタクトホールの少なくともいずれかを形成し、溝及びコンタクトホールの少なくともいずれかに第一の導電膜を形成し、酸化性ガス及びハロゲン系ガスの混合ガスから生成するプラズマに暴露した後、水を含む雰囲気に暴露して、第一の導電膜の一部または全部を流動化し、その後、第一の導電膜上に第二の導電膜を形成する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作マージンを確保した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のメモリセル及び前記複数のメモリセルを選択する複数の選択配線を有するセルアレイを複数積層してなるセルアレイブロックと、第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうちの所定の第1配線が側面に接続された柱状の第1ビアと、前記第1高さから第2高さまで積層方向に延び、前記セルアレイブロックの選択配線のうち前記第1配線よりも上層の所定の第2配線が側面に接続された柱状の第2ビアとを備え、前記第2配線は、前記第1配線よりも積層方向に厚く、且つ、前記第1配線よりも抵抗率が高いことを特徴とする。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】製造容易性、及び信頼性の高い半導体装置を提供する。

【解決手段】半導体装置100は、接続孔80を有する層間絶縁膜10と、接続孔80上に形成され、上端が接続孔80の上端より低い位置に位置する金属シード膜24と、金属シード膜24上に形成され、接続孔80内を埋め込んでおり、かつ金属シード膜24の上端を覆う金属膜20と、を備える。このためCMPによる平坦化工程において、金属シード膜24、26は露出せず、除去されない

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】機械的強度および密着力に優れた低誘電率の層間絶縁層を有する半導体装置を提供すること。

【解決手段】基板上に形成された、SiO2骨格を含む第1の多孔質層6と、第1の多孔質層6の直上に形成された、SiO2骨格を含む第2の多孔質層7と、第1の多孔質層6に埋め込まれたビア10と、第2の多孔質層7に埋め込まれた配線11と、を有し、第1の多孔質層6の孔密度x1は40%以下であり、第2の多孔質層7の孔密度x2は、(x1+5)%以上である半導体装置を提供する。

(もっと読む)

1,011 - 1,020 / 5,422

[ Back to top ]