国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

131 - 140 / 3,785

半導体記憶装置の製造方法

【課題】スループットの向上を図る。

【解決手段】半導体記憶装置の製造方法は、基板上に、不純物濃度が第1濃度である第1シリコン層35、不純物濃度が第1濃度より低い第2濃度である第1犠牲層、不純物濃度が第1濃度である第2シリコン層35、および不純物濃度が第2濃度である第2犠牲層が順に積層された積層体を形成する工程と、積層体上に、第1絶縁膜を形成する工程と、積層体および第1絶縁膜内に、溝22を形成する工程と、溝内に、不純物濃度が第1濃度より低く、第2濃度より高い第3濃度である第3犠牲層90を埋め込む工程と、ウェットエッチングにより、溝内の第3犠牲層を上面から後退させて除去することで、第1犠牲層および第2犠牲層の端面を後退させる工程と、第1シリコン層および第2シリコン層の端面を第1犠牲層および第2犠牲層の端面に沿ってエッチングする工程とを具備する。

(もっと読む)

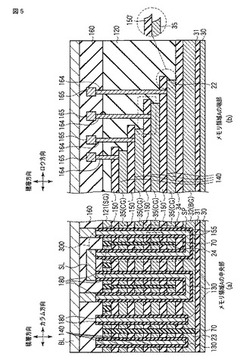

半導体記憶装置

【課題】アドレス信号の配線に起因する配線容量を低減させ、アクセス速度の高速化を実現する半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、複数のビット線と複数のワード線に対応して設けられた複数のメモリセルと、複数のメモリセルのいずれかを特定するためのアドレス信号を中継する中継バッファと、複数のワード線のうち、中継バッファにて中継されたアドレス信号に応じたワード線を選択するトランジスタを複数有するワード線ドライバ回路と、を備え、トランジスタでは、2つの拡散層のうち一方の拡散層が他のトランジスタの拡散層と共有し、拡散層を共有している2つのトランジスタで構成される複数の共有回路が、複数のトランジスタ群に分けられ、複数のトランジスタ群のうち隣り合う前記トランジスタ群の隙間部分に、隣り合うトランジスタ群のいずれかのゲート配線が設けられ、中継バッファはトランジスタ群のゲート配線と接続される。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

OTPメモリ

【課題】より秘匿性の高いOTPメモリを提供する。

【解決手段】メモリセルは、第1ノードと第2ノードとの間に電流経路を形成するメモリトランジスタと、第3ノードと第4ノードとの間に電流経路を形成し、第3ノードがメモリトランジスタのゲートと配線により接続された選択トランジスタと、第1ノードに接続されたキャパシタとを備える。メモリトランジスタに対して、ゲート酸化膜が破壊されず劣化してゲートリーク電流が増大する程度の高電圧を印加することによりデータが書き込まれる。キャパシタの蓄積電荷のリークの有無によりデータを読み出すことが可能となる。ゲート酸化膜の劣化箇所は物理解析で識別できないため、秘匿性が高い。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

鍵格納回路、半導体集積回路、及びシステム

【課題】格納された鍵の値の推測を困難にすることができる、鍵格納回路、半導体集積回路、及びシステムを提供する。

【解決手段】LSI10に搭載された鍵格納ブロック20は、k個のヒューズメモリセル30を有するヒューズブロック22と、鍵生成回路24と、を備えており、ヒューズブロック22からは予め実装されているビット長kの固定出力値fout[k−1:0]が出力される。鍵生成回路24は、レジスタ及び復号器を含んで構成されており、復号器は、演算処理により、固定出力値fout[k−1:0]と、レジスタの出力値と、からビット長n(n>k)の鍵key[n−1:0]を生成して出力する。

(もっと読む)

不揮発性半導体記憶装置

【課題】小型化が可能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、基板と、メモリ部と、非メモリ部と、を備える。メモリ部は、基板上に設けられる。非メモリ部は、基板上に設けられ基板の主面に対して平行な面内でメモリ部と並ぶ。メモリ部は、積層体と、半導体層と、メモリ膜と、導電膜と、を含む。積層体は、主面に対して垂直な第1軸に沿って積層された複数の電極膜と、第1軸に沿って隣り合う2つの電極膜の間に設けられた電極間絶縁膜と、を含む。半導体層は、複数の電極膜の側面に対向する。メモリ膜は、複数の電極膜と半導体層との間に設けられる。導電膜は、積層体の上に設けられ、積層体と離間している。非メモリ部は、導電膜と同層の抵抗素子部を含む。

(もっと読む)

半導体パッケージ

【課題】系統毎の配線長の違いを抑制し、高速動作を実現できる半導体パッケージを提供すること。

【解決手段】第1主面と、第1主面に対向した第2主面とを有する矩形の基板と、第1主面上に実装される第1の半導体チップと、第1の半導体チップ上に積層される1以上の第2の半導体チップと、1以上の第2の半導体チップ上に積層される1以上の第3の半導体チップと、を備え、基板は、第1主面上の第1の辺側に、1以上の第2の半導体チップの電極と接続される第1の接続端子と、第1の接続端子と電気的に接続され、第1の半導体チップの第1の電極と接続される第3の接続端子と、を有し、第1主面上の第1の半導体チップを挟んで第1の辺と対向する第2の辺側に、1以上の第3の半導体チップの第2の電極と接続される第2の接続端子と、第2の接続端子と電気的に接続され、第1の半導体チップの電極と接続される第4の接続端子と、を有する。

(もっと読む)

半導体記憶装置

【課題】書き込み/消去の繰り返しによる信頼性の低下を抑制することが可能な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、ウェル上にトンネル絶縁膜を介して形成された浮遊ゲートに蓄積する電荷量を制御することにより電気的にデータを書き換え可能な複数のメモリセルを備える。半導体記憶装置は、前記ウェル、及び前記浮遊ゲート上に絶縁膜を介して形成された制御ゲートに、電圧を印加する制御回路を備える。

前記メモリセルの消去動作において、前記制御回路は、第1の消去電圧が階段状に上昇する第1のパルス波を、前記ウェルに印加し、その後、第2の消去電圧の第2のパルス波を、前記ウェルに印加する。

(もっと読む)

131 - 140 / 3,785

[ Back to top ]