国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

151 - 160 / 3,785

半導体装置の製造方法

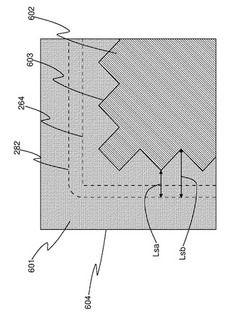

【課題】キャパシタ上の絶縁膜とキャパシタの形成されていない領域上の絶縁膜と平坦化する際に、キャパシタ上の絶縁膜を一部エッチング除去した後平坦化すると、両者の境界部に残る絶縁膜隆起部が剥がれてくぼみ等の欠陥が発生するのを抑制する。

【解決手段】境界部に残す絶縁膜の隆起部立ち上がり点から水平方向の最短距離をLr、エッチング量をHdとしたとき、アスペクト比Hd/Lrを0.6以下、好ましくは0.25以下する。キャパシタ上のエッチング開口端形状として鋸刃型などの形状、開口端側面を傾斜形状とする、又はスリットを形成する。

(もっと読む)

バッファ付きフィンFETデバイス

【課題】フィンFETデバイスのロバストネスを向上させる。

【解決手段】トランジスタデバイスであって、半導体基板と、半導体基板に形成されたバッファ付き垂直フィン状構造であって、垂直フィン状構造は、ドレーン領域とソース領域512との間にチャンネル領域514を含む上位の半導体層と、上位の半導体層の下のバッファ領域304であって、第1のドーピング極性を有するバッファ領域と、第1のドーピング極性と反対である第2のドーピング極性を有するウェル領域302の少なくとも一部分と、バッファ領域とウェル領域との間の少なくとも1つのp−n接合であって、該垂直フィン状構造の水平断面を少なくとも部分的にカバーする少なくとも1つのp−n接合とを含むバッファ付き垂直フィン状構造と、上位の半導体層のチャンネル領域をおおい形成されたゲートスタックとを備えている。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートトランジスタや周辺回路部のトランジスタの下部電極の抵抗値を低減し、しきい値電圧の増加も図れるようにする。

【解決手段】ゲート電極の加工時に、選択ゲートトランジスタのゲート電極SGD−SGD間の側壁部と、周辺回路部のトランジスタのゲート電極PGの両側壁とに、多結晶シリコン膜4の上部に段差形状を形成し、傾斜部4dを設ける。ゲート電極の多結晶シリコン膜6のシリサイド加工時に、多結晶シリコン膜4の傾斜部4dからもシリサイド化を進行させ、シリサイド膜7および7aを形成する。これにより、ゲート電極SGDおよびPGの下部電極においても低抵抗化を図ることができる。多結晶シリコン膜4に分断層4aを設けることで、シリサイド反応を停止させたり、設けないでゲート絶縁膜3の部分までシリサイド反応させてしきい値電圧を増加させたりできる。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

不揮発性メモリ要素及びこれを含むメモリ素子

【課題】不揮発性メモリ要素及びこれを含むメモリ素子を提供する。

【解決手段】両電極の間にメモリ層を含み、該メモリ層は複数層構造を持つ不揮発性メモリ要素である。メモリ層は、ベース層及びイオン種交換層を含み、これらの間のイオン種の移動による抵抗変化特性を持つ。イオン種交換層は、少なくとも2つの層を含む複数層構造を持つ。不揮発性メモリ要素は、複数層構造のイオン種交換層によりマルチビットメモリ特性を持つ。ベース層は酸素供給層であり、イオン種交換層は酸素交換層である。

(もっと読む)

半導体記憶装置、及び半導体記憶装置の動作方法

【課題】光学的に書き込み状態が解析されることがなく、安価に実現することのできる、半導体記憶装置及びその動作方法を提供すること。

【解決手段】半導体記憶装置は、書込み処理が行われていない第1半導体記憶素子と、書込み処理が行われた第2半導体記憶素子とを具備する。前記第1半導体記憶素子及び前記第2半導体記憶素子は、それぞれ、不純物が注入された半導体層を備える抵抗部と、前記抵抗部に接続される、第1コンタクトと、前記抵抗部に接続される、第2コンタクトとを具備する。前記第1半導体記憶素子における前記半導体層の不純物の活性化率は、前記第2半導体記憶素子のそれとは異なっている。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

半導体記憶装置、および、ビット線の充電方法

【課題】低消費電力モードから通常動作モードへの復帰時におけるビット線の充電時間を適切に設定することで、復帰動作で消費される電力を低減する。

【解決手段】半導体記憶装置10は、複数のビット線2a,2b…のそれぞれを充電する充電回路4と、帰還経路5aの配線にダミービット線3が用いられているリングオシレータ5と、リングオシレータ5の発振回数が、複数のビット線2a,2b…の数に基づいて設定された所定の回数に達すると、検出信号を出力するカウンタ6と、低消費電力モードから通常動作モードへの復帰を指示する復帰信号に応じて、充電回路4による複数のビット線2a,2b…の充電を開始させるとともにリングオシレータ5の発振を開始させ、カウンタ6から出力された検出信号に応じて、充電回路4による複数のビット線2a,2b…の充電を終了させる制御回路7と、を有する。

(もっと読む)

情報格納装置

【課題】より容易な方法で集積度を向上させた情報格納装置を提供する。

【解決手段】本発明の情報格納装置は、基板と、基板上のゲートライン構造体を含むトランジスターと、少なくとも一部が基板内に埋め込まれてトランジスターの活性領域を定義する導電性分離パターン(conductive isolation patterns)と、を有し、導電性分離パターンは、互いに電気的に連結される。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】チップ面積の縮小を図る。

【解決手段】磁気ランダムアクセスメモリは、メモリセル部の素子領域10a上に形成された第1の拡散層17aと、第1の拡散層に接続された第1のコンタクトCB1と、第1のコンタクト上に形成された第1の下部電極層21aと、第1の下部電極層上に形成された第1の抵抗変化層22a及び第1の上部電極層23aと、周辺回路部において互いに異なる素子領域に形成された第2乃至第4の拡散層17d、17eと、第2乃至第4の拡散層に接続された第2乃至第4のコンタクトCS1、CS2と、第1の下部電極層、第1の抵抗変化層、第1の上部電極層と同じ高さに形成された第2の下部電極層21b、第2の抵抗変化層22b、第2の上部電極層23bとを具備する。第2の下部電極層は、第2及び第3のコンタクトを接続する第1のローカル配線L1として機能する。

(もっと読む)

151 - 160 / 3,785

[ Back to top ]