国際特許分類[H03B5/02]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 細部 (241)

国際特許分類[H03B5/02]の下位に属する分類

国際特許分類[H03B5/02]に分類される特許

21 - 30 / 122

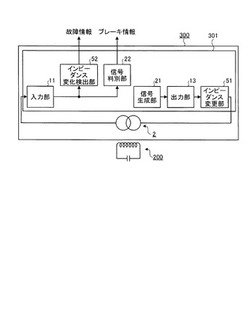

自動列車停止装置の車上用装置

【課題】通常の運行動作に影響を与えずに、地上子との結合で変化する車上子のインピーダンス変化を検知して車上子と地上子の結合を検知して地上子から信号現示情報を得る信号現示情報取得の健全性を監視して安全性を確保することができる自動列車停止装置の車上用装置を得る。

【解決手段】車上子2と検知部301とにより構成されるインピーダンス変化検知回路を有し、検知部301が、インピーダンス変化検知回路のインピーダンスを変更するインピーダンス変更部51と、インピーダンス変更部51によりインピーダンス変化検知回路のインピーダンスを変更したことにより生じる複数の周波数の信号の特性の予め設定された変化を検出してインピーダンスの変化を検出した場合に、信号現示情報の取得動作が健全であると判断するインピーダンス変化検出部52と、を備える。

(もっと読む)

水晶発振器

【課題】水晶発振器の出力振幅の調整機能を簡易な構成で実現する。

【解決手段】水晶発振器は、電源に接続される電源端子(VCC)と、接地電位に維持される接地端子(GND)と、電源端子と接地端子とに接続され、電源端子と接地端子との間に印加された電源電圧に基づく振幅レベルの発振信号(V0)を出力する水晶発振回路(6)と、イネーブル信号(VEN1、VEN2)が入力されるイネーブル端子(EN1、EN2)と、イネーブル端子と接地端子とに接続され、水晶発振回路から入力される発振信号を波形整形してイネーブル端子と接地端子との間のイネーブル信号の電圧に応じた振幅レベルの基準クロック信号(CLK1、CLK2)を出力するバッファ回路(2a、2b)と、バッファ回路から出力される基準クロック信号が出力される出力端子(OUT1、OUT2)と、を備える。

(もっと読む)

発振回路

【課題】従来の発振回路では、出力信号のジッタを抑制できない問題があった。

【解決手段】本発明の発振回路は、発振周波数設定電流に基づき蓄積された電荷量に応じて発振周波数制御電圧Vcpを生成するフィルタコンデンサCpumpと、発振周波数制御電圧Vcpに応じて出力する発振信号Foutの周波数を変動させる発振器30と、発振信号Foutの周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する制御回路40と、タイミング制御信号に基づき発振信号Foutの周期の長さに応じて連続的に電圧レベルが変化する周波数検出電圧Vcapを生成する周波数検出回路10と、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて発振周波数設定電流を連続的に可変してフィルタコンデンサCpumpに出力する差動増幅器20と、を有する。

(もっと読む)

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

2出力直交ローカル信号発振器

【課題】90°の位相差を持つ2つのローカル信号を発生するローカル信号源として使用可能な2出力直交ローカル信号発振器の提供。

【解決手段】第1及び第2のトランジスター14及び15を有し、共振器20を共有することにより、基本発振周波数にてプッシュ−プッシュ発振動作を行い、第1及び第2のトランジスターの一方から第1のローカル信号を出力する第1のプッシュ−プッシュ型発振器18と、第3及び第4のトランジスター16及び17を有し、共振器20を共有することにより、前記基本発振周波数にてプッシュ−プッシュ発振動作を行い、第3及び前記第4のトランジスターの一方から第2のローカル信号を出力する第2のプッシュ−プッシュ型発振器19とを有し、第1及び第2のプッシュ−プッシュ型発振器は、共振器の直交共振モードによって直交発振動作を行い、90°の位相差のある直交ローカル信号を出力することを特徴とする2出力直交ローカル信号発振器。

(もっと読む)

広帯域発振回路

【課題】LC型VCOの出力する発振信号の周波数帯域が比較的狭くても、連続した周波数の発振信号(分周信号)の出力が可能な広帯域発振回路の実現。

【解決手段】発振信号を出力する発振器11と、発振器の出力する発振信号を受け、フィルタリングして注入同期信号NINJを出力するフィルタ14と、自己発振動作を行い、注入同期信号により発振動作が規制されて発振信号の分周信号を出力し、制御信号VbDに応じて分周比が変化する注入同期型周波数分周器12と、を備え、フィルタ14は、分周信号に同期したフィルタ制御信号に応じて、発振信号を通過させる通過特性を時間的に制御して注入同期信号NINJを発生する。

(もっと読む)

発振器複合回路と半導体装置並びに電流再利用方法

【課題】発振器の不安定動作を回避し低消費電力化を実現する発振器複合装置と方法の提供。

【解決手段】インダクタ(111)と容量(112)を含む共振回路(110)を備えた発振器(100)と、前記発振器の発振出力信号を入力し、且つ、電源側からの電流パスを構成し前記電流パスの前記第1の電源と反対側の一端が前記発振器の前記インダクタ(111)の中点に接続された差動対を含む分周器(200)とを、グランドと電源間に縦積みに配置し、分周器(200)の直流供給電流端子(230)からグランド側に流れる直流電源電流を、発振器(100)の電源電流として再利用する。

(もっと読む)

周波数逓倍回路

【課題】入力振幅の大きさに依存することなく適切な発振振幅を得ることができる、消費電流が少なく、かつ簡略化された周波数逓倍回路を提供する。

【解決手段】CMOSインバータのPMOSFET21、NMOSFET22の少なくともどちらか一方に流れる発振電流を個々に制御する電流制御用素子23、24と、発振電流の交流成分のみを通過させる容量10、11と、容量10、11を通過した交流信号を加算処理して逓倍信号を出力する加算手段とから成り、加算手段は、電流制御用素子23、24とともに基準電圧によりオフセットされているため、CMOSインバータの各FETに流れる電流を任意に制限することができ、入力振幅の大きさに依存しない適切な発振振幅を得られる。

(もっと読む)

低位相ノイズ電圧制御発振器

本発明の形態は、消費電力を低減し位相ノイズ性能を向上させるために、電流再使用技術を用いた低位相ノイズ発振器回路を含み、発振器回路は、第2のVCOに結合されている第1のVCOを備え、第1及び第2のVCOの出力は、コンデンサ等の受動素子に結合されている。第1及び第2のVCO両方の全体の消費電力は、単一のVCOの消費電力と略同じである。また、位相ノイズは、約3dBほど低減される。このため、発振器回路の消費電力を増加させることなしに、位相ノイズ性能が向上される。 (もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

21 - 30 / 122

[ Back to top ]