国際特許分類[H03B5/02]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 振動の発生,直接のまたは周波数変換による振動の発生,スイッチング動作を行なわない能動素子を用いた回路による振動の発生;このような回路による雑音の発生 (3,506) | 出力から入力への再生帰還による増幅器を用いた振動の発生 (3,166) | 細部 (241)

国際特許分類[H03B5/02]の下位に属する分類

国際特許分類[H03B5/02]に分類される特許

31 - 40 / 122

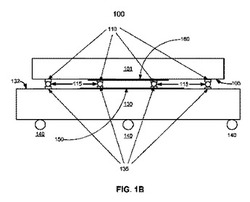

周波数発生のための装置及び方法

広帯域周波数発生器は、フリップチップパッケージ内の同一のダイに配置された異なる周波数帯域のための2つ以上の発振器を有する。2つの発振器の誘導子間の結合は、一方の誘導子がダイに配置され、他方の誘導子がパッケージに配置され、これら誘導子がハンダバンプの直径によって離されることで、減少させられる。弱結合されたこれら誘導子では、一方の発振器の帯域を増加させるために他方の発振器のLCタンク回路の操作をしたり、その逆を行ったりできる。一方の発振器の振動の好ましくないモードを防ぐことは、他方の発振器の粗同調バンクの全容量といった大容量を他方の発振器のLCタンク回路に与えることによって達成され得る。好ましくないモードを防ぐことは、他方の発振器のLCタンクのQファクタを減少させ、タンク回路内の損失を増加させることによっても達成され得る。 (もっと読む)

温特補正機能付き発振回路およびその製造方法

【課題】 発振周波数を補正するためのメモリなどが不要な温特補正機能付き発振回路およびその製造方法を実現する。

【解決手段】 温特補正機能付き発振回路10は、第1の発振回路21と、第2の発振回路22と、第1の発振回路21が発生する発振周波数を理想の発振周波数に近い発振周波数に補正するための補正回路50とを備える。補正回路50は、第1の発振回路21の発振周波数f1と、第2の発振回路22の発振周波数f2との差分(f1−f2)を検出し、その検出した差分に補正係数αを乗じ(α・(f1−f2))、その補正された差分を第1の発振回路21の発振周波数に加算し(f1+α・(f1−f2))、それを出力する動作を行う。

(もっと読む)

発振回路

【課題】半導体集積回路の電源電圧や温度の変動がある場合においても、発振波形の周波数変動を低減させる。

【解決手段】リミッタLm1は、出力端子T1の発振信号Vo1の電圧と、基準電圧Vconstに電圧降下Vth分を加算した値とを比較し、出力端子T1の発振信号Vo1の電圧が、基準電圧Vconstに電圧降下Vth分を加算した値を超えた場合、出力端子T1の発振信号Vo1の振幅を、基準電圧Vconstに電圧降下Vth分を加算した値に制限する。

(もっと読む)

発振器

【課題】負荷容量に応じて最適な波形を出力可能な発振器を提供する。

【解決手段】発振回路12からの出力を、出力バッファ(前段出力バッファ14、出力バッファ22)を介して負荷回路に出力する発振器10であって、発振器10は、出力バッファ22の駆動能力を出力バッファから流れる電流に応じて調整可能なバッファ制御回路48を有する。ここで出力バッファ22は、発振回路12の後段に複数並列に接続されるとともに、バッファ制御回路48は、出力バッファから流れる電流に応じて出力バッファ22の稼動数を調整する信号を出力バッファ22に出力することにより出力バッファ22の駆動能力を調整している。

(もっと読む)

発振制御回路

【課題】発振開始時からデューティが50%に安定する発振制御回路を提供する。

【解決手段】作動制御回路3が、発振信号の発振電位がCMOSインバータIV1の反転電位よりも低い第1基準電位よりも低くなるまでMOSトランジスタT11及びT12をオフ状態、MOSトランジスタT2をオン状態に保持する。作動制御回路3が、発振信号の発振電位が第1基準電位よりも低くなったとき出力が反転するCMOSインバータIV31と、CMOSインバータ31の後段に設けた抵抗R31とコンデンサC31とからなるローパスフィルタ31と、ローパスフィルタ31の出力が閾値を越えると出力が反転するCMOSインバータ33と、を有している。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

発振器

【課題】温度変動に対して一定の出力電圧振幅を確保するとともに、消費電力を低く抑えた低消費電力な発振器を提供する。

【解決手段】圧電振動子10と、圧電振動子10を発振させ発振信号22を出力する発振回路20と、発振信号aを入力するバッファー回路30と、バッファー回路30の出力信号bを出力するNchトランジスターN1とPchトランジスターP1とを含むプッシュプル型出力回路40と、NchトランジスターN1のゲート端子に接続されたNchカレントミラー回路50と、PchトランジスターP1のゲート端子に接続されたPchカレントミラー回路60とを含み、第1のカレントミラー回路がNchトランジスターN1の温度特性を補償し、第2のカレントミラー回路がPchトランジスターP1の温度特性を補償することによって、プッシュプル型出力回路40が持つ温度特性をキャンセルさせ、温度変動によらずほぼ一定の電圧振幅を出力する。

(もっと読む)

集積電圧制御発振器回路

改善した位相ノイズ性能と、より低い電力消費とを有する電圧制御発振器を提供する技術である。例示的な実施形態では、電圧制御発振器(VCO)は、混合器に、または、2分周器のような周波数分周器に結合されている。VCOは、磁気的にクロス結合されているインダクタを有するトランジスタ対と、トランジスタ対のゲートに結合されている可変キャパシタンスとを備える。例示的な実施形態では、周波数分周器は、トランジスタ対を通って流れる差動電流の周波数を分周して、LO出力を発生させるように構成されている。代替的で例示的な実施形態では、混合器は、トランジスタ対を通って流れる差動電流を別の信号と混合するように構成されている。VCOと、混合器または周波数分周器は、通常バイアス電流を共有し、したがって、電力消費を減少させる。これらの技術を利用するさまざまな例示的な装置および方法を開示する。 (もっと読む)

電子回路

【課題】電子回路(例えば、マイクロコンピュータ)の動作モードに応じて、低周波数の発振器について適切な電源インピーダンスを設定することにより、前記発振器の誤動作を防止しながら、消費電力を適切に低減することができる。

【解決手段】システムクロックのクロック源として、高速発振器11、中速発振器12、低速発振器13が設けられる。また、時計用クロックを発生する水晶発振器30が設けられる。そして、高速発振器11が動作している時は、水晶発振器30の電源インピーダンスを低くして、耐ノイズ性を高める。一方、高速発振器11、中速発振器12、低速発振器13がすべて停止している待機時には、水晶発振器30の電源インピーダンスを高くして消費電力を抑える。

(もっと読む)

発振回路

【課題】振動子の安定発振を早める発振回路に関する技術を提供するとともに、それを用いた超音波流量計を提供する。

【解決手段】共振周波数を有する振動子1と、前記振動子に接続されるアンプ2と、付勢パルス発生手段3と、前記付勢パルス発生手段3と前記振動子1およびアンプ2との接続・非接続とを切替える切替え手段4とを備え、前記振動子1の駆動初期は前記切替え手段4により、前記振動子1と前記付勢パルス発生手段3とを接続するようにした発振回路。

(もっと読む)

31 - 40 / 122

[ Back to top ]