国際特許分類[H05K1/02]の内容

電気 (1,674,590) | 他に分類されない電気技術 (122,472) | 印刷回路;電気装置の箱体または構造的細部,電気部品の組立体の製造 (64,965) | 印刷回路 (15,851) | 細部 (13,335)

国際特許分類[H05K1/02]の下位に属する分類

基体用材料の使用 (3,156)

金属パターンのための材料の使用 (1,329)

印刷回路への,または印刷回路間の電気的接続のための印刷要素 (1,520)

2つ以上の印刷回路の構造的結合 (1,850)

国際特許分類[H05K1/02]に分類される特許

21 - 30 / 5,480

回路基板の補強位置決定方法及び基板組立体

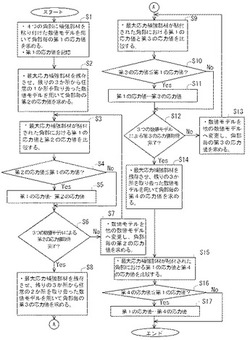

【課題】電子部品の周辺にスタッドが配置された回路基板において、必要最小限の反り低減対策を容易に決定することを目的とする。

【解決手段】回路基板の補強位置決定方法は、表面に、電子部品が複数のバンプにより実装され、裏面に、前記電子部品の角部に配置されたバンプに対応する位置に補強部材が貼り付けられた回路基板の数値モデルを設定する。そして、前記数値モデルに、前記電子部品の周囲に配置され且つ前記回路基板を電子機器の筐体に固定するスタッドに関する情報を取り込み、前記回路基板の裏側から前記電子部品に向かって力を加えたときに、前記角部のバンプにそれぞれ発生する応力値を求めるシミュレーションを行う。前記シミュレーションにより求めた前記応力値に基づいて、前記スタッドの位置に対応する前記補強部材の配置を決定する。

(もっと読む)

電子制御装置

【課題】電子制御装置において、部品点数の増加を抑えつつ小電流が流れる配線パターンにノイズが入り込むことを抑制する。

【解決手段】プリント配線板の厚み方向から見て、大電流用内層パターンが形成される大電流領域R1と、電流用内層パターンが形成される小電流領域R2とが重ならずに配置されている。

(もっと読む)

基板取り付け装置、基板取り付け方法及び電子機器

【課題】電子機器の筐体に多層基板を容易かつ安価に取り付けて、電磁バンドギャップ構造体を設ける。

【解決手段】多層基板100は、多層基板100の下面に形成された接地導体1と、配線導体5と、多層基板100の下面の各位置であって配線導体5に対向する各位置に所定の間隔d1で形成された複数のパッチ導体6とを備える。基板取り付け装置50は、パッチ導体6と、各パッチ導体6を電子機器200の筐体10にそれぞれ電気的に接続する複数の導電性の足部30を備える。

(もっと読む)

配線回路基板およびその製造方法

【課題】信号線路対の占有面積の増加を抑制しつつ信号線路対のインピーダンスの低減および信号のスキューの低減を可能とする配線回路基板およびその製造方法を提供する。

【解決手段】カバー絶縁層42aがベース絶縁層41上に形成される。書込用配線パターンW1は線路LA1〜LA3を含み、書込用配線パターンW2は線路LB1〜LB3を含む。書込用配線パターンW1,W2は信号線路対を構成し、線路LA2,LB2はカバー絶縁層42aの上面に配置され、線路LA3,LB3はベース絶縁層41の上面に配置される。線路LA2,LB2の少なくとも一部はカバー絶縁層42aを介してそれぞれ線路LB3,LA3に対向する。線路LA2,LA3は線路LA1と電気的に接続され、線路LB2,LB3は線路LB1と電気的に接続される。線路LB1はベース絶縁層41の下面のジャンパー配線を通して線路LB2,LB3の少なくとも一方と電気的に接続される。

(もっと読む)

電子素子及び/又は電気素子のための回路装置

【課題】従来技術の欠点が改善された回路装置を提供すること。

【解決手段】少なくとも1つの電子素子及び/又は電気素子(30,30’)と、支持体(10,10’)とを有する回路装置であって、

前記少なくとも1つの電子素子及び/又は電気素子は、該電子素子及び/又は電気素子と前記支持体との間に空気層(LS,LS’)を形成しつつ、少なくとも1つのはんだ層(40,40’)を介して前記支持体と導電的に接続されている、

回路装置において、

前記支持体の中に少なくとも1つの3次元収容構造(20,20’)が組み込まれており、

前記3次元収容構造内にて、該3次元収容構造の少なくとも2つのコンタクト領域(22,22’)の間に、前記少なくとも1つの電子素子及び/又は電気素子が軸方向に配置されている、

ことを特徴とする回路装置。

(もっと読む)

基板内蔵用電子部品および部品内蔵型基板

【課題】 厚みを薄くできるとともに部品集積度の向上も図ることができる基板内蔵用電子部品および部品内蔵型基板を提供する。

【解決手段】 基板内蔵用電子部品(100)は、一対の磁性体層(101、102)と、前記一対の磁性体層(101、102)の間に挟み込まれた複数の層からなる絶縁体層(103〜105)と、前記絶縁体層の少なくとも一の層内に形成された平面型コイル(110、111)と、前記平面型コイル(110、111)の周囲を一巡して同層内に形成されたシールドパターン(121、122)とを有する。

(もっと読む)

多数個取りセラミック基板およびセラミック基板

【課題】 絶縁層が光の反射層となることができ、個片のセラミック基板への分割も容易な多数個取りセラミック基板および個片のセラミック基板を提供することにある。

【解決手段】 複数の基板領域2を有する母基板1と、母基板1の上面に、基板領域2の境界に沿って設けられた分割溝3とを備えており、母基板1が、第1のセラミック焼結体からなる絶縁層1aと、第1のセラミック焼結体よりも結晶化温度が低い第2のセラミック焼結体からなる拘束層1bとが交互に、最上層が絶縁層1aとなるように積層されて形成されているとともに、母基板1の上面に分割溝3に沿って、第2のセラミック焼結体からなる帯状拘束層4が付着している多数個取りセラミック基板9である。帯状拘束層4により、分割溝3が形成された部分における絶縁層1aの収縮を抑制して分割溝3の変形を抑制できる。そのため、分割が容易な多数個取りセラミック基板9を提供できる。

(もっと読む)

多層配線基板、AV機器およびテレビジョン受像機

【課題】より確実に静電気から保護されている安価な多層配線基板を提供すること。

【解決手段】本発明の多層配線基板は、スルーホール、導電体層、半田材料の凸部および半田材料の被覆部を用いて静電気対策がなされている。

(もっと読む)

通信妨害電磁波測定装置、通信妨害電磁波測定用素子、及び表示装置通信妨害電磁波測定装置

【課題】電子機器が発する電磁波の無線通信品質への影響をより正確に計測する。

【解決手段】通信妨害電磁波測定装置は、無線通信プロトコルによる通信信号が印加される第1アンテナ線(102)と、前記無線通信プロトコルにより第1アンテナ線と送受信を行なう第2アンテナ線(103)と、第1アンテナ線と第2アンテナ線とがそれぞれ接続される測定素子(200)と、第2アンテナ線に接続され、通信品質の測定を行なう通信品質測定装置(101)と、を備え、測定素子は、基板と、前記第1アンテナ線が電気的に接続される、前記基板上の配線である第1配線と、前記第2アンテナ線が電気的に接続される、前記基板上の配線である第2配線と、を有する。

(もっと読む)

電子部品実装モジュールの製造方法および電子部品実装モジュール

【課題】配線パターンの配置自由度を制限することなく、はんだブローホールの発生を防止可能であるとともに、はんだによるショートを防止する。

【解決手段】一実施形態に係る凹部を有する電解コンデンサ1がはんだ付けされた電子部品実装モジュールの製造方法は、電解コンデンサ1のリード線1aを挿通孔11に挿通し、電解コンデンサ1をプリント配線板10の実装領域Aに搭載する工程と、プリント配線板10を治具板20に固定し、挿通孔11を治具板20の開口部22に露出させるとともに、実装領域A内側の貫通孔12および実装領域A外側の貫通孔13が、治具板20の流路部23と連通することにより凹部1bをプリント配線板10の上側の空間と連通させる工程と、プリント配線板10が固定された治具板20を、開口部22に露出したプリント配線板10の裏面が溶融はんだと接触するように溶融はんだ槽に浸漬する工程と、を備える。

(もっと読む)

21 - 30 / 5,480

[ Back to top ]