富士通セミコンダクター株式会社により出願された特許

41 - 50 / 2,507

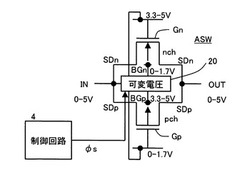

半導体装置及びアナログスイッチの制御方法

【課題】高い電圧を有する入力信号に対して適切に動作するアナログスイッチを有する半導体装置を提供する。

【解決手段】入力端子と出力端子との間にPチャネルトランジスタとNチャネルトランジスタとを並列に接続したアナログスイッチと,入力端子に印加される入力電圧に応じて,Pチャネルトランジスタの第1ゲート電圧及び第1バックゲート電圧と,Nチャネルトランジスタの第2ゲート電圧及び第2バックゲート電圧とのそれぞれの電位を可変生成する可変電圧回路と,アナログスイッチを導通または非導通に制御する制御信号を可変電圧回路に供給する制御回路とを有する。可変電圧回路は,導通に制御する制御信号に応答して,可変生成される第1ゲート電圧と第2ゲート電圧とをPチャネルトランジスタとNチャネルトランジスタのゲートにそれぞれ出力する。

(もっと読む)

画像生成装置,画像生成プログラム,および,画像生成装置を有する画像表示システム

【課題】半透明なオブジェクトの後ろに不透明なオブジェクトが配置されている場合,半透明なオブジェクトと不透明なオブジェクトとが重なる領域を適切にぼかす。

【解決手段】画像生成部111は,3次元仮想空間において,半透明なオブジェクトが,不透明なオブジェクトよりも所定の視点位置側に配置され,かつ,2次元表示用画像において半透明なオブジェクトと不透明なオブジェクトが重なる場合,半透明なオブジェクトの透明度に応じて,この重なる領域のぼけ度を,不透明なオブジェクトのぼけ度の割合で補正する。

(もっと読む)

半導体装置の製造装置

【課題】半導体装置や電子機器の更なる微細化・高集積化の要請に応えるべく、隣接するバンプ間距離を短縮するも、当該バンプ間に短絡を生ぜしめることなく良好な所期のバンプリフローを実現し、信頼性の高い製品を実現する。

【解決手段】チャンバ1内の上部に設けられた、第1の加熱温度を制御する第1の加熱制御機構3と、チャンバ1内の下部に設けられた、第1の加熱制御機構3と独立して第2の加熱温度を制御する第2の加熱制御機構4と、第1の加熱制御機構3を上下方向に移動させる第1の移動機構5と、第2の加熱制御機構4を、第1の移動機構5とは独立して上下方向に移動させる第2の移動機構6とを含む。

(もっと読む)

半導体装置

【課題】低電圧動作が可能なSRAMをそのセル面積の増加を抑えて実現する。

【解決手段】第1方向Sに並ぶP型ウェル領域20、N型ウェル領域30、P型ウェル領域40に、第2方向Tに隣接するメモリセル1aが形成される。各メモリセル1aは、P型ウェル領域20,40に形成されたトランスファトランジスタTf1,Tf2及びドライバトランジスタDr1,Dr2、N型ウェル領域30形成されたロードトランジスタLo1,Lo2を備える。SRAM1では、第2方向Tに隣接するメモリセル1aの、互いのトランスファトランジスタTf1のゲート電極がワード線WL1に、互いのトランスファトランジスタTf2のゲート電極がワード線WL2に、それぞれ電気的に接続される。ワード線WL1はP型ウェル領域20に、ワード線WL2はP型ウェル領域40に、それぞれ電気的に接続される。

(もっと読む)

半導体装置及び半導体装置の形成方法

【課題】配線層間に絶縁物が堆積しない配線の形成方法を提供する。

【解決手段】半導体装置10は、第1絶縁体層14と、第1絶縁体層14上に間隔を空けて配置された複数の配線層18a、18bと、配線層18a、18bの側面上に形成された水素を吸蔵及び放出する水素吸蔵層19b、19c、19d、19eと、複数の配線層18a、18b上に、配線層間の溝20b上を跨ぐように形成された第2絶縁体層23と、を備えた配線を備える。

(もっと読む)

半導体装置

【課題】電源線と機能回路の間に電源スイッチとして接続されるMOSトランジスタのオン時のバックゲートの電圧を簡単な構造で調整することができる半導体装置を提供する。

【解決手段】一対の電源線2、3と、機能回路4a0〜4anと、一対の電源線2、3との少なくとも一方と機能回路4a0〜4anの間に接続されるスイッチング回路6a0〜6an、7a0〜7anとを有し、スイッチング回路6a0〜6an、7a0〜7anは、ソース/ドレインの一方が機能回路4a0〜4anに接続され、他方が前記一対の電源線2、3の一方に接続される第1のMOSトランジス11と、第1のMOSトランジスタ11のゲートとバックゲートを接続する抵抗素子12、21と、第1のMOSトランジスタ11のゲートに接続されるゲート電圧制御回路13と、を有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】基準チップ特定に用いる目印を半導体ウエハに形成する半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、フォトレジスト膜の形成された半導体ウエハに、露光用マスクを介して第1、第2、第3露光を行う工程を有し、第1露光の第1ショット領域に対し、第2露光の第2ショット領域は第1方向に隣接し、第2ショット領域に対し第3露光の第3ショット領域は第1方向に隣接し、ショット領域は第1方向に交差し対向する第1、第2の辺と、第1方向に平行な第3、第4の辺を有する外周スクライブ領域を有し、第1の辺上に第1パターンが、第2の辺上で第1パターンと対向する位置に第1パターンを内包する透光領域の第2パターンが配置され、第1、第2露光は第1、第2パターンが重ならないように、第2、第3の露光は第1、第2パターンが重なるように行われる。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

半導体集積回路

【課題】 複数のバッファに供給される信号が同時に同じレベルに変化するときに発生する電源ノイズを低減する。

【解決手段】 半導体集積回路は、動作モードに応じて信号を互いに同期してまたは非同期に出力する複数の第1バッファと、複数の第1バッファから出力される信号をそれぞれ受け、伝搬遅延時間が互いに異なる複数の第2バッファとを有している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】新規な構造のコンタクトプラグを有する半導体装置を提供する。

【解決手段】

半導体装置は、半導体基板と、半導体基板に形成され、ソース/ドレイン領域及びゲート電極を有するトランジスタと、トランジスタのソース/ドレイン領域及びゲート電極を覆う絶縁膜と、絶縁膜中に形成され、トランジスタのソース/ドレイン領域またはゲート電極に接されるコンタクトプラグとを有し、コンタクトプラグは、絶縁膜の厚さ方向に延在しトランジスタのソース/ドレイン領域またはゲート電極に接触する柱部と、柱部の上部から絶縁膜の表面と平行な方向に張り出し上面が平坦化された鍔部とを有する。

(もっと読む)

41 - 50 / 2,507

[ Back to top ]