株式会社ルネサステクノロジにより出願された特許

51 - 60 / 4,790

シングルチップデータプロセッサ及び半導体集積回路

【課題】接続している別のデータプロセッサから、当該データプロセッサの内部機能若しくは当該データプロセッサの外付け回路を効率良く利用する方法を提供する。

【解決手段】一のデータプロセッサ101に他のデータプロセッサ100との接続を可能にするためのインタフェース手段119を設け、このインタフェース手段に、一のデータプロセッサ内の内部バス108に他のデータプロセッサをバスマスタとして接続可能にする機能を設け、内部バスにメモリマップされた周辺機能を前記インタフェース手段を介して外部より当該他のデータプロセッサが直接操作できるようにする。これにより、データプロセッサは、実行中のプログラムを中断することなく、別のデータプロセッサの周辺機能等を使うことが可能となる。要するに、一のデータプロセッサは別のデータプロセッサの周辺リソースを共有することが可能になる。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の半導体チップを多数積層した半導体装置において、生産性を損なうことなく高性能化する。

【解決手段】シリコン基板1の主面s1上に順に形成された複数の素子、層間絶縁膜2およびパッド3と、パッド3に電気的に接続するバンプ電極4と、シリコン基板1の裏面s2に形成され、バンプ電極4に電気的に接続する裏面電極6とを有する半導体装置である。バンプ電極4は、パッド3を貫通し、シリコン基板1側に向かって突出するような突出部d1を有する。また、裏面電極6は、シリコン基板1の裏面s2側から主面s1側に向かって、バンプ電極4の突出部d1に達し、パッド3には達しないような裏面電極用孔部7の内側を覆うようにして形成されていることで、バンプ電極4と電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】積層された半導体チップの上段側が傾き、ワイヤの接合不良が発生することや、上段側の半導体チップの下面と樹脂表面との間に隙間が発生し、パッケージがクラックすることを防止できる半導体装置を提供する。

【解決手段】配線基板2上にマイコンチップ1がフリップチップ接合され、マイコンチップ1上にマイコンチップ1より外形寸法が大きなメモリチップ7が積層されるSIP11において、配線基板2上のマイコンチップ1の周囲にダム2fが形成され、マイコンチップ1とダム2fとの間に第1封止体4が配置され、メモリチップ7の迫り出し部7dが第1封止体4により支持され、接着層を有するDAF6を介してマイコンチップ1上に搭載され、第1封止体4の表面に形成された凹凸がDAF6の前記接着層に吸収されるため、上段側のメモリチップ7が下段側のマイコンチップ1に対して傾いて配置されることを防止し、SIP11の信頼性を向上できる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置における信頼性の向上を図る。

【解決手段】下段側の第1半導体パッケージ7上に上段側の第2半導体パッケージが積層されて成るPOP型半導体装置において、第1半導体パッケージ7の第1配線基板2の複数の主面側ランド2eを、主面2aの中央部に位置するチップ搭載領域を境にその両側に振り分けて配置しているため、スルーモールド方式を採用することができる。これにより、下段側の第1半導体パッケージ7の第1配線基板2の主面2a上に形成された第1封止体4が、第1配線基板2の一方の第2辺2nの中央部から他方の第2辺2nの中央部に向かって形成されるため、下段側の第1配線基板2の反りに対する強度を高めることができ、前記POP型半導体装置の信頼性の向上を図れる。

(もっと読む)

半導体装置

【課題】非絶縁型DC−DCコンバータの小型化及び電圧変換効率を向上させる。

【解決手段】ハイサイドスイッチ用のパワーMOS・FETとローサイドスイッチ用のパワーMOS・FETとが直列に接続された回路を有する非絶縁型DC−DCコンバータにおいて、ハイサイドスイッチ用のパワートランジスタとローサイドスイッチ用のパワートランジスタと、これらを駆動するドライバ回路とを夫々異なる半導体チップ5a、5b、5cで構成し、前記3つの半導体チップ5a、5b、5cを一つのパッケージ6aに収納し、かつ、前記ハイサイドスイッチ用のパワートランジスタを含む半導体チップ5aと前記ドライバ回路を含む半導体チップ5cとを近接して配置する。

(もっと読む)

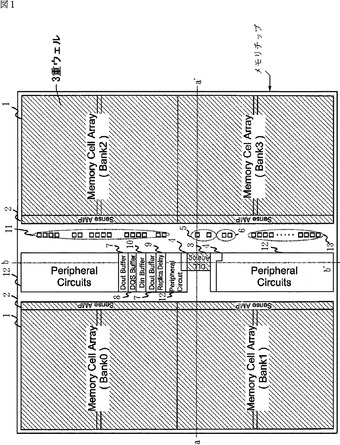

ダイナミック型半導体記憶装置

【課題】安定したクロック発生動作、高精度で低消費電力を実現しDLLを備える。

【解決手段】内部クロック信号を生成するDLL回路、内部クロック信号で動作を制御される周辺回路とメモリセルアレイを含む。第1電源電圧を供給するために同期回路に接続された第1電源パッド、第1電源電圧より低い第2電源電圧を供給するために同期回路に接続された第2電源パッド、周辺回路とメモリセルアレイに第3電源電圧を供給するための第3電源パッド、周辺回路とメモリバンクに第3電源電圧より低い第4電源電圧を供給する第4電源パッドを含む。複数のメモリセルアレイは第1領域と第2領域に分割して配置される。複数の周辺回路は第1領域と第2領域の間の第3領域に配置される。第1、2、3,4電源パッドは第1領域と前記第3領域の間の第4領域に配置されている。

【選択図】図1  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】PAD on I/Oセル構造において、パッド引き出し部のレイアウトをI/O部の略中心に配置し、半導体チップのレイアウト面積を削減する。

【解決手段】I/O部5において、トランジスタ8は、半導体チップの周辺部に最も近い位置にレイアウトされている。このトランジスタ8の上方には、抵抗12がレイアウトされており、抵抗12の上方には、ダイオード10,11がレイアウトされている。ダイオード10,11の上方には、トランジスタ9がレイアウトされており、トランジスタ9の上方には、たとえば、メタル配線層に形成されたパッド引き出し部5aを挟んでロジック部6がレイアウトされている。これにより、パッド2からトランジスタ9のドレインまでを同じノードとすることができるので、パッド引き出し部5aをI/O部5の略中央にレイアウトすることが可能となる。

(もっと読む)

異電源接続検証方法及び異電源接続検証用プログラム並びに記録媒体

【課題】真のエラーか否かの判定を可能とする検証技術を提供する。

【解決手段】異電源接続検証はコンピュータによって行われる。コンピュータ内の中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、その処理結果に基づいて、擬似違反を抑制する第2処理とを含む。上記第2処理は、トランジスタの違反を除外する第3処理を含む。この第3処理において、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定し(S804)、仮定されたトランジスタがオンするために必要なトランジスタのオン状態を探索し(S805)、オン状態又はオフ状態が決定される周辺トランジスタを探索する(S806)。そして貫通電流パスが無い場合には、擬似違反のMOSトランジスタを違反対象から除外する。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】動作速度が高速になっても、パッド再配線間抵抗ばらつきに起因する不良モードの増加を抑えた半導体集積回路装置および半導体集積回路装置の製造方法を提供する。

【解決手段】ウエハ・レベル・パッケージ方式の半導体集積回路装置(LSI)におけるアルミニウム系パッド2pと再配線16との間の抵抗を安定させるために、これら両者の間に下層チタン層、中層窒化チタン層、上層チタン層を含むバリア・メタル層を介在させ、この下層チタン層の厚さを5nm以上、60nm以下とした。

(もっと読む)

半導体装置

【課題】ダイパッド露出型の半導体装置において、使用環境温度が変化した場合に発生しうる樹脂割れを抑制または防止する。

【解決手段】主面1aと下面1bを有する半導体素子1と、半導体素子1が搭載され、かつ半導体素子1の下面1bのドレイン電極19と導電性の接着材9を介して接続するダイパッド3と、ダイパッド3と繋がる吊りリード11と、半導体素子1と電気的に接続された複数のリードと、半導体素子1及びダイパッド3の一部を樹脂封止する封止体10とを有し、ダイパッド3の下面3bが封止体10の下面10bから露出し、吊りリード11の全部または一部の厚さが、ダイパッド3の中央部より薄く形成されていることで、樹脂割れを抑制または防止する。

(もっと読む)

51 - 60 / 4,790

[ Back to top ]