株式会社ルネサステクノロジにより出願された特許

71 - 80 / 4,790

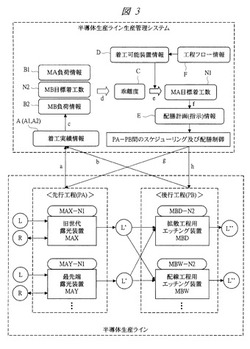

半導体生産管理システム

【課題】半導体生産管理システムに係わり、複数の種類の半導体デバイス、工程フロー、及び製造装置などが混在する生産ライン環境で全体の生産性を向上する。

【解決手段】半導体製品(ロット)単位の工程フローで工程毎に着工可能な製造装置が対応付けられる。本生産管理システムでは、ラインの複数の工程及び製造装置のうち例えば露光工程(先行工程)とエッチング工程(後行工程)の組を対象として、ロット及び部材(レチクル)の配膳及びスケジューリングを制御する。本システムは、各工程の装置の着工実績や負荷の把握に基づく目標着工数(N1,N2)の計算をもとに、先行工程の露光装置に対する着工をロット及び部材の効率よい配膳により制御する。これによって後行工程のエッチング装置へ必要な着工数のロットを送り込むことにより、エッチング装置の目標着工数(N2)が実現される。

(もっと読む)

半導体データ処理デバイス

【課題】物理的な破壊を伴わずに行われる不正なアタックに対しても万全のセキュリティを実現することができる半導体データ処理デバイスを提供する。

【解決手段】半導体データ処理デバイス(2)に、外部からユーザ認証を受けるための認証処理を行う認証処理回路(8)の認証処理により前記ユーザ認証を受けることができなかった場合に、前記認証処理に用いるための情報を保持する記憶回路(3,7)を少なくとも電気的に破壊する破壊回路(10,11)を採用する。前記破壊回路は、例えば、前記記憶回路を構成する回路素子の絶縁を電気的に破壊する昇圧電圧を、動作電源電圧の供給経路に出力可能な昇圧回路である。これにより、半導体データ処理デバイスは、認証が得られないとき自己破壊する。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。

(もっと読む)

半導体装置の製造方法

【課題】hp45nm以降のCMOS半導体装置のような微細構造において、LaO膜を高精度でエッチングして所定の領域にLaO膜を残すことができる半導体装置の製造方法を提供する。

【解決手段】high−kゲート絶縁膜/金属ゲート構造を有する半導体装置の製造方法において、半導体基板の上にhigh−k材料膜とLaO膜を順次形成する工程と、LaO膜の上に、所定の領域を覆うようにマスク層を形成する工程と、マスク層を用いて、LaO膜を選択的に除去するエッチング工程と、マスク層を除去した後に、LaO膜をhigh−k材料膜中に熱拡散させる工程とを含み、エッチング工程が、pH4〜6.8の酸性水溶液を用いてLaO膜を選択的にウエットエッチングする。

(もっと読む)

表示駆動装置

【課題】バックライト減光後の画質を一定レベルに維持するように、バックライト減光率を制御することで、画質と電力削減率とを両立する。

【解決手段】MSE(Mean Square Error)などを画質の指標に用いて、バックライト減光後の画質が一定レベルになるようにデータ伸張率およびバックライト減光率を基準階調制御部(205)で制御する。前フレームのデータ伸張率とバックライト減光率をもとに、表示データを伸張しバックライトを減光した場合の入力表示画像に対する輝度低下量を誤差算出部(203)でMSEとして予め算出し、前記MSEが所定の基準値より大きければ、伸張部(220)によるデータ伸張率および調光制御部(230)によるバックライト減光率を前フレームより小さくする。一方、前記MSEが所定の基準値より小さければ、データ伸張率およびバックライト減光率を前フレームより小さくする。

(もっと読む)

半導体集積回路

【課題】暗号化無線通信に際して暗号鍵を他の電子装置との間で共有する際に、無駄なケーブル配線の増加を回避する。

【解決手段】半導体集積回路100は、暗号化無線通信のための無線通信制御回路116と暗号鍵を管理する処理ユニット112と電力線通信回路114、120を具備する。半導体集積回路100は、電力線通信回路114、120に電力線122を介して外部から供給される電源電圧により動作する。電力線通信回路は、電力線122を介して他の電子装置200A1、200B1…200N1と接続される。無線通信制御回路116は、暗号化無線通信によって他の電子装置と通信する。半導体集積回路100は、無線通信制御回路116を利用して他の電子装置と暗号化無線通信を行う前に、電力線通信回路114、120を介して暗号鍵の情報を他の電子装置に供給する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチゲート型MOSFETのゲートを有する半導体素子の、歩留まりおよび信頼性を高める。

【解決手段】ゲート電極9aの加工時のエッチングガスとして、フッ素系のガスであるSF6を使用することでエッチングの等方性を強め、ゲート電極9aの表面を滑らかに加工することができ、製品の歩留まりおよび信頼性を向上することができる。また、ゲート電極9aの加工時のn+型単結晶シリコン基板1の温度を5℃とすることで、エッチング残渣が加工表面へ再付着するのを防ぎ、加工表面を滑らかな形状にすることにより、トレンチゲート型MOSFETの歩留まりおよび信頼性を高めることができる。

(もっと読む)

半導体装置の製造方法

【課題】Siおよびこれと同族元素であるGe,Cなどの組合せを用いて、低消費電力で高速なMOSFETを有する半導体装置の製造方法を提供する。

【解決手段】Si層1と、その上に形成されたMOSFETのゲート電極16と、Si層1に形成されたソース領域14及びドレイン領域15と、それらの間の領域に形成されるチャネル領域とを有する半導体装置の製造方法において、ソース領域14またはドレイン領域15が形成される領域のSi層1を選択的にエッチングし、形成された溝内にSiGeを選択成長させる。

(もっと読む)

半導体装置の製造方法

【課題】半導体チップのバンプ電極と、配線基板のボンディングリードとの接合部における破断を抑制する。

【解決手段】マトリクス基板(配線基板)11をピックアップして保持する基板保持部TRa、基板保持部TRaを支持する支持部TRb、支持部TRbとともにマトリクス基板11を搬送する搬送部TRc、およびマトリクス基板11を加熱するヒータ(基板加熱部)TRdを有する搬送装置TRを用いて、半導体チップ1の複数の突起電極とボンディングリードとが電気的に接続されたマトリクス基板11を、加熱されたアンダフィル樹脂充填ステージ(第2ステージ)に搬送する。

(もっと読む)

磁気記憶装置

【課題】書き込み特性の安定した磁気記憶装置を提供する。

【解決手段】第1非磁性膜2は記録層3上に設けられている。第1強磁性膜1dは、第1非磁性膜2上に設けられ、かつ第1の磁化M1dおよび第1の膜厚t1dを有する。第2非磁性膜1cは第1強磁性膜1d上に設けられている。第2強磁性膜1bは、第2非磁性膜1c上に設けられ、かつ第1強磁性膜1dと反平行結合し、かつ第2の磁化M1bおよび第2の膜厚t1bを有する。反強磁性膜1aは第2強磁性膜1b上に設けられている。第1の磁化M1dおよび第1の膜厚t1dの積と第2の磁化M1bおよび第2の膜厚t1bの積との和は、記録層の磁化M3aと記録層の膜厚t3aとの積よりも小さい。

(もっと読む)

71 - 80 / 4,790

[ Back to top ]