Fターム[2G132AE16]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 表示 (313)

Fターム[2G132AE16]に分類される特許

81 - 100 / 313

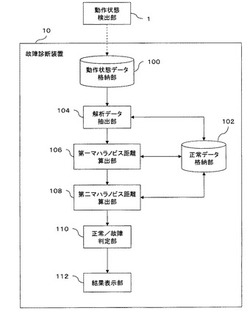

検出データ処理装置及びプログラム

【課題】回路基板における異常又は故障を高精度に検出することを支援する。

【解決手段】故障診断装置10の解析データ抽出部104は、回路基板の動作状態を検出する動作状態検出部1から取得された検出データの複数のグループについて互いに相関関係を求め、他のグループとの相関関係を表す値が予め設定された閾値よりも小さいグループの検出データを解析データとして選択し抽出する。第一マハラノビス距離算出部106は、正常な回路基板を動作させたときの検出データから解析データ抽出部104が抽出した解析データを用いて生成された第一のマハラノビス空間と、診断対象の回路基板を動作させたときの検出データと、に基づいて1段目のマハラノビス距離を算出する。

(もっと読む)

組合せ型スイッチングマトリクスの構築方法およびその半導体装置の試験システム

【課題】 組合せ型スイッチングマトリクスの構築方法において、使用者の作業効率を高めるとともに、試験コストを削減する。

【解決手段】 第1と第2のスイッチングモジュールを選択し、第1と第2のスイッチングモジュールの出力ポートおよび入力ポートを設定し、少なくとも第1の出力ポートうちの一つと第2の入力ポートのうちの一つとを接続することで、組合せ型スイッチングマトリクスを形成し、出力ポートと入力ポートとの接続関係に基づいて接続マッピングテーブルを作成し、チャネル切換えインターフェイスを表示する。チャネル切換えインターフェイスは、複数の入力端子と、出力端子と、仮想スイッチとを備え、入力端子および出力端子の間の経路のオン・オフ状態を表す組合せ型スイッチングマトリクスを表示する。

(もっと読む)

回路部品の試験装置および方法

【課題】被試験体である回路部品に対して試験信号のタイミングに依存することなく任意のタイミングで負荷試験を行うことができる回路部品試験装置および方法を提供する

【解決手段】複数の外付端子T1−T4を有する回路部品10の試験装置は、複数の外付端子にそれぞれ試験負荷を出力する複数の第1バッファアンプAt1−At4と、複数の外付端子の負荷状態をそれぞれ入力し測定信号M1−M4として出力する複数の第2バッファアンプAm1−Am4と、m複数の第1バッファアンプからm試験負荷を出力させながら複数の第2バッファアンプを順次駆動して測定信号を出力させるように制御する制御手段22と、を有する。

(もっと読む)

データ表示装置、データ表示方法およびプログラム

【課題】デバイスの試験用プログラムの修正に伴う試験実行時間の変化を容易に比較することができるデータ表示装置を提供する

【解決手段】デバイスの試験用プログラム毎に計測された実行時間データを格納する実行時間データ格納部と、格納された実行時間データから、基準となる実行時間データと比較対象となる実行時間データの選択を受け付ける操作受付部と、選択された実行時間データについて、比較対象となる実行時間データと基準となる実行時間データとの差分値を表示する実行時間表示制御部とを備える。

(もっと読む)

故障解析装置

【課題】被テストデバイスの不良箇所の位置を3次元的に特定する。

【解決手段】故障解析装置70には、被テストデバイスである半導体デバイス(DUT)21にレーザ光を照射して、照射された被テストデバイスの特定箇所を加熱して熱起電流を発生させるレーザ照射手段と、前記レーザ光を水平方向及び垂直方向に走査して前記被テストデバイスの光加熱抵抗変化画像を撮影する撮影手段と、水平方向の前記光加熱抵抗変化画像と前記被テストデバイスの平面レイアウト画像を水平方向の位置座標が同一となるように重ね合わせる第1の位置座標設定手段と、縦方向の光学ステージ位置情報と前記被テストデバイスの断面情報を縦方向の位置座標が同一となるように重ね合わせる第2の位置座標設定手段とが設けられる。

(もっと読む)

半導体集積回路の故障解析方法、故障解析装置、及び故障解析プログラム

【課題】半導体検査装置から得られた半導体集積回路の異常信号と関連する回路を精度よく抽出する半導体集積回路の故障解析方法、故障解析装置、及び故障解析プログラムを提供する。

【解決手段】半導体検査装置より得た半導体集積回路の解析データに含まれる異常信号データについて解析データにおける装置座標系の座標を求める信号検出工程と、半導体集積回路の複数の基準点について装置座標系の座標と半導体集積回路の設計データにおける設計座標系の座標との対応を求め、装置座標系と設計座標系との座標変換式を求める座標変換工程と、座標変換式による装置座標系の座標と設計座標系の座標との位置誤差を求める誤差算出工程と、座標変換式と位置誤差とを用いて、装置座標系における異常信号の座標から、設計データにおける異常信号に関連する回路を抽出する回路抽出工程と、を有する。

(もっと読む)

イメージセンサおよび電子情報機器

【課題】新たなAD変換回路の追加を行わずに、評価回路のバラツキの影響を受けにくく正確なテストを簡易にかつ高速に行う。

【解決手段】カメラのオートフォーカス機構を実現するボイスコイルモータVCMを制御するVCM制御回路2または2Aが内蔵され、このVCM制御回路2または2A内のDA変換回路101または101Aのテスト出力端子Toutを複数のカラムAD変換回路4の全部または一部の複数の入力端にそれぞれ接続可能に構成し、出力回路5からのデジタル信号により、このVCM制御回路2または2AのDA変換回路101または101Aの性能評価テストを行う。

(もっと読む)

不良解析方法、不良解析システムおよびメモリマクロシステム

【課題】使用者にとってわかりやすいFBMを作成する。

【解決手段】メモリマクロ内に配置された通常セル領域およびスペアセル領域の個数および各セル領域のサイズを含む構成情報を回路設計情報から抽出する構成情報抽出工程(S2)と、メモリマクロに配置された通常セル領域およびスペアセル領域を含めた全てのセル領域に含まれる各メモリセルが不良であるか否かを示す電気テスト結果を順次収集する電気テスト結果収集工程(S5)と、電気テスト結果の収集順に対応する配列情報を構成情報に基づいて2次元座標値に変換する2次元座標値算出工程(S8、S9)と、通常セル領域とスペアセル領域とが識別可能なように電気テスト結果を2次元座標値に基づいて表示する出力工程(S10、S11)と、を備える。

(もっと読む)

試験結果表示装置

【課題】不良発生の原因や傾向をロット単位又はウェハ単位で容易に把握することができる試験結果表示装置を提供する。

【解決手段】ウェハマップ表示装置15は、複数のウェハ上に形成されたDUTに対する試験によって得られた試験結果から、ウェハ上の位置が同じであるDUTについての試験結果を検索するデータ検索部21aと、データ検索部21aによって検索された試験結果を重ね合わせたウェハマップを作成するウェハマップ作成部21bと、ウェハマップ作成部21bで作成されたウェハマップを表示装置15bに表示する表示制御部22とを備える。

(もっと読む)

ポゴタワー電気チャネル自己検査式半導体試験システム

【課題】ポゴタワー電気チャネル自己検査式半導体試験システムの提供。

【解決手段】本ポゴタワー電気チャネル自己検査式半導体試験システムは、ショートボードを提供し、その各接点をロードボード上のポゴタワーの各種ポゴピンに電気的に接続し、それぞれ回路を形成させ、さらに自己検査コントローラが異なる検査信号を各電源チャネル、各伝送チャネル、各駆動チャネルに入力し、上述の回路を通し、複数のパラメータ検出ユニットが各電源チャネル、各伝送チャネル、各駆動チャネルが上述の検査信号を受けて発生する応答信号を検出し並びに判断する。これにより本発明はウエハ試験の前に、各電気チャネルの開路或いは短絡状態が正常であるか、或いは漏電が発生しているか否かを自己検査できる。

(もっと読む)

半導体装置の診断装置及び診断方法

【課題】半導体装置の診断の所要時間を短縮し、且つ、診断の精度を向上させるための半導体装置の診断装置及び診断方法を提供する。

【解決手段】発光解析によって取得された半導体装置の各セルのトランジスタの発光像情報、並びにレイアウトを含む設計情報に基づいて、発光像情報の発光位置情報に対応する故障セルリストを作成し、設計情報から接続関係を示すトランジスタ回路網リスト及び診断パターンを作成する故障セルリスト作成部14aと、設計情報、診断パターン、及び故障辞書に基づいて、セル内のトランジスタの基板電流に関するシミュレーションを実行して、セル内のトランジスタの基板電流を含む発光箇所辞書を作成する発光箇所辞書作成部14cと、発光像情報、設計情報、及び発光箇所辞書に基づいて、第1故障回路網候補の中から第2故障回路網候補を抽出する故障回路網抽出部14dと、第2故障回路網候補を出力する出力部18と、を備えている。

(もっと読む)

半導体試験装置及び半導体試験方法

【課題】ユーザの負担を増大させることなしにユーザの待ち時間を短縮することで効率的に信号波形を観察することができる半導体試験装置及び半導体試験方法を提供する。

【解決手段】半導体試験装置1は、DUT30に試験信号S1〜Snを印加して得られる信号D1〜Dnと所定の判定電圧値とを比較するコンパレータ15bと、コンパレータ15bの比較結果と予め定められた期待値とが一致するか否かを所定のタイミングで判定する判定部16と、判定部16の判定結果が変化する変化点を示す変化点情報を判定部16に設定される判定タイミング毎に記憶する記憶部25と、判定部16に設定した判定タイミングについての変化点情報が記憶部25に記憶されている場合に、コンパレータ15bに設定すべき判定電圧値と記憶部25に記憶されている変化点情報との大小関係に応じてDUT30に対する試験を実施するか否かを制御する制御部24とを備える。

(もっと読む)

診断装置、診断方法および試験装置

【課題】診断時における使用者の負担を軽減することができる。

【解決手段】被試験デバイスを試験する複数の試験モジュールを備える試験装置を診断する診断装置であって、複数の試験モジュールのそれぞれの種類および接続関係が記述された構成情報を記憶する構成記憶部と、構成情報に基づいて、複数の試験モジュールのそれぞれを診断するための診断用パターンを記述したパターンファイルを生成する生成部と、複数の試験モジュールのそれぞれに対して、対応する診断用パターンに応じた診断用信号を発生させて、それぞれの試験モジュールを診断する診断部と、を備える診断装置を提供する。

(もっと読む)

半導体試験装置及び半導体試験方法

【課題】ユーザの負担を増大させることなしにユーザの待ち時間を短縮することで効率的に信号波形を観察することができる半導体試験装置及び半導体試験方法を提供する。

【解決手段】半導体試験装置1は、DUT30に試験信号S1〜Snを印加して得られる信号D1〜Dnと判定電圧値とを比較するコンパレータ15bと、この比較結果と期待値とが一致するか否かを所定のタイミングで判定する判定部16と、予め設定された最小値から最大値まで判定電圧値の大きさを徐々に変化させつつ判定部16の判定結果を取得する第1制御を行い、第1制御が終了する前に取得した判定結果が変化した場合には、判定部16における判定のタイミングを所定量だけ変化させてから第1制御を新たに開始する第2制御を行う制御部24と、制御部24で取得された判定結果を用いてDUTから得られる信号D1〜Dnの信号波形を表示部23に表示する表示制御部26とを備える。

(もっと読む)

半導体試験装置

【課題】ユーザに対して煩雑な作業を強いることなしに直流試験の試験結果を容易に把握することができ、これにより試験効率を高めることができる半導体試験装置を提供する。

【解決手段】半導体試験装置1は、半導体デバイスに直流信号を印加して半導体デバイスから得られる直流信号が所定の規格内であるか否かの試験(直流試験)に用いられる複数の測定装置30a〜30nと、測定装置30a〜30nの各々から得られる測定結果と直流試験の試験条件(パス/フェイル判定に用いる直流信号の許容上限値及び許容下限値)とを関連付けたグラフを作成するグラフ作成部25と、グラフ作成部25で作成されたグラフを表示部27に表示する表示処理部26とを備える。

(もっと読む)

集積回路デバイス構造をナノプロービングするための方法(集積回路デバイス構造のナノプロービング)

【課題】集積回路のデバイス構造をナノプロービングするための方法を提供する。

【解決手段】この方法は、デバイス構造の第1の領域全体にわたって、第1の領域に近接する少なくとも1つのプローブを使用して、1次荷電粒子ビームを走査することを含み、デバイス構造の第2の領域は1次荷電粒子ビームからマスクされる。この方法は、2次電子イメージを形成するために、デバイス構造の第1の領域および少なくとも1つのプローブから放出される2次電子を収集することをさらに含む。2次電子イメージは、結像部分としての第1の領域および少なくとも1つのプローブと、非結像部分としての第2の領域とを含む。別の方法として、第2の領域は、第1の領域よりも速い走査速度で荷電粒子ビームによって走査可能であるため、結果として第2の領域は2次電子イメージの結像部分でもある。

(もっと読む)

電子ビーム吸収電流解析方法及び電子ビーム吸収電流解析器

【課題】解析対象ネットに対して前段に位置する前段ネットからのEBAC反応を防止した解析ヒット率の高いEBAC解析方法及びそれに好適な装置を提供する

【解決手段】解析対象である解析対象ネット1000に対して出力用のプリアンプ3に接続された第1のプローブ針1を接触する。また、前段ネット1100または前段ネット1100の電源配線1010に設置された第2のプローブ針2を接触する。プローブ針の接触後、電子ビームを照射し解析対象ネット1000に対する。解析対象ネット1000に蓄積された電荷はプリアンプ3を介して外部に出力される一方で、前段ネット1100に蓄積された電荷は第2のプローブ針2を介して出力され前段ネットから排除される。これにより、EBAC解析時には前段ネット1100の誤表示を防ぐことができる。

(もっと読む)

モジュール状態表示装置及びソースコードデバッガ

【課題】操作性が高いモジュール状態表示装置12及びソースコードデバッガを提供する。

【解決手段】モジュール状態表示装置12は、ICテスタ14を構成する各モジュールの設定状態を表示する装置であって、各モジュールの設定状態が記述されているテストプログラムのソースコードから表示させたいモジュール情報を選択する選択部43と、選択されたモジュール情報を各モジュールの設定状態を表示するモジュール状態表示エリアに登録する登録部44と、登録部44により登録されたモジュール情報を自動更新する自動更新部45とを備える。ユーザに表示させたいモジュール情報をソースコードから選択させ、選択されたモジュール情報を登録し、登録されたモジュール情報をポーズ行ごとに自動更新する。

(もっと読む)

試験測定機器、測定システム及び方法

【課題】ある試験測定機器が検出したイベントにより、他の試験測定機器の取り込みをトリガする際に、正確な同期をとれるようにする。

【解決手段】ハブ18は、複数の試験測定機器12〜15の各々に結合されている。各試験測定機器は、ハブから受けたハブ・イベントに応答して取り込みをトリガする。この際、各試験測定機器は、機器イベントを発生し、ハブは、これら機器イベントを組合せてハブ・イベントを発生する。各試験測定機器は、ハブから入力部までのコミュニケーションの時間遅延にほぼ類似の出力部からハブまでのコミュニケーションの時間遅延がある。構成モードでは、ハブが試験測定機器から受けたイベントを試験測定機器に戻し、試験測定機器がハブから戻るイベントの時間を測定する。

(もっと読む)

半導体試験装置、半導体試験方法および半導体試験プログラム

【課題】被試験デバイスの試験に要する時間をより詳細に測定して、試験速度の高速化および生産性の向上を図ることを目的とする。

【解決手段】DUT2のテストを行う1または複数の制御カード1と当該制御カード1の制御を行うコントローラ3とを備える半導体試験装置であって、制御カード1に備えられ、この制御カード1に設けたテスト実行部13を制御するために要する制御時間TBを計測するカード側タイマ12と、コントローラ3に備えられ、カード側タイマ12が測定する制御時間TBに基づいてテスト実行部13がDUT2のテストを行うために確保される待機時間TWを変更する待機時間変更部24と、を備えている。

(もっと読む)

81 - 100 / 313

[ Back to top ]