Fターム[2H092JA41]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | ソース、ドレイン電極 (2,019)

Fターム[2H092JA41]の下位に属するFターム

Fターム[2H092JA41]に分類される特許

1 - 20 / 1,146

液晶表示装置

液晶表示装置

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明の液晶表示装置の製造方法によれば、高い表示品位を有する液晶表示装置を製造できる。

【解決手段】液晶表示装置の製造方法は、第2基板22の主面21a上に遮光膜BMを形成する工程と、遮光膜BMを覆うように第1絶縁膜226を形成する工程と、第1絶縁膜226上に透光性の導体層100を形成する工程と、導体層100上にレジストREを形成する工程と、第2基板22の反対主面22b側から、遮光膜BMと重ならない部分のレジストREを露光する工程と、レジストRE上にマスクPMを配置して、レジストREのうち遮光膜BMの形成領域上に位置するレジストREの一部をマスクPM側から露光する工程と、導体層100の一部を露出させる工程

と、導体層100の露出した一部をエッチングし、レジストを除去して、遮光膜BMの形成領

域上に信号電極228および共通電極227を形成する工程とを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供する。

【解決手段】ガラス基板上に設けられたボトムゲート構造のスタガ型トランジスタを有する半導体装置において、ゲート電極層上に組成を異なる第1のゲート絶縁膜及び第2のゲート絶縁膜が順に積層されたゲート絶縁膜を設ける。又は、ボトムゲート構造のスタガ型トランジスタにおいて、ガラス基板とゲート電極層との間に保護絶縁膜を設ける。第1のゲート絶縁膜と第2のゲート絶縁膜との界面、又はゲート電極層とゲート絶縁膜との界面における、ガラス基板中に含まれる金属元素の濃度を、5×1018atoms/cm3以下(好ましくは1×1018atoms/cm3以下)とする。

(もっと読む)

電気光学装置および電子機器

【課題】シリケートガラスによって、シール材と基板との界面からの水分の侵入や、シール材で囲まれた領域内に侵入した水分の影響を低減することのできる電気光学装置、および当該電気光学装置を備えた電子機器を提供すること。

【解決手段】電気光学装置100では、素子基板10および基板本体10w(第1基板)側においてシール材107と接するのは、BSG膜からなるシリケートガラス層18(第1シリケートガラス層)であり、対向基板20および基板本体20w(第2基板)側においてシール材107と接するのは、BSG膜からなるシリケートガラス層28(第2シリケートガラス層)である。シール材107で囲まれた領域で、シリケートガラス層18は、画素電極9aおよびダミー画素電極9bの非形成領域9cで液晶層50に表面を向けており、シリケートガラス層28は、共通電極21の非形成領域21cで液晶層50に表面を向けている。

(もっと読む)

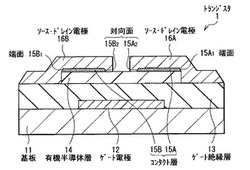

薄膜トランジスタ

【課題】バックライトの間接光に起因するリーク電流を低減可能な薄膜トランジスタを提供する。

【解決手段】表示装置用のボトムゲート型の薄膜トランジスタであって、基板1と、ゲート電極配線2と、ゲート絶縁膜3と、チャネルとなる第1の半導体層4と、第1及び第2のコンタクト層5a、5bとなる第2の半導体層と、ソース又はドレイン電極配線7a、7bとを有し、ソース又はドレイン電極配線7a、7bに対して露出する第2の半導体層の露出部に、絶縁性半導体層6a、6bが形成されている。

(もっと読む)

液晶パネル、液晶プロジェクタ装置

【課題】プロセスの増大に伴う生産性の低下やコストアップなどの問題を招来することなく、ダミー画素へのパネル出射面側からの光入射に起因した画質低下の防止を図る。

【解決手段】有効画素領域の周囲に形成されたダミー画素のうち上記有効画素領域内の画素と同じ画素列に配されるダミー画素を同列ダミー画素としたとき、少なくとも当該同列ダミー画素が有するトランジスタと信号線との間の電気的接続を断つ。これにより、光照射に伴う上記トランジスタの性能劣化に起因して生じる有効画素領域におけるV−T特性の変動を効果的に防止でき、画質低下を防止する。トランジスタと信号線との電気的接続を断つには、接続するためのコンタクト部の形成を省略でき、同時に、別途の層を新たに形成するなどといったプロセスの増加を伴わない。

(もっと読む)

半導体装置の作製方法

【課題】量産性の高い新たな半導体材料を用いた大電力向けの半導体装置の作製方法を提供する。

【解決手段】GRTA装置を用いて、第1の酸化物半導体膜に熱を加え、熱が加えられた第1の酸化物半導体膜に、酸素を添加して第2の酸化物半導体膜とし、GRTA装置を用いて、酸素が添加された第2の酸化物半導体膜に熱を加える。GRTA装置は、高温のガスを用いて加熱処理を行う装置であって、当該GRTA装置を用いると短時間での高温加熱処理が可能となる。

(もっと読む)

液晶表示装置、表示モジュール及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

液晶表示装置

【課題】 信頼性の高い液晶表示装置を提供する。

【解決手段】 マトリクス状に配置された複数の画素電極PEと、画素電極PEが配列する行に沿って延びるゲート配線Gと、列に沿って延びるソース配線Sと、複数の画素電極PEが配置された領域ACTの周囲の領域において画素電極PEと同層に配置され、ゲート配線Gと同層に配置された第1導電体とソース配線Sと同層に配置された第2導電体とを電気的に接続する電極EBと、電極EBの端部に沿って設けられた突起200と、を備えた第1基板ARと、複数の画素電極PEが配置された領域ACTおよび周囲の領域と対向した共通電極CEを備え第1基板ARと対向して配置された第2基板CTと、第1基板ARと第2基板CTとの間に挟持された液晶層LQと、を備えた液晶表示装置。

(もっと読む)

液晶表示装置

【課題】 1つの表示領域を2つの領域に分割し、当該2つの領域に並行して映像や画像を表示する液晶表示装置におけるドライバ回路の発熱を抑え、かつ、画質の低下を防ぐ。

【解決手段】 液晶表示パネルの1つの表示領域は、走査信号線の延在方向と一致する境界線により第1の表示領域と第2の表示領域に分割されており、前記第1の表示領域の画素のTFT素子が接続している映像信号線と、前記第2の表示領域の画素のTFT素子が接続している映像信号線とは、電気的に絶縁されており、前記第1の表示領域および前記第2の表示領域のそれぞれの表示領域において、前記映像信号線の延在方向に沿って並んだ複数個の画素の列には、それぞれ、2本の隣接する映像信号線のうちの一方の映像信号線にTFT素子が接続している画素と、前記2本の隣接する映像信号線のうちの他方の映像信号線にTFT素子が接続している画素とが、交互に並んでいる液晶表示装置。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

液晶表示装置及びその不良画素修復方法

【課題】本発明は、液晶表示装置及びその不良画素の修復方法を提供する。

【解決手段】第1の絶縁基板と、第1の絶縁基板上に実質的に第1の方向に互いに平行するように配値されたゲート配線およびストレージ配線と、ゲートおよびストレージ配線と絶縁されて交差し、実質的に第2の方向に配値されたデータ配線と、データ配線上に形成された保護膜と、保護膜上に形成された第1の画素電極と第2の画素電極と、第1の画素電極に隣接する第2の画素電極を含み、ストレージ配線は、実質的に第1の方向に配値された水平部および水平部から実質的に第2の方向に分枝し、データ配線とオーバーラップする垂直部を含み、垂直部は、第1の画素電極および第2の画素電極とオーバーラップし、第1の画素電極と垂直部がオーバーラップする幅は第2の画素電極および垂直部の間のオーバーラップする幅と実質的に同一であることを特徴とする液晶表示装置。

(もっと読む)

液晶表示装置

【課題】信号配線と配向膜ストッパとの間における電界の発生を抑制することが可能な技術を提供することである。

【解決手段】

表示領域よりも外側の領域に形成され、少なくとも表示領域の2つの異なる辺に沿って形成される配向膜ストッパを有し、該配向膜ストッパは液状の配向膜材料に対して疎水性を有する薄膜材料からなり、配向膜ストッパの塗布時において、第1基板側の最上層に形成される第2の導電体層SPと、絶縁膜を介して第2の導電体層SPの下層に配置され、第2の導電体層SP側から平面的に見て、第2の導電体層SPの長手方向の辺縁部が露出するように配置される第1の導電体層SHとからなり、第1の導電体層SHが表示領域の辺部に配置される信号線と第2の導電体層SPとの間の薄膜層に形成されてなる液晶表示装置である。

(もっと読む)

液晶表示装置

【課題】製造コストを削減するとともに歩留まりを向上し、かつプロセス設計が容易である液晶表示装置を提供すること。

【解決手段】液晶表示装置1において、半導体層ASIと半導体層ASIの液晶材側の面に形成された金属層Mとの積層部分であり、かつ画素電極MITの液晶材側の面に重なる部分である重なり部50を含むソース電極SD2を有し、第2の絶縁層PAS2は、ソース電極SD2の液晶材側の面から重なり部の50端部、及び画素電極MITの一部を開口するように形成されており、ソース電極SD2の液晶材側の面から重なり部50の端部上、及び画素電極MIT上に、ソース電極SD2の液晶材側の面から重なり部50の端部、及び画素電極MITを導通させる導体膜70が形成されている。

(もっと読む)

液晶表示装置およびその製造方法

【課題】映像信号線のパターニング時における映像信号線の断線を防止する。

【解決手段】映像信号線107、ドレイン電極107、ソース電極107は同層で同時に形成される。映像信号線107等はベース層1071、AlSi層1072、キャップ層1073の3層によって形成される。従来は、AlSi層1072において、キャップ層1073との境界にエッチングレートの早い合金が形成されて映像信号線107等のパターニング時、断線を生じていた。本発明では、映像信号線107等の形成時、AlSi層1072をスパッタリングによって形成した後、TFTを大気にさらし、AlSi層の表面にAl酸化層を形成した後、キャップ層1073をスパッタリングによって形成する。これによってAlSi層に、エッチングレートが部分的に早くなる合金が発生することを防止し、映像信号線等の断線の発生を防止する。

(もっと読む)

アクティブマトリクス基板

【課題】アクティブ動作中に外部電源による電位の制御を必要としない静電気保護回路を有するアクティブマトリクス基板を提供する。

【解決手段】本発明のアクティブマトリクス基板1は、複数のゲート配線22と、複数のソース配線21と、高電位側ESDリング31及び低電位側ESDリング32と、ゲート配線22及びソース配線21の各々に対応して配置されアノード電極が低電位側ESDリング32に接続されカソード電極がゲート配線22及びソース配線21のうちの一の配線に接続されたESDダイオード42と、アノード電極が当該一の配線に接続されカソード電極が高電位側ESDリング31に接続されたESDダイオード41と、2本以上のゲート配線22の各々に対応して配置されアノード電極が低電位側ESDリング32に接続されカソード電極が対応するゲート配線22に接続された低電位固定ダイオード43とを備える。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明は、製造工程を単純化して透明導電膜上に金属膜が積層された積層構造を有する共通電極配線を製造することができる液晶表示装置の製造方法を提供する。

【解決手段】液晶表示装置の製造方法であって、透明導電膜10上に金属膜11が積層された積層構造を有する枠状の共通電極配線12と、透明導電膜10の配線幅よりも小さい配線幅を有する共通電極13と、共通電極配線12の透明導電膜10の配線幅よりも小さい配線幅を有する画素電極14とからなる横電界方式において、感光性樹脂膜15をエッチングマスクにして等方性エッチングにより、共通電極13および画素電極14となる透明導電膜10上に積層された、感光性樹脂膜15の下側に位置する金属膜11を除去するとともに、共通電極配線12となる透明導電膜上10に積層された、感光性樹脂15の下側に位置する金属膜11の側面の一部を除去する工程を含む。

(もっと読む)

1 - 20 / 1,146

[ Back to top ]