Fターム[3C081BA32]の内容

Fターム[3C081BA32]に分類される特許

61 - 80 / 317

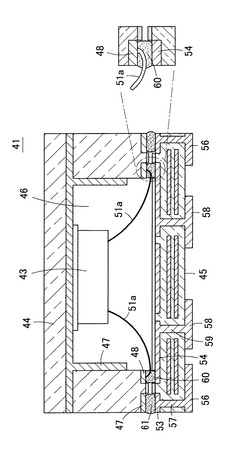

半導体装置及びマイクロフォン

【課題】半導体素子を実装する部材と信号入出力手段を設けている部材とが別部材となったパッケージ構造を有する半導体装置の構造を簡略にする。

【解決手段】マイクロフォン41のパッケージを、カバー44と基板45によって構成する。カバー44に設けた凹部46内にはマイクチップ42と回路素子43を納めて凹部46の天面に接着固定する。凹部46の外側においてカバー44の下面には複数個のボンディング用パッド48を設ける。回路素子43にボンディングワイヤ51aの一端を接続し、その他端をボンディング用パッド48に接続する。基板45は信号入出力手段として信号入出力端子58を有しており、基板45の上面には信号入出力端子58と導通した接続電極54がボンディング用パッド48と対向して設けられている。基板45とカバー44は、接続電極54とボンディング用パッド48を導電性接着剤やハンダなどの導電性部材60により接合される。

(もっと読む)

電子装置の製造方法

【課題】特性の良い機能素子を有する電子装置を製造できる製造方法を提供する。

【解決手段】電子装置の製造方法によれば、基板10の上方に機能素子20を形成する工程と、機能素子20を覆う層間絶縁層30a,30b,30cを形成する工程と、機能素子20の上方であって、層間絶縁層30a,30b,30cの上方に第1被覆層40を形成する工程と、第1被覆層40に貫通孔42を形成する工程と、層間絶縁層30a,30b,30cの上方および第1被覆層40の上方に樹脂層50を形成する工程と、貫通孔42の上方の樹脂層50に、貫通孔42と連通する開口部52を形成する工程と、貫通孔42を通して機能素子20の上方の層間絶縁層30a,30b,30cを除去し、空洞部32を形成する工程と、貫通孔42の上方に第2被覆層60を形成して、貫通孔42を塞ぐ工程と、を含む。

(もっと読む)

半導体装置

【課題】MEMS装置が備える性能を十分に発揮しうる装置構成を採用しつつ、徒らに製造工程数が増加することを防止し、製造時間の短縮を図ることができる半導体装置を提供する。

【解決手段】基板2と、基板2上に設けられる有機絶縁膜3と、有機絶縁膜3上に、有機絶縁膜3よりも薄く形成される無機絶縁膜4と、無機絶縁膜4上に形成され、その内部にMEMS素子5を中空に封止する中空封止構造体6と、有機絶縁膜3と無機絶縁膜4とを貫通して形成される貫通孔7と、貫通孔7に充填されて基板2に形成される電極とMEMS素子5とを電気的に接続する導電性部材8とを備える。

(もっと読む)

貫通電極、微小構造体及びそれらの製造方法

【課題】短時間で製造することができ、十分な気密性を有するとともに、基板の反りを低減させることができる貫通電極、微小構造体及びそれらの製造方法を提供する。

【解決手段】導電性を有する基板10の所定領域を貫通トレンチ21で囲み、貫通トレンチ21内に絶縁膜50を形成して周囲から絶縁分離した貫通電極60において、絶縁膜50は、貫通トレンチ21の側面から化学気相成長させたシリコン膜40を熱酸化したシリコン熱酸化膜50である。

(もっと読む)

電気機械変換装置及びその作製方法

【課題】所望の周波数帯域で良好な感度を有する二次元容量型電気機械変換装置などの電気機械変換装置を無欠陥ないし歩留まり良く作製することを可能とする技術を提供する。

【解決手段】電気機械変換装置は少なくとも1つのセルを含むエレメント1、2、3を複数個有する。複数のエレメントト1、2、3は、複数の処理回路が形成された集積回路基板5上のそれぞれ対応する処理回路に対して、互いに分離して独立的に配置され、各エレメント毎に信号の入出力ができる様に、対応する複数の処理回路とそれぞれ機械的及び電気的に結合されている。

(もっと読む)

アクチュエータ、液滴噴射ヘッド及びその製造方法、並びに液滴噴射装置

【課題】高い信頼性を有するアクチュエータ、液滴噴射ヘッド、並びにそれらの製造方法と液滴噴射装置を提供する。

【解決手段】アクチュエータ200は、第1の面を有する基板と、第1の方向に延びる複数の第1の導電層40と、第1の導電層40の少なくとも一部を、それぞれ覆うように形成された第1の部分51と、第1の部分51以外の第2の部分52aと、を有する、圧電体層50と、第1の面と直交する方向から見て、第1の導電層40の少なくとも一部とオーバーラップし、かつ、第1の部分51の少なくとも一部を覆う第2の導電層60と、第2の導電層60の上に形成され、第1の方向に延びる第1リード配線71と、第1リード配線71の一部を覆うように形成された保護膜80と、を含み、圧電体層50は複数の第1の開口部56を有し、圧電体層50の第1の部分51は、第1の開口部56に挟まれた部分である。

(もっと読む)

犠牲領域を有する静電容量型電気機械変換装置

【課題】高電圧が誤って印加された場合でも、セルないしエレメントの破壊を防ぐことが可能な容量型電気機械変換装置を提供することである。

【解決手段】静電容量型電気機械変換装置は、第1の電極2と、空隙4を介して第1の電極2と対向して配置された第2の電極3と、を含むセルを少なくとも1つ有する。絶縁体で構成される犠牲領域7が備えられ、犠牲領域7は、セルを含む駆動領域6において短絡を起こす短絡電圧より低い電圧が印加されることで短絡を起こす様に構成される。第一電極2と第二電極3は、犠牲領域7を含む絶縁部を挟んだ構成で、それぞれ電気的に接続されている。

(もっと読む)

マイクロミラーアレイ基板及びマイクロミラーアレイ基板の製造方法

【課題】より容易にマイクロミラーアレイ基板を製造すること。

【解決手段】基板3上に配列させた金属柱22を封止膜23で被覆し、封止膜23と金属柱22の表面が略面一となるように研削して、封止膜23の表面から金属柱22の上端面22aを露出させる際、その上端面22aを研磨して鏡面加工を施し、光反射面2として形成することにより、マイクロミラーアレイ基板1Aのミラー面に複数の光反射面2を一括して形成することを可能にした。

(もっと読む)

電気機械変換デバイスおよび電気機械変換デバイスの製造方法ならびに電気機械変換デバイスの製造に用いる半導体ウエハー

【課題】生産性の向上を図ることのできる電気機械変換デバイスおよび電気機械変換デバイスの製造方法ならびに電気機械変換デバイスの製造に用いる半導体ウエハーを提供する。

【解決手段】電気機械変換デバイスは、基板2に設けられた可動部3と、可動部3に設けられた圧電素子4と、圧電素子4と電気的に接続された第1および第2圧電素子側電極41,42と、を備えている。また、圧電素子4と絶縁状態で実装される信号処理回路5と、信号処理回路5と電気的に接続された第1および第2信号処理回路側電極51,52と、圧電素子4と信号処理回路5とを、圧電素子4の分極処理後に短絡する導電体71,72と、を備えている。そして、基板2の表面の周端縁には、少なくとも圧電素子4の分極処理の際に第1および第2圧電素子側電極41,42と接続されている第1および第2延設電極91,92が形成されている。

(もっと読む)

MEMSセンサ及びその製造方法

【課題】 特に、内部配線層への電気的接続性及び内部空間の高さ寸法のばらつきを小さくすることが可能なMEMSセンサ及びその製造方法を提供することを目的としている。

【解決手段】 第1の基板21と、第2の基板22と、前記第1の基板21の表面に形成される第1のSiO2層25と、前記第1の基板21と前記第1のSiO2層25との間に形成される内部配線層24と、前記第1のSiO2層25の表面25aから前記内部配線層24にかけて形成される貫通孔26と、前記貫通孔26内に形成され前記内部配線層24と電気的に接続される電気接続層28と、前記第2の基板22と前記第1のSiO2層25との間に位置し、前記第2の基板22と前記第1の基板21間に形成される内部空間S2の高さ寸法を規制する突出形状の第1の窒化シリコン層33と、を有することを特徴とする。

(もっと読む)

MEMS及びASICを備える小型化した電気的デバイス及びその製造方法

本発明は、MEMSチップ及びASICチップを備える小型化した電気的デバイスに関する。MEMSチップ及びASICチップは互いに上下に配置する。これら両チップの内部接続部は、MEMSチップ又はASICチップを貫通するビアを介して電気的デバイスの電気的外部接続端子に接続する。 (もっと読む)

マイクロ可動デバイス

【課題】MEMSが搭載される半導体基板と高周波動作で使用される電子部品との電磁的な結合を低減しつつ、そのような電子部品をその半導体基板上に形成する。

【解決手段】可動電極12を覆うようにして可動電極12と間隔を空けて配置された絶縁層13およびキャップ膜14を層間絶縁層8上に形成し、可動電極12の周囲には空洞Uを形成し、キャップ膜14上には導電層15aを形成するとともに、層間絶縁層8上には再配線15bが形成され、導電層15aにて伝送線路を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】素子面積を小さくしたMEMS素子などの電子デバイスを組み込んだ半導体装置およびその製造方法を提供する。

【解決手段】MEMS素子本体11の両面に機能部材が露出するようにして面積を小さくしたMEMS素子10をフリップチップ実装するに際し、MEMS素子本体11に第1実装用基板13を接合し、その第1実装用基板13ごとボンディングツールで吸着して、回路基板20へフリップチップ実装する。また、MEMS素子本体11の上下面に位置する金ボール12、27によって第1空間部S1、第2空間部S2を形成するとともに、金ボール12、27を対向して配置することで、接合時におけるMEMS素子本体11の破損を防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】引き出し電極の抵抗値が小さく、引き出し電極の周りで寄生容量が形成され難い半導体装置およびその製造方法を提供する。

【解決手段】シリコンからなるベース基板B4であって、絶縁分離された複数個のベース半導体領域Bsが上面の表層部の所定領域R1に形成されてなるベース基板B4と、シリコンからなるキャップ基板C4であって、ベース基板B4の所定領域R1において、下面がベース基板B4の上面に貼り合わされるキャップ基板C4とを有してなる半導体装置100において、下面が所定のベース半導体領域Bsに接続し、キャップ基板C4を貫通するようにして、上面がキャップ基板C4の上面まで伸びる、金属40で構成された引き出し電極De1が、当該引き出し電極De1の周りにおいて、キャップ基板C4との間に溝35を有するように形成されてなる半導体装置100とする。

(もっと読む)

電子装置

【課題】ガスの発生に起因する空洞部内の圧力の上昇を回避でき、機能構造体の動作を良好な状態に保持できる電子装置の提供。

【解決手段】電子装置101は、基板1と、基板1上に形成された機能素子を構成するMEMS構造体3Xと、MEMS構造体3Xが配置された空洞部Sを画成し密封する被覆構造部20と、を備え、被覆構造部20は、空洞部Sの周囲を取り巻くように基板1上に形成された層間絶縁膜4,6と機能層3、配線層5とを含み、被覆構造部20のうち空洞部Sを周囲から被覆する周囲被覆部21に、機能層3、配線層5の少なくとも一部で形成された包囲壁22(第1包囲壁23、第2包囲壁24)が空洞部Sに露出するように設けられ、包囲壁22(第1包囲壁23、第2包囲壁24)の少なくとも一部が、ガス吸蔵性を有していることを特徴とする。

(もっと読む)

貫通電極及びその製造方法、並びに微小構造体

【課題】封止領域の気密性を高めることができる貫通電極及びその製造方法、並びに微小構造体を提供する。

【解決手段】導電性を有する基板10の所定領域11を周囲と絶縁して形成した貫通電極100であって、前記基板の第1の面側に、前記基板を貫通しない深さに形成された第1のトレンチ30と、該第1のトレンチより溝幅が狭く、該第1のトレンチの底面と前記基板の第2の面とを貫通する第2のトレンチ20と、該第2のトレンチを充填するとともに、前記第1のトレンチの溝表面を覆う絶縁層50と、前記第1のトレンチの溝表面を覆う前記絶縁層上に、前記第1のトレンチの両側の内壁に沿うとともに、前記第1のトレンチの底面を横断する横断部62を含むように形成された成長膜60と、を含む。

(もっと読む)

領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法

【課題】従来の領域分割基板と較べて部分領域を引き出し導電領域として利用した場合の抵抗値が小さく、導電性、半導電性または絶縁性の任意の基板材料を用いることができ、適用制限の少ない領域分割基板およびそれを用いた半導体装置ならびにそれらの製造方法を提供する。

【解決手段】基板30の第1表面S1から第2表面S2に亘って、当該基板30を貫通するように形成されたトレンチ31aによって、当該基板30が複数の部分領域Ceに分割され、トレンチ31aによって形成された部分領域Ceの側壁に、第1表面S1の側から第2表面S2の側に亘って、当該基板30より高い導電率を有する導電層35が形成され、導電層35を介して、トレンチ31a内に絶縁体31bが埋め込まれてなる領域分割基板A10とする。

(もっと読む)

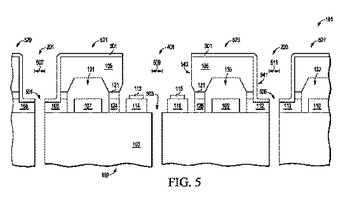

ウェハ構造の電気的結合

第1ウェハ105を第2ウェハ103に電気的に結合する方法が提供される。方法が、結合物質121を用いて第1ウェハを第2ウェハに結合することを含む。方法が、第2ウェハのスクライブ領域141または143における第1ウェハに開口201または203を形成して、第2ウェハの導電性構造108または112の表面を露出させることをさらに含む。方法が、第1ウェハおよび第1ウェハの開口の上方に導電性層301を形成し、導電性層が第2ウェハの導電性構造108または112との電気的接続を形成し、第1ウェハを第2ウェハに電気的に結合することをさらに含む。  (もっと読む)

(もっと読む)

マイクロ・エレクトロ・メカニカル・システム(MEMS)デバイスのための音響(acoustic)エアチャネルを有するリードフレームベースのプリモールドされたパッケージ

マイクロ・エレクトロ・メカニカル・システム(MEMS)デバイス(100)が、キャリア面(111)上に中央に開口するキャビティを画定する窪み(117)を有する。前記キャリア面の周囲に導電性リード(112)が組み込まれる。集積回路チップ(101)を含むインセット(120)が、前記窪みの上部(114、116)内に適合され、前記キャビティの覆いとなる。電気的接続(130)が、前記導電性リードを前記チップ上の端子と接続する。前記集積回路チップ及び電気的接続を囲む前記キャリア面にカバー(140)が取り付けられる。周囲環境から前記キャビティを介してチップ内の可動フォイル(105)まで、前記カバー内の孔(141)、前記インセット内の第1及び第2の開口(121、122)、及び集積回路チップ内の開口(104)を含む経路を通して、エアチャネルが提供される。 (もっと読む)

半導体パッケージの製造方法

【課題】MEMS素子を搭載した半導体パッケージを確実にかつ効率的に製造することができ、MEMS素子を搭載した信頼性の高い半導体パッケージを提供する。

【解決手段】(a)シリコンウエハ10に、厚さ方向に貫通するビア13と、MEMS素子搭載面とは反対面側にビア13と電気的に接続する配線パターン16を形成する工程と、(b)シリコンウエハ10のMEMS素子搭載面に、ビア13とMEMS素子20とを電気的に接続してMEMS素子ウエハ18を接合する工程と、(c)シリコンウエハ10に接合されたMEMS素子ウエハ18のMEMS素子20を個別に分離する工程と、(d)シリコンウエハ10のMEMS素子搭載面に、個別に分離されたMEMS素子20が搭載された領域ごとに、MEMS素子20を収容する凹部25を備えたリッド25を接合する工程と、(e)シリコンウエハ10とリッド24との接合体を個片化して半導体パッケージを形成する工程とを備える。

(もっと読む)

61 - 80 / 317

[ Back to top ]