Fターム[4G077AB01]の内容

結晶、結晶のための後処理 (61,211) | 結晶自体の特徴 (2,433) | 不純物濃度、キャリア濃度、転位濃度の特定 (795)

Fターム[4G077AB01]に分類される特許

141 - 160 / 795

炭化珪素単結晶基板および炭化珪素単結晶エピタキシャルウェハ

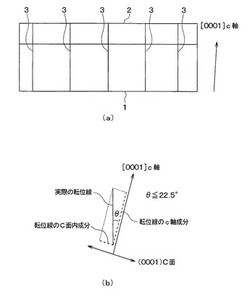

【課題】デバイス特性の劣化や、歩留まりの低下を抑制するため、貫通転位の転位線の方向を規定する。

【解決手段】貫通転位3の転位線の方向が揃えられ、貫通転位3の転位線の方向と[0001]c軸とが平行となるようにする。[0001]c軸方向に転位線を持つ貫通転位3は、基底面転位の転位線の方向と垂直であるため、C面内の拡張転位とはならず、積層欠陥を発生させることがない。このため、貫通転位3の転位線の方向が[0001]c軸であるSiC単結晶基板に対して電子デバイスを形成すれば、デバイス特性は良好となり、劣化が無く、歩留まりも向上したSiC半導体装置とすることができる。

(もっと読む)

エピタキシャル炭化珪素単結晶基板及びその製造方法

【課題】オフ角度の小さな炭化珪素単結晶基板上に、高品質でドーピング密度の面内均一性に優れた炭化珪素エピタキシャル膜を有するエピタキシャル炭化珪素単結晶基板、及びその製造方法を提供する。

【解決手段】オフ角度が1°以上6°以下の炭化珪素単結晶基板上に、ドーピング密度の面内均一性に優れた炭化珪素エピタキシャル膜を有するエピタキシャル炭化珪素単結晶基板、及び、その製造方法であり、上記エピタキシャル膜が、0.5μm以下のドープ層と0.1μm以下のノンドープ層とを繰り返し成長させており、そのエピタキシャル成長において、ドープ層を形成する場合には材料ガス中の珪素原子数に対する炭素原子数の比(C/Si比)を1.5以上2.0以下とし、その時にドーピングガスである窒素を導入してドープ層とする。ノンドープ層を形成する場合にはC/Si比を0.5以上1.5未満とする。

(もっと読む)

β−Ga2O3単結晶

【課題】バンドギャップがより大きく、紫外領域で発光する可能性があるβ−Ga2O3単結晶において、所定の抵抗率及びキャリア濃度を有するβ−Ga2O3単結晶を提供する。

【解決手段】β−Ga2O3単結晶において、Si濃度を1×10−5〜1mol%に変化させることにより、抵抗率が2.0×10−3〜8×102Ωcm、キャリア濃度が5.5×1015〜2.0×1019/cm3の範囲に制御するドーパントの添加濃度に応じて抵抗率を可変することができる。

(もっと読む)

炭化珪素半導体エピタキシャル基板の製造方法

【課題】点欠陥の少ない炭化珪素半導体エピタキシャル基板を製造する方法を提供する。

【解決手段】本発明の炭化珪素半導体エピタキシャル基板の製造方法は、オフセット角が2°以上10°以下である炭化珪素単結晶基板10を用意する工程と、化学気相堆積法により、1400℃以上1650℃以下の温度で、炭化珪素からなるエピタキシャル層11を前記炭化珪素単結晶基板上に成長させる工程と、前記エピタキシャル層を1300℃以上1800℃以下の温度で熱処理する工程とを包含する。

(もっと読む)

半絶縁性のIII族メタルナイトライドおよびその製造方法

【課題】エレクトロニクス製品、および/または、オプトエレクトロニクス製品に利用するGaNデバイスを加工する基板として、大きく、高純度で、低コストの単結晶半絶縁性のガリウムナイトライドを提供する。

【解決手段】およそ5ミリメーターよりも長い結晶構造の基板部材と、他の結晶構造を実質的に保有しない特徴のウルツ鉱型構造と、前記他の結晶構造の体積は、ウルツ鉱型構造の体積のおよそ1%以下であって、不純物濃度がおよそ1015 cm-1よりも大きいLi、Na、K、Rb、Cs、Mg、Ca、F、Clの少なくとも一つであって、およそ107Ω-cmよりも大きい電気抵抗であることを特徴とする結晶構造を含むガリウムナイトライド。

(もっと読む)

炭化珪素結晶および炭化珪素結晶の製造方法

【課題】品質の低下を抑制できる、SiC結晶およびSiC結晶の製造方法を提供する。

【解決手段】SiC結晶10は、Feの濃度が0.1ppm以下であり、かつAlの濃度が100ppm以下であることを特徴とする。SiC結晶の製造方法は、以下の工程を備える。第1の原料として研磨用SiC粉末を準備する。第1の原料を加熱することにより昇華して、SiCの結晶を析出することにより、第1のSiC結晶を成長する。第1のSiC結晶を粉砕して、第2の原料を形成する。第2の原料を加熱することにより昇華して、SiCの結晶を析出することにより、第2のSiC結晶を成長する。

(もっと読む)

シリコン半導体ウェハ

【解決手段】界面で成長する単結晶をルツボ中に含まれる融液から引き上げる工程と、引き上げられた単結晶から半導体ウェハを切り分ける工程とを有するシリコン半導体ウェハの製造方法において、単結晶の引き上げの間に、界面の中心に熱を供給し、界面の中心から縁部までの比V/Gの半径方向プロフィールを、界面に対して垂直方向の温度勾配であるG及び融液から単結晶を引き上げる引き上げ速度であるVを用いて制御する。比V/Gの半径方向プロフィールを、界面に接する単結晶中の熱機械応力場の影響が内因性点欠陥の発生に関して補償するように制御する。

【効果】0.6mm/minの速度で引き上げた単結晶から、300mmの直径を有する無欠陥のシリコン半導体ウェハを高い歩留まりで得ることができた。この半導体ウェハに関して、Aスワール欠陥も、FPDも、OSF欠陥も検出できなかった。

(もっと読む)

酸化亜鉛系薄膜、酸化亜鉛系基板、及び酸化亜鉛系基板の処理方法

【課題】Zn極性面(+c面)を有する酸化亜鉛系基板中の不純物含有量を十分に低減できる酸化亜鉛系基板の処理方法、不純物含有量が十分に低減された酸化亜鉛結晶を含有する酸化亜鉛系薄膜、及び該薄膜の形成に好適な、不純物含有量が十分に低減された酸化亜鉛系基板の提供。

【解決手段】一般式「ZnxMg1−xO(式中、xは、0<x≦1を満たす数である。)」で表される組成を有する酸化亜鉛系基板の処理方法であって、前記基板の表面のうち、Zn極性面(+c面)をドライエッチングすることにより、化学的に安定な第一の不純物含有層を除去する工程と、前記ドライエッチング面をさらにウェットエッチングすることにより、前記第一の不純物含有層よりも深い位置にある第二の不純物含有層を除去する工程と、を有することを特徴とする酸化亜鉛系基板の処理方法。

(もっと読む)

シリコン単結晶の製造方法

【課題】 CZ法による無欠陥シリコン単結晶の製造方法において、双晶欠陥が抑制された良質なシリコン単結晶の製造方法を提供することを目的とする。

【解決手段】 CZ法によってチャンバ内でシリコン単結晶をシリコン融液から引上げて製造する方法において、双晶欠陥のない無欠陥結晶を得るために、前記シリコン単結晶の引き上げ速度Vと結晶温度勾配Gの比のV/G値を、格子間シリコンの凝集体として形成される転位クラスター領域と格子間シリコン優勢の無欠陥領域の境界V/G値より0.2〜0.5%大きい範囲で、かつ、OSF領域が出現するV/G値よりも小さい範囲内で制御し、前記シリコン単結晶を製造することを特徴とするシリコン単結晶の製造方法。

(もっと読む)

シリコンウェーハ及びその製造方法

【課題】板状酸素析出物を含むシリコンウェーハであってデバイスプロセスにてLSA処理を行った場合であっても転位の発生を防止することが可能なシリコンウェーハを提供する。

【解決手段】本発明によるシリコンウェーハは、LSA処理を含むデバイスプロセスに供せられるシリコンウェーハであって、LSA処理時においてシリコンウェーハに含まれる板状酸素析出物の対角線長をS(nm)、前記LSA処理における最高到達温度をT(℃)とした場合、T×S2≦9×106を満たす。本発明によれば、上記の条件でLSA処理を行うことにより、シリコンウェーハに含まれる板状酸素析出物を起点とした転位の発生を防止することが可能となる。

(もっと読む)

エピタキシャル炭化珪素単結晶基板の製造方法

【課題】炭化珪素単結晶基板に含まれる基底面転位がエピタキシャル膜に引き継がれるのを抑制して、高品質のエピタキシャル膜を成膜することができるエピタキシャル炭化珪素単結晶基板の製造方法を提供し、また、これにより得られたエピタキシャル炭化珪素単結晶基板を提供する。

【解決手段】化学気相堆積法によって、炭化珪素単結晶基板上に炭化珪素膜をエピタキシャル成長させる結晶成長工程において、エピタキシャル成長の主たる時間を占める結晶成長主工程での成長温度T1に対し、低い設定温度T0と高い設定温度T2との間で、成長温度を上下に変化させる温度切り替え操作を伴う結晶成長副工程を含むエピタキシャル炭化珪素単結晶基板の製造方法であり、また、この方法を用いて得られたエピタキシャル炭化珪素単結晶基板である。

(もっと読む)

炭化珪素単結晶ウェハの製造方法及びこの方法で得られた炭化珪素単結晶ウェハ

【課題】炭化珪素単結晶インゴットから切り出された直後のウェハに存在するそり・うねりをウェハの両面研磨の際に効果的に除去し、フリースタンディング状態でもそり・うねりの無い研磨後のウェハを調製し、これによって欠陥密度の少ない良好な品質のウェハを製造することができる炭化珪素単結晶ウェハの製造方法を提供する。また、平均積層欠陥密度が30cm-1以下である良品質の炭化珪素単結晶ウェハを提供する。

【解決手段】炭化珪素単結晶インゴットから切り出されたウェハ3を両面研磨装置のキャリア2内に保持させてウェハ表面を両面研磨し、次いで両面研磨後のウェハの表面に生成した加工変質層を除去して炭化珪素単結晶ウェハを製造するに際し、ウェハ厚さよりも厚さの大きいキャリアを用いてウェハの両面研磨を行う、炭化珪素単結晶ウェハの製造方法である。

(もっと読む)

炭化珪素基板

【課題】結晶方位を把握することができ、かつ容易に製造することができる炭化珪素基板を提供する。

【解決手段】第1の円形面11は、第1の形状を有する第1のノッチ部N1aが設けられている。第2の円形面21は、第1の円形面に対向し、かつ第2の形状を有する第2のノッチ部N2aが設けられている。側面31は第1の円形面11および第2の円形面21をつないでいる。第1のノッチ部N1aおよび第2のノッチ部N2aは互いに対向しており、側面31は第1のノッチ部N1aおよび第2のノッチ部N2aをつなぐ第1のへこみ部Daを有する。

(もっと読む)

炭化珪素単結晶ウェハ

【課題】ウェハの反り量が小さく、かつ、ウェハ面内の結晶方位が揃っており、デバイス作製用ウェハとして適用した場合に高いデバイス性能とデバイス歩留りを実現できるSiC単結晶ウェハの提供。

【解決手段】口径100mm以上の炭化珪素単結晶ウェハ12であって、ウェハ面内における高低差で表される反り量が、口径100mmのウェハ換算比(反り量/ウェハ口径)で60μm/100mm以下であり、かつ、ウェハ中心における<0001>結晶方位に対して、ウェハ直径上の4つの測定点a1,a2,a1’,a2’での<0001>結晶方位のずれが、いずれも±1000秒以内である炭化珪素単結晶ウェハである。4つの測定点は、全てウェハ12の直径L1上に存在し、このうち2点a1,a1’はウェハ外周からウェハ中心に向かって2mm内側の位置、残りの2点a2,a2’は前記外周部の2点a1,a1’と中心a0とを結んだ線分の中点に位置する。

(もっと読む)

エピタキシャルウェーハの製造方法、エピタキシャルウェーハ及び撮像用デバイスの製造方法

【課題】欠陥のほとんどないシリコンエピタキシャル層を形成できるエピタキシャルウェーハの製造方法、当該方法により製造されたエピタキシャルウェーハ及び撮像用デバイスの製造方法を提供することを目的とする

【解決手段】前記シリコン基板に急速熱処理を施すことによって、少なくとも前記シリコン基板の表面から0.5μmの深さまでの領域に存在するRIE法により検出される欠陥を消滅させるRIE欠陥消滅工程と、前記RIE法により検出される欠陥を消滅させたシリコン基板の表面上に前記シリコンエピタキシャル層を形成する工程とを具備するエピタキシャルウェーハの製造方法。

(もっと読む)

GaAs結晶基板

【課題】比抵抗が1×108Ω・cm〜8×108Ω・cmのような高い比抵抗を有し、結晶主面に平行な面内における比抵抗値および/またはキャリア移動度のばらつきが低減されたGaAs結晶基板を提供する。

【解決手段】本GaAs結晶基板は、比抵抗が1×108Ω・cm〜8×108Ω・cmかつ炭素濃度が5×1015cm-3〜1×1016cm-3のGaAs結晶をスライスして得られた、結晶主面に平行な面内における比抵抗のばらつきが10%未満である。

(もっと読む)

導電性III族窒化物単結晶基板の製造方法

【課題】所望の比抵抗を有する導電性III族窒化物単結晶基板を低コストで製造することができる導電性III族窒化物単結晶基板の製造方法を提供する。

【解決手段】導電性III族窒化物単結晶基板の製造方法は、GaClガス、NH3ガス、及びN2又はArにより所定の濃度に希釈されたSiH2Cl2ガスをGaN単結晶基板に供給し、450μm/hourより大きく2mm/hour以下の範囲の成長速度でGaN単結晶基板上にGaN単結晶を成長させると共に、SiH2Cl2ガスが所定の濃度に希釈されたことによるNH3ガスとの反応の抑制により、GaN単結晶の比抵抗が1×10−3Ωcm以上1×10−2Ωcm以下となるようにSiH2Cl2ガスに含まれるSiがGaN単結晶にドーピングされることを含む。

(もっと読む)

III族窒化物半導体結晶の製造方法

【課題】Naフラックス法によるGaN結晶の製造方法において、GaN結晶にインクルージョンが発生せず、かつ転位密度を減少させること。

【解決手段】種結晶18として、GaNからなる自立基板を用い、種結晶18上に7μm/h以下の成長速度でGaN結晶100を成長させた。GaN結晶100はステップフロー成長し、種結晶18から伝搬する転位はGaN結晶100中において曲げられ、転位密度が減少する。その後、GaN結晶100上に7μm/hよりも速く、25μm/hよりも遅い成長速度でGaN結晶102を成長させた。

(もっと読む)

多結晶シリコンインゴットの製造方法及び多結晶シリコンインゴット

【課題】(001)、(111)方位を向く結晶が多く存在し、かつ、底部における酸素濃度が高い部分が少なく、生産歩留まりを大幅に向上させることができる多結晶シリコンインゴット、及び、その製造方法を提供する。

【解決手段】シリコン融液を底面から上方に向けて一方向凝固させる多結晶シリコンインゴットの製造方法であって、ルツボ20の底面にはシリカ多層コーティング層27が配設されており、前記ルツボ20内における凝固過程を、前記ルツボ20の底面を基準として、0mmから高さX(10mm≦X<30mm)までの第1領域A1と、高さXから高さY(30mm≦Y<100mm)までの第2領域A2と、高さY以上の第3領域A3と、に区分けし、前記第1領域A1における凝固速度V1が、10mm/h≦V1≦20mm/hの範囲内に設定され、前記第2領域A2における凝固速度V2が、1mm/h≦V2≦5mm/hの範囲内に設定される。

(もっと読む)

窒化物半導体エピタキシャルウェハおよびその製造方法ならびに電界効果型トランジスタ素子

【課題】 高耐圧化とカレントコラプス現象の低減ないしは解消との両立を可能とした窒化物半導体エピタキシャルウェハおよびその製造方法ならびに電界効果型トランジスタ素子を提供する。

【解決手段】 基板1と、前記基板1の上に形成された第1の窒化物半導体層3と、前記第1の窒化物半導体層3の上に形成された、前記第1の窒化物半導体層3よりも電子親和力の小さい第2の窒化物半導体層5とを有し、前記第1の窒化物半導体層3には、その表面から深さ方向に、近似式;NFe=A×exp(B×C)、(NFe:第1の窒化物半導体層における鉄濃度、A:1E14〜1E17[cm−3]、B:3〜8[μm−1]、C:第1の窒化物半導体層における表面からの深さ)によって表わされる深さ方向プロファイルで鉄がドーピングされており、かつ前記第1の窒化物半導体層の表面側には、前記鉄の濃度よりも高い濃度でシリコンをドーピングしてなるシリコンドーピング領域4が設けられている。

(もっと読む)

141 - 160 / 795

[ Back to top ]