Fターム[4G077EE01]の内容

結晶、結晶のための後処理 (61,211) | 結晶成長共通−成長前の基板の処理、保護 (913) | 基板の表面処理 (858)

Fターム[4G077EE01]の下位に属するFターム

清浄化、エッチング (229)

結晶核の形成 (118)

被膜の形成(例;保護膜) (381)

基板へのドーピング (28)

Fターム[4G077EE01]に分類される特許

21 - 40 / 102

大領域窒化物結晶およびその作製方法

【課題】大領域のガリウム含有窒化物結晶の成長のための方法を提供する。

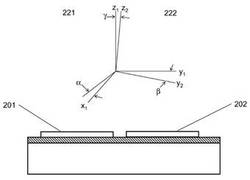

【解決手段】転位密度が約107cm−2よりも低い少なくとも2つの結晶201、202を提供する工程と、ハンドル基板を提供する工程と、少なくとも2つの結晶201、202をハンドル基板に対してウェーハ接合する工程と、少なくとも2つの結晶201,202を成長させて、溶合結晶として合体させる工程と、を含み、第1の結晶201と第2の結晶202との間の極性配向不整角度γは、0.5度未満であり、方位配向不整角度αおよびβは1度未満である。

(もっと読む)

ホモエピタキシャルIII−V族窒化物品、デバイス、およびIII−V族窒化物ホモエピタキシャル層を形成する方法

【課題】LEDや高電子移動度トランジスタなどのデバイス用として有用なIII−V族窒化物品の提供。

【解決手段】自立III−V族窒化物基板上に堆積したIII−V族窒化物ホモエピタキシャル層を含むホモエピタキシャルIII−V族窒化物品であって、前記III−V族窒化物ホモエピタキシャル層が1E6/cm2未満の転位密度を有しており、(i)前記III−V族窒化物ホモエピタキシャル層と前記自立III−V族窒化物基板の間に酸化物を有するか、(ii)前記III−V族窒化物ホモエピタキシャル層と前記自立III−V族窒化物基板の間にエピ中間層を有するか、

(iii)前記自立III−V族窒化物基板がオフカットされており、前記III−V族窒化物ホモエピタキシャル層が非(0001)ホモエピタキシャルステップフロー成長結晶を含むことを特徴とする。

(もっと読む)

エピタキシャルウェーハの製造方法、エピタキシャルウェーハ及び撮像用デバイスの製造方法

【課題】欠陥のほとんどないシリコンエピタキシャル層を形成できるエピタキシャルウェーハの製造方法、当該方法により製造されたエピタキシャルウェーハ及び撮像用デバイスの製造方法を提供することを目的とする

【解決手段】前記シリコン基板に急速熱処理を施すことによって、少なくとも前記シリコン基板の表面から0.5μmの深さまでの領域に存在するRIE法により検出される欠陥を消滅させるRIE欠陥消滅工程と、前記RIE法により検出される欠陥を消滅させたシリコン基板の表面上に前記シリコンエピタキシャル層を形成する工程とを具備するエピタキシャルウェーハの製造方法。

(もっと読む)

グラフェン膜のエピタキシャル成長方法

【課題】大規模、均一かつ高品質のグラフェン膜およびその作成方法を提供する。

【解決手段】結晶質基板100上に触媒薄膜101を形成し、この触媒薄膜を加熱処理して高秩序で選択的に配向した結晶質触媒薄膜を形成し、ガス状炭素源を加熱し触媒薄膜を冷却することで、触媒薄膜上にグラフェン膜102が形成される。前記触媒薄膜の触媒材料はNi、Pt、Co、Fe、Al、Cr、Cu、Mg、Mn、Rh、Ti、Pd、Ru、Ir及びReからなる群から選択された1つまたは複数の元素を含み、厚さは約1nmから約2mmの範囲である。

(もっと読む)

炭化珪素基板の製造方法

【課題】製造工程を簡略化すると共に、表層部にらせん転位が存在することを抑制することができるSiC基板の製造方法を提供する。

【解決手段】炭化珪素からなり、主表面および当該主表面の反対面である裏面を備え、らせん転位1を表層部2aに含む欠陥含有基板2を用意する工程と、欠陥含有基板2のうち主表面に外力を印加することにより表層部2aの結晶性を低下させる第1外力印加工程と、外力印加工程の後、欠陥含有基板2を熱処理することにより表層部2aの結晶性を回復させる第1熱処理工程と、を含む製造方法とする。

(もっと読む)

GaN結晶基板

【課題】GaN結晶基板上に成長させる半導体層のモフォロジーを低下させることなく、基板の結晶方位を識別することができるGaN結晶基板を提供する。

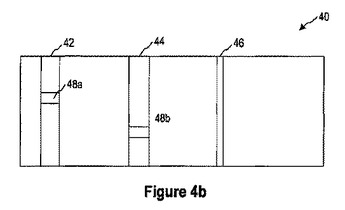

【解決手段】本GaN結晶基板は、マトリックス結晶領域11と、マトリックス結晶領域11の結晶に対して少なくとも1つの結晶軸が異なる結晶を含有する異方位結晶領域13とを含み、異方位結晶領域13の形状は、任意に特定される結晶方位を示すように形成されている。

(もっと読む)

SiCエピタキシャルウェハ及びその製造方法

【課題】三角欠陥及び積層欠陥が低減され、キャリア濃度及び膜厚の均一性が高く、ステップバンチングフリーのSiCエピタキシャルウェハ及びその製造方法を提供する。

【解決手段】0.4°〜5°のオフ角で傾斜させた4H−SiC単結晶基板上にSiCエピタキシャル層を形成したSiCエピタキシャルウェハの製造方法であって、ガスエッチングによって表面を清浄化した前記基板上に、炭化珪素のエピタキシャル成長に必要とされる量の炭素と珪素の原子数比C/Siが0.7〜1.2となるように珪素含有ガス及び炭素含有ガスを供給して、1600℃より高くかつ1800℃以下の温度で炭化珪素膜をエピタキシャル成長させる。これにより、前記SiCエピタキシャル層の表面の三角形状の欠陥密度が1個/cm2以下となる。

(もっと読む)

100ミリメートル高純度半絶縁単結晶炭化珪素ウエハ

【課題】炭化珪素の高品質の単結晶を生成する。

【解決手段】シード結晶とシード・ホルダとの距離を、シード結晶とシード・ホルダとの間の伝導性熱転移が、シード・ホルダに隣接するシード結晶の表面全体に渡って、これらの間の放射性熱転移よりも大きくなるまで、減少させる。特に、シード結晶及びシード・ホルダが直接接触するときに良好な結果が得られ、接触面は常に10μm以下、好ましくは1μm未満である。このような関係を得るために、シード・ホルダ25に固定されているエッジ・リング・シード・キャップ27にシード結晶24を支持している。成長する結晶26もキャップに支持される。

(もっと読む)

p型ZnOナノ構造体および該p型ZnOナノ構造体を備えてなる紫外線センサならびにp型ZnOナノ構造体の製造方法

【課題】結晶性に優れ、基板に対して配向成長したp型ZnOナノ構造体及びその製造方法を提供する。

【解決手段】圧力及び温度が制御された反応容器の内部に配置されたP(リン)を含有するZnOターゲットにレーザー光を照射し、レーザーアブレーションにより生成した微粒子に由来する微結晶を核としてサファイア単結晶基板表面のc面に配向成長したリンを含有するp型ZnOナノ構造体が形成される。特に圧力及び温度を適宜選択することにより、p型ZnOナノ構造体として、p型ZnOナノワイヤやp型ZnOナノシートを形成することができる。該ZnOナノ構造体は、紫外線センサなどの半導体デバイスとして好適に使用できる。

(もっと読む)

発光素子の製造方法

【課題】半導体基板の製造方法及び発光素子の製造方法を開示する。

【解決手段】本発明の一実施形態によると、半導体基板の製造方法は、基板の上に第1の半導体層を形成し、第1の半導体層の上にパターン状に金属性材料層を形成し、第1の半導体層の上及び金属性材料層の上に第2の半導体層を形成するとともに、金属性材料層より下層部分の第1の半導体層に空洞を形成し、空洞を用いて第2の半導体層から基板を剥離することを含む。これによって、レーザを使用して成長基板を分離する必要がないので、基板製造コストを減少させることができる。

(もっと読む)

制御された量子ドット成長

本開示は、概して、制御された量子ドットを成長させる技法、および量子ドットの構造に関する。いくつかの例では、基板を用意することと、基板上に欠陥を形成することと、基板上に層を堆積することと、欠陥に沿って量子ドットを形成することとのうちの1つまたは複数を含む方法が記載されている。  (もっと読む)

(もっと読む)

エピタキシャルウェハの製造方法、欠陥除去方法およびエピタキシャルウェハ

【課題】膜厚分布が均一なエピタキシャル膜を有するとともに、平坦度に優れたエピタキシャルウェハを簡単な工程で製造することのできるエピタキシャルウェハの製造方法およびエピタキシャルウェハを提供すること。

【解決手段】CZ法により得られたシリコン単結晶インゴットを薄円板状に切り出してウェハを得る(ステップS1)。次に、ウェハの表面を研削(ラッピング)して平面化する(ステップS2)。次に、エッチングによる化学研磨を行った(ステップS3)後、ウェハの両面を粗研磨する(ステップS4)。粗研磨終了後、気相エッチングを行い(ステップS5)、その後、エピタキシャル膜を形成する(ステップS6)。そして、エピタキシャル膜が形成されたウェハに対して仕上げ研磨を行い(ステップS7)、最終洗浄を行った(ステップS8)後、終了する。

(もっと読む)

半導体結晶の成長方法及び光半導体素子

【課題】

光学的特性に優れたZnO系結晶を提供する。

【解決手段】

(0001)(+C面)を主面とするZnO単結晶基板を準備し、熱処理する工程と、 加熱した前記主面上にII−VI族半導体結晶をII族原子の極性面で成長する工程と、を含み、前記熱処理する温度は、前記II−VI族の半導体結晶の成長工程における結晶成長温度よりも高い温度である半導体結晶の成長方法。

(もっと読む)

酸化物薄膜の成膜装置および成膜方法

【課題】酸化物薄膜の形成の直前に配向金属基板を還元雰囲気下で熱処理を行うに際して、必要以上に熱処理時間を長くしてコストアップを招くことがなく、また、必要以上に熱処理温度を高くして品質の低下を招くことがない酸化物薄膜の成膜装置およびこのような装置を用いた酸化物薄膜の成膜方法を提供する。

【解決手段】長尺の配向金属基板の表面の酸化層を除去する還元熱処理室の直後に、還元熱処理室より搬送された配向金属基板の表面に酸化物薄膜を成膜する成膜室を備えた酸化物薄膜の成膜装置であって、還元熱処理室と成膜室との間に、還元熱処理室および成膜室の互いの雰囲気を実質的に独立した雰囲気とする雰囲気遮断部が設けられ、さらに、還元熱処理室および成膜室のそれぞれにガス供給機構および排気機構が設けられている酸化物薄膜の成膜装置とそれを用いた成膜方法。

(もっと読む)

エピタキシャル成長用内部改質基板及びそれを用いて作製される結晶成膜体、デバイス、バルク基板及びそれらの製造方法

【課題】窒化物半導体層のエピタキシャル成長に用いるサファイア基板において、効率良く基板の反り形状及び/又は反り量を精密に制御することができ、且つ、成膜中に生じる基板の反りを抑制、それを用いて作製される窒化物半導体層成膜体、窒化物半導体デバイス、窒化物半導体バルク基板及びそれらの製造方法を提供する。

【解決手段】サファイア基板の内部に、前記サファイア基板の研磨面側を通してパルスレーザを集光し、走査し、前記パルスレーザによる多光子吸収を利用して改質領域パターンを形成し、サファイア基板の反り形状及び/又は反り量を制御する。本発明により得られたサファイア基板を用いて窒化物半導体層を形成すると、成膜中の基板の反りを抑制し、基板の反り挙動を小さくすることができるため、膜の品質及び均一性が向上し、窒化物半導体デバイスの品質及び歩留まりを向上させることができる。

(もっと読む)

化合物半導体基板及びその製造方法、並びに、半導体デバイス及びその製造方法

【課題】エピタキシャル層と基板との界面における電気抵抗の低減がはかられた化合物半導体基板及びその製造方法を提供する。

【解決手段】化合物半導体基板10は、III族窒化物で構成され、化合物半導体基板10の表面の表面層12に、Cl換算で200×1010個/cm2以上12000×1010個/cm2以下の塩化物及びO換算で3.0at%以上15.0at%以下の酸化物が含まれるときに、化合物半導体基板10とその上に形成されるエピタキシャル層14との間の界面のSiが低減され、その結果界面における電気抵抗が低減される。

(もっと読む)

エピタキシャルシリコンウェーハとその製造方法

【課題】シリコン結晶育成時にリンのような電気抵抗率降下用ドーパントとゲルマニウムが一緒に高濃度にドープされた低電気抵抗率のシリコン結晶基板をベースにしたエピタキシャルシリコンウェーハにおいて、ミスフィット転位とスタッキングフォルト(SF)の双方を抑制する。

【解決手段】シリコン結晶育成時に例えばリンとゲルマニウムが一緒に高濃度ドープされたシリコン結晶基板上に、シリコンエピタキシャル層をCVD法で成長させるプロセスにおいて、そのプロセス温度を1000〜1090℃の範囲内(より望ましくは、1050〜1080℃)の範囲内にする。これにより、SFに起因してエピタキシャルシリコンウェーハの表面に生じるLPD(SFに起因して生じる)の個数が大幅に減る。

(もっと読む)

半導体構造物の製造方法

【課題】シリコン基板に代表されるIV族半導体上に、基板面に対して垂直に延びる半導体ナノワイヤを配置すること。

【解決手段】(111)面を有するIV族半導体基板と、前記(111)面を被覆し、開口部を有する絶縁膜とを含む基板を準備し;前記基板を低温熱処理して、前記(111)面を、(111)1×1面とし;前記基板に低温条件下で、III族原料またはV族原料を供給して、前記(111)面を、(111)A面または(111)B面に変換し;前記IV族半導体基板の(111)面から前記開口部を通して、III−V化合物半導体ナノワイヤを成長させる。IV族半導体基板とは、シリコン基板やゲルマニウム基板であったりする。

(もっと読む)

ハイドライド気相成長法(HVPE)による平坦な非極性{1−100}m面及び半極性{11−22}窒化ガリウムの成長

ハイドライド気相成長法(HVPE)を使用してIII族窒化物材料をm面サファイア基板などの適当な基板上で成長させる、(11−22)又は(10−13)窒化ガリウム(GaN)エピタキシャル層などの半極性III族窒化物材料を成長させる方法を提供する。この方法は、基板をアンモニア及びアルゴンの環境内で上昇温度でインサイチュ前処理し、窒化アルミニウム(AlN)又は窒化アルミニウムガリウム(AlGaN)などの中間層を焼鈍基板上で成長させ、HVPEを使用してIII族窒化物エピタキシャル層を中間層上で成長させることを含む。 (もっと読む)

単結晶ダイヤモンドの表面損傷の除去方法

【課題】単結晶ダイヤモンド基板の表面損傷を除去するために有効な新規な方法および表面損傷が除去された単結晶タイヤモンドを基板としたCVD法による単結晶ダイヤモンドの製造方法を提供する。

【解決手段】単結晶ダイヤモンドにイオン注入を行って表面近傍に非ダイヤモンド層を形成し、該非ダイヤモンド層をグラファイト化させた後、エッチングして表面層を除去する。この様にして得られた単結晶ダイヤモンドは、表面粗さを増加させることなく、切断、研磨などによって生じた表面損傷部がほぼ完全に除去され、また、表面と交差する転位もほとんど存在しないものとなるので、処理された単結晶ダイヤモンドを基板として、CVD法によってダイヤモンドを成長させることによって、転位の伝播や新たな転位の発生を著しく抑制することができ、形成される単結晶ダイヤモンドの結晶性を著しく改善することができる。

(もっと読む)

21 - 40 / 102

[ Back to top ]