Fターム[4G077EF03]の内容

結晶、結晶のための後処理 (61,211) | 結晶成長共通−基板への多層成長 (667) | 基板に膜を多層に形成するもの (667) | バッファ層の形成(格子整合のための) (495) | バッファ層が成長結晶の成分元素を含むもの (367)

Fターム[4G077EF03]に分類される特許

41 - 60 / 367

III族窒化物単結晶の製造方法およびこれに用いる種結晶基板

【課題】結晶品質の良いIII族窒化物単結晶を得ると共に、その基板からの自然剥離を促進することで、クラックを更に低減することである。

【解決手段】基板1と、基板1上に形成されたIII族窒化物からなるバッファ層2およびこのバッファ層2上に形成されたIII族窒化物単結晶からなる種結晶膜3を備える複数の育成部9とを備えており、隣り合う複数の育成部9の間に基板1の表面1bが露出している育成用部材7を使用する。育成用部材7をウエットエッチングに供することによってバッファ層2を育成部9の端面からエッチングし、次いでIII族窒化物単結晶を種結晶膜3上にフラックス法によって育成する。

(もっと読む)

III族窒化物結晶の製造方法、III族窒化物テンプレートの製造方法、III族窒化物結晶及びIII族窒化物テンプレート

【課題】石英製の反応炉の損傷を抑制することができ、副生成物の生成を抑制できるIII族窒化物結晶の製造方法、III族窒化物テンプレートの製造方法、III族窒化物結晶及びIII族窒化物テンプレートを提供する。

【解決手段】本発明に係るIII族窒化物結晶は、III族窒化物結晶中に1×1016cm−3以上1×1020cm−3未満の炭素を含み、前記炭素がV族サイトを置換しており、かつ、前記III族窒化物結晶内でアクセプタとして働く他の不純物を含まないものである。

(もっと読む)

III族窒化物半導体素子製造用基板およびIII族窒化物半導体自立基板またはIII族窒化物半導体素子の製造方法ならびにIII族窒化物成長用基板

【課題】結晶層の結晶性や均一性を向上させることができるIII族窒化物半導体素子製造用基板の製造方法を提供する。

【解決手段】成長用下地基板10上に、クロム層20を形成する成膜工程と、該クロム層20を、所定の条件で窒化することによりクロム窒化物層30とする窒化工程と、該クロム窒化物層30上に、バッファ層40を介して、少なくとも1層のIII族窒化物半導体層50をエピタキシャル成長させる結晶層成長工程とを具えるIII族窒化物半導体素子製造用基板90の製造方法であって、前記クロム層20は、スパッタリング法により、スパッタリング粒子飛程領域における成膜速度が7〜65Å/秒の範囲で、厚さが50〜300Åの範囲となるよう成膜され、前記クロム窒化物層30は、炉内圧力6.666kPa以上66.66kPa以下の、温度1000℃以上のMOCVD成長炉内において、アンモニアガスを含むガス雰囲気中で形成される。

(もっと読む)

窒化ガリウム系化合物半導体基板とその製造方法

【課題】転位発生の防止と基板の反り低減を、中間層を構成する窒化物半導体層の積層数を少なくして実現できる窒化ガリウム系化合物半導体基板を提供する。

【解決手段】Si単結晶からなる基板1と、前記基板上に形成された窒化物半導体からなる中間層2と、前記中間層上に形成された窒化ガリウム系化合物半導体3からなる活性層で構成される窒化ガリウム系化合物半導体基板であって、前記中間層は、前記基板上に第一層21と第二層22がこの順で積層された初期バッファ層200と、前記初期バッファ層上に第三層23と第四層24をこの順で複数回繰り返し積層し最後に第五層25を積層してなる複合層202を複数積層した周期堆積層203からなる。

(もっと読む)

窒化物半導体結晶層の製造方法

【課題】より良質な窒化物半導体結晶層を製造する方法を提供する。

【解決手段】実施形態によれば、窒化物半導体結晶層の製造方法は、基体の上に設けられたシリコン結晶層の上に、第1の厚さを有する窒化物半導体結晶層を形成する工程を備える。前記シリコン結晶層は、前記窒化物半導体結晶層の形成の前には、前記第1の厚さよりも薄い第2の厚さを有している。前記窒化物半導体結晶層の形成は、前記シリコン結晶層の少なくとも一部を前記窒化物半導体結晶層に取り込ませ、前記シリコン結晶層の厚さを前記第2の厚さから減少せることを含む。

(もっと読む)

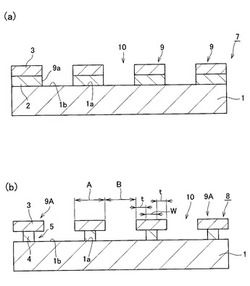

窒化物半導体基板の製造方法

【課題】下地基板の表面品質を均一にし、窒化物厚膜成長の歩留と品質の向上を実現することができる窒化物半導体基板の製造方法を提供する。

【解決手段】半導体デバイスのエピタキシャル成長に用いる窒化物半導体基板の製造方法において、基材1上に窒化物半導体からなる第1の層2が設けられた下地基板10上に金属膜層(若しくは炭化膜層)3を形成し、金属膜層(若しくは炭化膜層)3を窒化した後、表面酸化処理を施し、窒化物半導体からなる第2の層5を成長させ、しかる後、基材1から第2の層5を剥離して窒化物半導体基板40を製造する方法である。

(もっと読む)

窒化物半導体ウェハ及びその製造方法

【課題】マーキングにかかる時間を短縮でき、かつ下地基板の製造履歴を簡便に追跡できる識別符号を有する自立した窒化物半導体ウェハを提供する。

【解決手段】識別符号12が付された下地基板11上に窒化物半導体層13を成長させ、その窒化物半導体層13を下地基板11から分離して得られる自立した窒化物半導体ウェハにおいて、窒化物半導体層13は、その成長時に識別符号11が転写された転写識別符号16を有する窒化物半導体ウェハである。

(もっと読む)

独立(Al、Ga、In)Nおよびそれを形成するための分割方法

【課題】非常に優れた形態的特徴を有し、例えばマイクロエレクトロニクスおよび/またはオプトエレクトロニクスデバイスおよびデバイス前駆体構造体を製作するための基板として使用される(Al、Ga、In)N物品の製造方法を提供する。

【解決手段】エピタキシャルに適合できる犠牲型板12を設けるステップと、単結晶(Al、Ga、In)N材料16を型板12上に堆積して、犠牲型板12と(Al、Ga、In)N材料16との間の界面14を含む複合犠牲型板/(Al、Ga、In)N物品10を形成するステップと、複合犠牲型板/(Al、Ga、In)N物品10を界面修正して、犠牲型板12を(Al、Ga、In)N材料16から分割し、独立(Al、Ga、In)N物品10を生じるステップにより、独立(Al、Ga、In)N物品を製造する。

(もっと読む)

化合物半導体基板

【課題】Si単結晶基板を用いた化合物半導体基板において、化合物半導体基板の機械強度低下と熱伝導率低下を、Si単結晶基板のドーパント濃度制御で低減する。

【解決手段】Si単結晶基板上に中間層とデバイス活性層を備えた化合物半導体基板で、Si単結晶基板は、中間層側の一主面の表面から厚さ方向に向かってドーパント濃度が1×1019atoms/cm3以上1×1021atoms/cm3以下である領域1と、ドーパント濃度が連続的に減少する遷移領域1と、ドーパント濃度が1×1012atoms/cm3以上5×1017atoms/cm3以下である領域2と、ドーパント濃度が連続的に増加する遷移領域2と、ドーパント濃度が1×1019atoms/cm3以上1×1021atoms/cm3以下である領域3とからなる。

(もっと読む)

半導体積層構造および電界効果トランジスター

【課題】ダイヤモンド基板上に、クラックが抑制され、かつ膜厚が厚い単結晶窒化物層を有する半導体積層構造を提供すること。

【解決手段】ダイヤモンド基板上に直接成長した窒化物層が多結晶となる上記課題を解決するため、本発明に係る半導体積層構造は、ダイヤモンド基板と、ダイヤモンド基板上の、Siを含む第1の層と、第1の層上の、単結晶窒化物で構成される第2の層とを備える。Siを含む第1の層をダイヤモンド基板と第2の層との間に設けることにより、第2の層の膜厚を大きくしても、第2の層を構成する窒化物を、クラックの抑制された単結晶とすることができる。したがって、当該半導体積層構造を利用することで、高いドレイン電流および出力電力密度を有する電界効果トランジスターを実現することが可能である。

(もっと読む)

立方晶炭化珪素膜の製造方法

【課題】結晶欠陥が少なく、かつ平坦性に優れた高品質の立方晶炭化珪素膜を容易に得ることができる立方晶炭化珪素膜の製造方法を提供する。

【解決手段】Si基板1の表面を炭化させて下地層2を形成し、次いで、Si基板1の下地層2上に原料ガスg2を供給しつつ、この原料ガス雰囲気にて立方晶炭化珪素層3をエピタキシャル成長させ、次いで、この立方晶炭化珪素層3の表面3aをクリーニングして異物を除去し、次いで、この立方晶炭化珪素層3上に再度、原料ガスg2を供給しつつ、この原料ガス雰囲気にて立方晶炭化珪素層4をエピタキシャル成長させる。

(もっと読む)

GaN結晶の成長方法

【課題】HVPE法において、1100℃以下の結晶成長温度で、大型のGaN結晶を成長させる方法を提供する。

【解決手段】所定の面方位の主表面1mおよび複数の側表面1sを有するGaN種結晶基板1を複数準備する工程と、複数のGaN種結晶基板1を、それらの主表面1mが互いに平行にかつそれらの側表面1sが互いに隣り合うように配置する工程と、配置された複数のGaN種結晶基板1の主表面1m上に、ハイドライド気相成長法により、第1のGaN結晶10を成長させる工程と、を備え、第1のGaN結晶10を成長させる工程において、結晶成長温度を980℃以上1100℃以下とすることにより、GaN種結晶基板1の主表面1m上に成長するそれぞれの部分結晶10uが一体化するように成長させる。

(もっと読む)

半導体発光素子の製造方法、半導体発光素子及びサファイア単結晶基板

【課題】直径100mm以上の大口径であっても結晶欠陥部分が少なく、化合物半導体層のエピタキシャル形成に適した高品質かつ低コストのサファイア単結晶基板、および、かかる基板上に化合物半導体層を成膜した高品質の半導体発光素子を安定的に提供する。

【解決手段】III族化合物半導体層を有する半導体発光素子の製造方法であって、サファイア単結晶のインゴットからウエーハを切り出す基板切り出し工程S200と、切り出したウエーハについてラング法によるX線トポグラフィ測定を行い、(11−20)面のX線回折像が得られるX線の入射角度ωに対し、±0.15°の範囲内を判断基準とする湾曲補正値Δωにより補正したX線によりX線回折像が得られる結晶欠陥部分を含むウエーハを選別する選別工程S500と、選別されたウエーハの被成膜面上にIII族化合物半導体層を成膜する半導体層成膜工程S800と、を有する。

(もっと読む)

結晶成長方法および半導体素子

【課題】転位およびクラックの発生、並びに、基板の反りを抑制することが可能な結晶成長方法を提供する。

【解決手段】このIII族窒化物半導体の結晶成長方法は、シリコン基板100を加熱する工程と、加熱されたシリコン基板100に対して、少なくともTMA(トリメチルアルミニウム)を含むガスを先出し供給することにより、基板表面に凹状構造105を形成する工程とを備えている。

(もっと読む)

窒化物半導体基板の製造方法

【課題】オフ角ばらつきの小さい、窒化物半導体基板を製造することができる窒化物半導体基板の製造方法を提供する。

【解決手段】サファイア基板(1)上に窒化物半導体層(2)を形成し、前記サファイア基板(1)から分離した前記窒化物半導体層(2)を用いて自立した窒化物半導体基板(3)を作製する窒化物半導体基板の製造方法において、分離された前記窒化物半導体層(2)の表裏面の欠陥密度差に起因する反りによる前記窒化物半導体層(2)のC軸の半径方向内方への傾きを相殺するように、予め前記サファイア基板(1)表面のC軸には半径方向外方に傾きを持たせた。

(もっと読む)

半導体基板および半導体装置

【課題】反りの小さな半導体基板および半導体装置を提供する。

【解決手段】Si基板10上に接して形成されたX線回折による(002)面のロッキングカーブ半値幅が1500秒以下のAlN層12と、AlN層12上に形成されたGaN系半導体層14と、を具備する半導体基板であって、その反りの曲率半径は±25m以上であり、反り量は、半導体基板の大きさを4インチとした場合、±50μm以下である。GaN系半導体層14はAlN層12から圧縮応力を受ける。

(もっと読む)

半導体装置

【課題】GaN系半導体層のグレインサイズを大型化することが可能な半導体装置を提供すること。

【解決手段】本発明は、(111)面から0.1度以下のオフ角度で傾斜した面を主面とするSi基板10と、Si基板10の主面に接して設けられ、(002)面のX線回折におけるロッキングカーブの半値幅が2000sec以下であるAlN層12と、AlN層12上に設けられたGaN系半導体層20と、を備える半導体装置100である。

(もっと読む)

窒化物半導体結晶構造及び窒化物半導体自立基板の製造方法

【課題】結晶を複数片に分離する際の断面の歪の導入を低減し、窒化物半導体結晶の利用効率を上げることが可能な窒化物半導体結晶構造及び窒化物半導体自立基板の製造方法を提供する。

【解決手段】窒化物半導体結晶10から板状の結晶片を分離し、分離した前記板状の結晶片から窒化物半導体自立基板を作製するための窒化物半導体結晶構造において、レーザー光の照射による加熱分解で前記板状の結晶片に分離すべく、前記窒化物半導体結晶10内に、該窒化物半導体結晶10の成長時にバンドギャップの異なる組成の光吸収層2を単層または複数層形成したものである。

(もっと読む)

III族窒化物半導体成長用の下地基板およびIII族窒化物半導体の成長方法

【課題】表面状態や断面形状が良好なIII族窒化物半導体の厚膜結晶を成長させることができる下地基板を提供する。

【解決手段】第1結晶成長面と前記第1結晶成長面と同じ方向に面している第2結晶成長面を有する下地基板であって、前記第1結晶成長面の周縁の50%以上に下向きの段差を介して前記第2結晶成長面が連接しており、前記段差の高さが0.1〜5mmである。

(もっと読む)

ナノドットを有する構造体

【課題】電磁波(フォトン)と表面プラズモンおよび表面マグノンとの間でのエネルギ交換を効率よく、かつ高い頻度で行うことができ、表面プラズモン共振や表面マグノン共振によって吸収、蓄積されるフォトンのエネルギを多くすることができるナノドットを有する構造体を提供する。

【解決手段】支持体10と、支持体10の上に形成された、複数の導電性セラミクスの単結晶22が集合してなる導電性セラミクス層20とを有し、導電性セラミクス層20の表面には、導電性セラミクスの単結晶22の一部からなり、高さ方向に直交する断面の面積が底部から頂部に向かってしだいに減少する形状を有するナノドット24が複数形成された、ナノドットを有する構造体1。

(もっと読む)

41 - 60 / 367

[ Back to top ]