Fターム[4K029AA06]の内容

Fターム[4K029AA06]に分類される特許

21 - 40 / 1,129

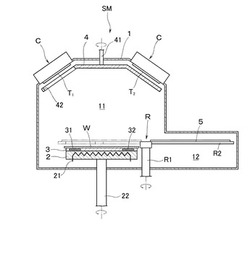

多元スパッタリング装置

【課題】静電チャックの基板吸着面にパーティクルが付着することを抑制できるようにした多元スパッタリング装置を提供する。

【解決手段】本発明の多元スパッタリング装置SMは、真空チャンバ1と、この真空チャンバの底部に配置され、上面に基板Wを吸着する静電チャック3を有するステージ2と、この真空チャンバの上部に、静電チャックで吸着された基板に対してスパッタ粒子を斜入射させるように配置された少なくとも2個のスパッタリングカソードCと、各スパッタリングカソードと基板との間を選択的に遮蔽する遮蔽手段4とを備える。静電チャックの上面が露出している場合に、当該静電チャックの上面を選択的に覆う保護板5を更に備える。

(もっと読む)

ミラー駆動装置及びその駆動方法並びに製造方法

【課題】圧電アクチュエータの力を効率よく利用してミラーの回転方向に大きな変位を得るとともに、垂直方向の並進運動を大幅に抑制する。

【解決手段】ミラー部(12)を挟んで両側に一対の圧電アクチュエータ部(14)が配置される。圧電アクチュエータ部(14)の一端(14A)は連結部(16)を介してミラー部(12)の端部(12A)に接続され、圧電アクチュエータ部(14)の他端(14B)は固定部(30)に固定支持される。また、ミラー部(12)は、垂直方向への並進運動する抑制する垂直移動抑制構造(32)を介して固定部(30)に接続されている。回転軸(18)付近に接続されるトーションバー(20)とトーションバー(20)の基端部を支持するトーションバー支持部(22)とにより垂直移動抑制構造(32)を構成できる。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】金属カルコゲナイド膜の積層体を有する相変化メモリにおいて、読み書き動作の速度を高めることのできる相変化メモリの形成装置、及び相変化メモリの形成方法を提供する。

【解決手段】GeTe膜とSbTe膜とを基板上にて交互に積層することによって相変化メモリを形成する際に、処理基板Sの温度を250℃以上350℃以下の所定温度に維持する。加えて、互いに異なる組成を有する二つのターゲットであるGeTeターゲット22aとSb2Te3ターゲット22bの各々を互いに異なるタイミングでアルゴンガスによりスパッタする。このとき、互いに異なる組成を有した二つ以上の金属カルコゲナイド膜であるGeTe膜とSb2Te3膜とを毎秒3nm以上10nm以下の速度で前記基板上に積層する。

(もっと読む)

基板処理装置、およびそれを有する基板処理システム

【課題】基板処理装置に関し、より詳しくは、イオンビームを基板に照射して、基板にイオンを照射する基板処理を行う基板処理装置、それを有する基板処理システムに関する。

【解決手段】基板処理装置が、一つ以上の基板が安着されたトレーが移送される移送経路の設けられた工程チャンバーと、前記移送経路に沿って移送される基板にイオンビームを照射する、一つ以上のイオンビーム照射部と、を含む。

(もっと読む)

相変化メモリの形成方法、及び相変化メモリの形成装置

【課題】相変化膜の組成が変わることを抑えつつ、基板の凹部に対する相変化膜の埋め込み性を高めることのできる相変化メモリの形成方法、及び相変化メモリの形成装置を提供する。

【解決手段】相変化メモリの形成に際し、金属カルコゲナイドターゲットをスパッタして絶縁膜23の上面23s及びホール23h内に相変化膜24を形成する。次いで、相変化膜24を覆うキャップ膜25を形成する。更に、相変化膜24を加熱して、相変化膜24によってホール23hを埋め込むリフローを行う。キャップ膜25は、絶縁膜23よりも相変化膜24に対する濡れ性が低い材料で形成される。

(もっと読む)

酸化物導電性薄膜の処理方法、該処理方法を用いて製造した電子デバイス、液滴吐出ヘッド及び液滴吐出装置

【課題】所望の表面組成を有する酸化物導電性薄膜の処理方法、並びに該酸化物導電性薄膜の処理方法を用いて製造した電子デバイス、液滴吐出ヘッド及び液滴吐出装置を提供する。

【解決手段】一般式ABO3で示されるABO3型酸化物導電性薄膜を少なくとも水を含む液体で処理し、ABO3型酸化物導電性薄膜の表面の原子比A/Bを化学量論比に近づける。液体は少なくとも水を含むものであり、純水と有機溶剤との混合液、あるいは純水であることが好ましい。有機溶剤としては、少なくともアルコール類の1種を含むことが好ましい。

(もっと読む)

赤外線光学フィルタおよびその製造方法

【課題】近赤外線から遠赤外線までの広帯域における赤外線遮断機能を有する低コストの赤外線光学フィルタを提供する。

【解決手段】800nm〜20000nmの波長域の赤外線を制御する赤外線光学フィルタであって、半導体基板1と、当該半導体基板1の一表面側に形成された広帯域遮断フィルタ部2と、当該半導体基板2の他表面側に形成された狭帯域透過フィルタ部3とを備えている。広帯域遮断フィルタ部2は、屈折率が異なる複数種類の薄膜2a,2bが積層された多層膜からなり、当該複数種類の薄膜2a,2bのうち1種類の薄膜2aが遠赤外線を吸収する遠赤外線吸収材料(Al2O3、Ta2O5、SiO2の群から選択される酸化物もしくはSi3N4からなる窒化物)により形成され、残りの1種類の薄膜2bが上記遠赤外線吸収材料よりも屈折率の高い高屈折率材料であるSiにより形成されている。半導体基板1は、Si基板である。

(もっと読む)

炭素薄膜成膜方法

【課題】水素フリーで緻密で硬質なダイヤモンドライクカーボン膜を容易に形成することができる炭素薄膜成膜法を提供する。

【解決手段】この炭素被膜成膜方法は、マグネトロンスパッタ法により試料基板電極上に配置された試料基板表面に炭素被膜を堆積させる炭素被膜成膜装置を用い、炭素ターゲット基板電極と試料電極に対し、下記1〜4の条件でそれぞれ電圧を印加させることを特徴とする。

1.ターゲット基板電極に印加する電圧が負のパルス電圧であって、かつ、そのパルス電圧時間比が40%以下であること。

2.ターゲット基板電極に印加するパルス電圧のパルス時間が20μs〜200μsであること。

3.試料基板電極に印加する電圧が負のパルス電圧であって、かつ、そのパルス電圧時間比が50%以下であること。

4.試料基板電極に印加する負パルス電圧の大きさが−20V〜−200Vであること。

(もっと読む)

半導体装置

【課題】一定時間電力が供給されない状況でも記憶内容の保持が可能な半導体装置を提供すること。さらに、半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させること。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料として、ワイドバンドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能である。また、トランジスタの下に設けた配線層と、酸化物半導体膜の高抵抗領域と、ソース電極とを用いて容量素子を形成することで、トランジスタと容量素子の占有面積の低減を図る。

(もっと読む)

薄膜トランジスタ及びその製造方法、表示装置、イメージセンサー、X線センサー並びにX線デジタル撮影装置

【課題】400℃以下で作製可能であり、30cm2/Vs以上の高い電界効果移動度と、ノーマリーオフとなる低いオフ電流を両立する薄膜トランジスタを提供する。

【解決手段】ゲート電極16と、ゲート電極と接するゲート絶縁膜15と、In(x)Zn(1−x)O(y)(0.4≦x≦0.5,y>0)で表される第1の領域A1及びIn(a)Ga(b)Zn(c)O(d)(b/(a+b)>0.250,c>0,d>0)で表され、ゲート電極に対して第1の領域よりも遠くに位置する第2の領域A2を含み、ゲート絶縁膜を介してゲート電極に対向配置されている酸化物半導体層12と、互いに離間して配置されており、酸化物半導体層を介して導通可能なソース電極13及びドレイン電極14と、を有する薄膜トランジスタ1。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】重畳する第1のトランジスタおよび第2のトランジスタからなる第1のインバータと、重畳する第3のトランジスタおよび第4のトランジスタからなる第2のインバータと、第1の選択トランジスタと、第2の選択トランジスタと、を有し、第1のインバータの出力端子、第2のインバータの入力端子および第1の選択トランジスタのソースおよびドレインの一方が接続され、第2のインバータの出力端子、第1のインバータの入力端子および第2の選択トランジスタのソースおよびドレインの一方が接続されることによって、微細化したSRAM回路を形成する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてエネルギーギャップの異なる少なくとも2層の酸化物半導体層を含み、かつ積層された酸化物半導体層の間に混合領域を有する酸化物半導体積層を用いる。

(もっと読む)

圧電体膜素子の製造方法、圧電体膜素子及び圧電体デバイス

【課題】ドライエッチングにより微細加工を行った場合に、エッチング残渣が少なく、後工程における信頼性が高い非鉛の圧電体膜素子の製造方法、圧電体膜素子及び圧電体デバイスを提供する。

【解決手段】圧電体膜素子1の製造方法は、基板2上に、組成式(K1−xNax)NbO3で表されるペロブスカイト構造を有する非鉛のアルカリニオブ酸化物系化合物からなる圧電体膜5を形成する工程と、圧電体膜5を、フッ素系反応ガスを含む雰囲気中で低圧プラズマを用いてエッチングを行う工程とを含む。

(もっと読む)

スパッタリングターゲットの製造方法

【課題】大型ターゲット等の製造コストの低減を図った上で、ターゲットに起因するパーティクルの発生を抑制したスパッタリングターゲットの製造方法を提供する。

【解決手段】スパッタリングターゲット1の製造方法は、基体2と金属原料粒子とを準備する工程と、基体2にコールドスプレー法を適用して金属原料粒子を高速で吹付け、基体2上に金属粒子4の堆積膜からなるターゲット層3を形成する工程とを具備する。ターゲット層3のX線回折チャートにおける第1ピークと第2ピークとの比率をP1、金属原料粒子のX線回折チャートにおける第1ピークと第2ピークとの比率をP2としたとき、P1とP2との差が10%以内となるように、金属原料粒子を基体2に吹付ける。

(もっと読む)

成膜装置および成膜方法

【課題】銅めっき工程の電極に用いるCu堆積膜による貫通孔開口の閉塞状態を適切に制御できる成膜装置を提供する。

【解決手段】成膜装置100は、貫通孔が形成された基板34Bおよび銅放出源35Bを格納する真空チャンバ30と、真空チャンバ30内を所定の真空度に減圧する真空ポンプ36と、基板34Bに印加する電力を発生する電源80と、基板34Bおよび銅放出源35B間の距離の設定に用いる駆動機構と、を備える。銅放出源35Bから放出された銅材料を基板34Bの一方の主面に堆積させ、主面における貫通孔の開口を銅材料からなる堆積膜によって閉塞させるとき、堆積膜による開口の閉塞状態が、上記距離および上記電力に基づいて調整される。

(もっと読む)

光電変換素子用蒸着材料及び光電変換素子、センサ、撮像素子

【課題】光電変換効率が高く、光電流/暗電流のS/N比の良好であり、且つ、応答速度の速い光電変換素子を提供する

【解決手段】一対の電極(20,40)と、一対の電極(20,40)に挟持された少なくとも光電変換層32を含む受光層30を有する光電変換素子1は、受光層30の少なくとも一部の層が、フラーレン又はフラーレン誘導体を主成分とする複数の粒子又は該複数の粒子が成形されてなる成形体であり、複数の粒子のD50%で表される平均粒径が50μm〜300μmであるの光電変換素子用蒸着材料を用いて蒸着されたフラーレン又はフラーレン誘導体を含むものである。

(もっと読む)

強誘電体素子、インクジェット式記録ヘッド及びインクジェット式画像形成装置

【課題】エッチング残渣が少なく信頼性が良好であり、かつリーク電流を抑制することができる強誘電体素子を提供する。

【解決手段】シリコン基板10の上に順に、振動板11、下部電極20、強誘電体層30、上部電極40を形成し、強誘電体層30の側面の傾斜角はθ2=30°、上部電極40の側面の傾斜角はθ1=30°としている。これにより、エッチングガスやプラズマ粒子の衝突角度が平面に近づき、傾斜面でのエッチング残渣の除去率が向上する。

(もっと読む)

パターン形成用基板、圧電アクチュエータ製造方法、圧電アクチュエータ、液滴吐出ヘッド、および、液滴吐出装置

【課題】流動体を付着させて熱処理を行う工程を繰り返し行うことにより微細パターンの膜を所望の膜厚で精密に作製可能とするパターン形成用基板と、パターン形成用基板を用いた圧電アクチュエータの製造方法を提供する。

【解決手段】所定の流動体を特定領域に付着させて熱処理を行うことによりパターン化された膜を形成するためのパターン形成用基板10で、特定領域を親和性とし、それ以外の領域を非親和性とする表面改質をおこなう。パターン形成用基板10の表面改質処理対象となる金属膜はPt膜53を積層し、基体として、Ti,Ta,Zr,V,Nb,Mo,Wから選ばれる少なくとも1つの金属元素、酸素元素および炭素元素から構成されるMOC膜52を用いる。

(もっと読む)

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

圧電膜素子及び圧電膜デバイス

【課題】圧電特性に優れ且つ信頼性の高い圧電膜素子及び圧電膜デバイスを提供する。

【解決手段】基板1上に、少なくとも下部電極層2と、非鉛のアルカリニオブ酸化物系の圧電膜4とを配した圧電膜素子10において、前記下部電極層2は、立方晶、正方晶、斜方晶、六方晶、単斜晶、三斜晶、三方晶のいずれかの結晶構造、またはこれら結晶構造のうちの二以上の結晶構造が共存した状態を有し、前記結晶構造の結晶軸のうちの2軸以下のある特定の結晶軸に優先的に配向しており、前記基板1上における少なくとも一つの前記結晶軸を法線とした結晶面のX線回折強度分布において、前記結晶面のX線回折強度の相対標準偏差が57%以下である。

(もっと読む)

21 - 40 / 1,129

[ Back to top ]