Fターム[4K029BD01]の内容

Fターム[4K029BD01]の下位に属するFターム

リードフレーム、配線材料 (490)

Fターム[4K029BD01]に分類される特許

61 - 80 / 995

半導体装置

【課題】電源電圧の供給を停止しても、論理回路部間の接続関係、又は各論理回路部内の回路構成を維持できる半導体装置を提供する。また、論理回路部間の接続関係の変更、又は各論理回路部内の回路構成の変更を高速で行うことができる半導体装置を提供する。

【解決手段】再構成可能な回路において、回路構成や接続関係等のデータを記憶する半導体素子に酸化物半導体を用いる。特に、半導体素子のチャネル形成領域に、酸化物半導体が用いられている。

(もっと読む)

記憶素子、記憶装置、信号処理回路

【課題】消費電力を抑えることができる信号処理回路を提供する。

【解決手段】記憶素子に電源電圧が供給されない間は、揮発性のメモリに相当する第1の記憶回路に記憶されていたデータを、第2の記憶回路に設けられた第1の容量素子によって保持する。酸化物半導体層にチャネルが形成されるトランジスタを用いることによって、第1の容量素子に保持された信号は長期間にわたり保たれる。こうして、記憶素子は電源電圧の供給が停止した間も記憶内容(データ)を保持することが可能である。また、第1の容量素子によって保持された信号を、第2のトランジスタの状態(オン状態、またはオフ状態)に変換して、第2の記憶回路から読み出すため、元の信号を正確に読み出すことが可能である。

(もっと読む)

単結晶の製造方法

【課題】種結晶の側面や表面外周部からの原子の脱離を抑えることができ、高品質な単結晶の作製が可能な単結晶の製造方法を提供すること。

【解決手段】単結晶の製造方法は、種結晶9が固定された坩堝蓋8で密閉される坩堝7内に原料6を配置して、原料6を昇華させて単結晶を製造する単結晶の製造方法であって、坩堝蓋8に固定された種結晶9の露出面を覆うように、予め、種結晶9が昇華しない温度領域で結晶薄膜15を形成する成膜工程と、結晶薄膜15が形成された坩堝蓋8で坩堝7を密閉して、原料6を昇華させて単結晶を成長させる成長工程と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】作製コストが低減され、かつ歩留まりが向上された半導体装置、および消費電力が低減された半導体装置を提供することである。

【解決手段】第1のトランジスタおよび第2のトランジスタと、第1のトランジスタ群および第2のトランジスタ群を具備し、第1のトランジスタ群は、第3のトランジスタ、第4のトランジスタおよび4の端子を有しており、第2のトランジスタ群は、第5乃至第8のトランジスタおよび4の端子を有しており、第1のトランジスタ、第3のトランジスタ、第6のトランジスタ、第8のトランジスタはnチャネル型トランジスタが用いられ、第2のトランジスタ、第4のトランジスタ、第5のトランジスタ、第7のトランジスタはpチャネル型トランジスタが用いられる半導体装置である。

(もっと読む)

III族窒化物半導体発光素子

【課題】半導体発光素子において、インジウム組成の大小に対応したピーク波長が異なる複数の光を得る。

【解決手段】pn接合型のIII族窒化物半導体発光素子であって、第1の導電型を有する第1の半導体層、発光層及び第1の導電型とは逆の導電性を示す第2の半導体層が積層された積層半導体層を備え、積層半導体層の発光層は、発光層からの発光の取り出し方向と反対側に配置され第1のインジウム組成を有する第1の窒化ガリウム・インジウム層と、第1の窒化ガリウム・インジウム層より発光の取り出し方向側に配置され第1のインジウム組成より小さい組成の第2のインジウム組成を有する第2の窒化ガリウム・インジウム層と、第1の窒化ガリウム・インジウム層と第2の窒化ガリウム・インジウム層との間に設けられ、第1の窒化ガリウム・インジウム層及び第2の窒化ガリウム・インジウム層を構成する材料より格子定数が小さい材料からなる中間層と、を含む。

(もっと読む)

アライメント装置

【課題】 真空処理装置の処理室内において、マスクに対する基板のアライメントのために両者の位置関係を確実に検出できる簡単な構成で低コストのアライメント装置を提供する。

【解決手段】 真空チャンバ1内で相互に対向配置される基板Wとこの基板に対する処理範囲を制限するマスクWとのいずれか一方を保持する固定の保持手段5と、その他方を保持する、固定の保持手段に対して相対移動可能な可動の保持手段2とを備える。固定の保持手段内に、一端側が可動の保持手段で保持された基板またはマスクのいずれか他方に向けて開口し、その他端側が処理室を画成する壁面に向けて開口する光路52R,52Lが形成され、光路の他端側から光を入射する光源61と、この他端側から光路を通して他方を撮像する撮像手段62と、撮像手段からの出力に応じて可動の保持手段を相対移動させてアライメントを行う制御手段Cとを更に備える。

(もっと読む)

新規酸化物、及び酸化物膜

【課題】従来よりも抵抗値の低いIn2O3系酸化物導電膜を形成することができる酸化物を提供する。

【解決手段】インジウム元素(In)及びガリウム元素(Ga)を含有し、X線回折において、2θ=12〜18度、21〜24度及び43〜45度に回折ピークを有する酸化物。

(もっと読む)

p型半導体材料

【課題】低温でも良好に薄膜形成できるp型ZnO系半導体材料を提供する。

【解決手段】

ZnOとNiOの混合材料をスパッタターゲットとして、スパッタリングすることにより、Zn1-xNixO薄膜を基板上に形成する。Zn1-xNixO(xは、ZnとNiの合計モル数に対するNiモル数の比率である)は、ZnOとNiOとが混合した酸化物であり、xの値は0.65以下に設定してZnOに対する価電子帯トップのオフセット量を1eV以内に抑えることが好ましく、xの値は小さい方が好ましい。一方、電気伝導タイプをp型とし、電気抵抗を低く抑えることを考慮すると、Zn1-XNiXOにおけるXの値は0.13以上であることが好ましい。

(もっと読む)

In2O3−ZnO系スパッタリングターゲット及び酸化物導電膜

【課題】従来よりも抵抗値の低いIn2O3−ZnO系酸化物導電膜を形成することができるスパッタリングターゲットを提供する。

【解決手段】インジウム元素(In)、亜鉛元素(Zn)及び下記のA群から選択される少なくとも1つの元素(A)を含有し、In、Zn及びAの金属元素の組成(原子比)がInxZn(1-x)Ayで表わされる酸化物からなり、x及びyが下記式(1)及び(2)を満たすスパッタリングターゲット。

A群:Al、Mg、Ca、Sr、Ba、Sc、Y、Ti、Zr、Hf、Ga、B、Si、Ge、ランタノイド

0.68≦ x ≦0.95 (1)

0.0001≦ y ≦0.0045 (2)

(もっと読む)

導電性酸化物およびその製造方法、ならびに酸化物半導体膜

【課題】スパッタリング用ターゲットとして好ましく使用され得る導電性酸化物およびその製造方法を提供する。

【解決手段】結晶質In2O3と、結晶質Ga2ZnO4とを含む導電性酸化物であって、導電性酸化物において、Znの原子濃度比を1とした場合に、Inの原子濃度比が0.4以上1.8以下であり、かつ、Gaの原子濃度比が0.4以上1.8以下の導電性酸化物とし、In−Ga−Zn−O酸化物のスパッタリング用のターゲットとして用いること。

(もっと読む)

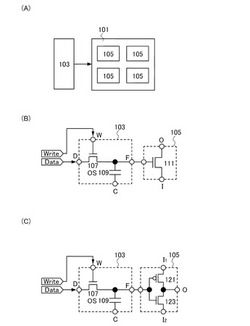

記憶素子、信号処理回路

【課題】新たな構成の不揮発性の記憶素子、それを用いた信号処理回路を提供する。

【解決手段】第1の回路と第2の回路とを有し、第1の回路は第1のトランジスタと第2のトランジスタとを有し、第2の回路は第3のトランジスタと第4のトランジスタとを有する。第1の信号に対応する信号電位は、オン状態とした第1のトランジスタを介して第2のトランジスタのゲートに入力され、第2の信号に対応する信号電位は、オン状態とした第3のトランジスタを介して第4のトランジスタのゲートに入力される。その後、第1のトランジスタ及び第3のトランジスタをオフ状態とする。第2のトランジスタの状態と第4のトランジスタの状態との両方を用いて、第1の信号を読み出す。第1のトランジスタ及び第3のトランジスタは、チャネルが酸化物半導体層に形成されるトランジスタとする。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】信号処理回路は、電源電圧が選択的に供給され、第1の高電源電位が選択的に与えられる第1のノードを有する回路と、第1のノードの電位を保持する不揮発性の記憶回路とを有する。不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなる第2のノードとを有する。トランジスタはエンハンスメント型のnチャネル型のトランジスタである。トランジスタのゲートには、第2の高電源電位または接地電位が入力される。電源電圧が供給されないとき、トランジスタはゲートに接地電位が入力されてオフ状態を維持する。第2の高電源電位は、第1の高電源電位よりも高い。

(もっと読む)

メモリ装置、及びメモリ装置の作製方法

【課題】可能な限り占有面積が削減され、データ保持期間の極めて長いメモリ装置を提供する。

【解決手段】メモリ装置内のメモリ素子のセルトランジスタとして、リーク電流の極めて小さいトランジスタを用いる。さらにメモリセルの占有面積を縮小するために、ビット線とワード線とが交差する領域に、当該トランジスタのソース及びドレインが縦方向に積層されるように形成すればよい。さらにキャパシタは、当該トランジスタの上方に積層すればよい。

(もっと読む)

記憶装置及び半導体装置

【課題】データの保持期間を確保しつつ、単位面積あたりの記憶容量を高めることができる記憶装置を提供する。

【解決手段】複数のビット線を幾つかのグループに分割し、複数のワード線も幾つかのグループに分割する。そして、一のグループに属するビット線に接続されたメモリセルには、一のグループに属するワード線が接続されるようにする。さらに、複数のビット線は、複数のビット線駆動回路102a,102b,102cによってグループごとにその駆動が制御されるようにする。加えて、複数のビット線駆動回路102a,102b,102cと、ワード線駆動回路101とを含めた駆動回路上に、セルアレイ103a,103b,103cを形成する。駆動回路とセルアレイ103a,103b,103cが重なるように三次元化することで、ビット線駆動回路が複数設けられていても、記憶装置の占有面積を小さくすることができる。

(もっと読む)

半導体記憶装置

【課題】電源電圧の供給の停止及び再開を行う構成において、揮発性の記憶装置と不揮発性の記憶装置との間のデータの退避及び復帰の必要のない半導体記憶装置を提供する。

【解決手段】不揮発性の半導体記憶装置とする際、揮発性の記憶装置と不揮発性の記憶装置を分離することなく構成する。具体的に半導体記憶装置には、酸化物半導体を半導体層に有するトランジスタ及び容量素子に接続されたデータ保持部にデータを保持する構成とする。そしてデータ保持部に保持される電位は、電荷をリークすることなくデータの出力が可能なデータ電位保持回路及び電荷をリークすることなくデータ保持部に保持した電位を容量素子を介した容量結合により制御可能なデータ電位制御回路で制御される。

(もっと読む)

ロータリースパッタリングカソード、及びロータリースパッタリングカソードを備えた成膜装置

【課題】スパッタリングによるターゲットの消耗を抑えつつ、ターゲット表面に付着する付着物の除去を行うことが可能なロータリースパッタリングカソード、およびロータリースパッタリングカソードを備えた成膜装置を提供すること。

【解決手段】ターゲット21の外表面に付着した付着物を加熱して昇華させて除去する除去手段51、又は、付着物を機械的に除去する除去手段を備える構成とする。これにより、従前のような付着物除去のためのスパッタリングを不要とする。付着物を加熱して昇華させる除去手段としては、例えばフィラメント51を用い、付着物を機械的に除去する除去手段としては、例えばブラシ53を用いることができる。これにより、ターゲットの消耗を抑えつつ、付着物を取り除くことができる。

(もっと読む)

記憶素子及び記憶装置

【課題】電力の供給が停止した後もデータを保持することができる、新たな構成の記憶素子を提供することを目的の一とする。

【解決手段】記憶素子は、ラッチ回路と、第1の選択回路と、第2の選択回路と、第1の不揮発性記憶回路と、第2の不揮発性記憶回路と、を有する。また、第1の不揮発性記憶回路及び第2の不揮発性記憶回路は、それぞれトランジスタ及び容量素子を有する。第1及び第2の不揮発性記憶回路のそれぞれが有するトランジスタは、チャネルが酸化物半導体膜に形成されるトランジスタである。当該トランジスタは、オフ電流が極めて低いため、トランジスタと容量素子の接続点であるノードにデータが入力された後、トランジスタがオフ状態となり、電源電圧の供給が停止しても、長期間にわたりデータを保持することができる。

(もっと読む)

記憶装置、及び半導体装置

【課題】高速動作を実現できる記憶装置、或いは、リフレッシュ動作の頻度が低減できる記憶装置を提供する。

【解決手段】セルアレイ101の内部において、メモリセル100に接続された配線に、駆動回路102から電位の供給が行われる。さらに、駆動回路102上にセルアレイ101が設けられており、セルアレイ101が有する複数の各メモリセル100は、スイッチング素子と、スイッチング素子により電荷の供給、保持、放出が制御される容量素子とを有する。そして、スイッチング素子として用いられるトランジスタは、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い半導体を、チャネル形成領域に含んでいる。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

プラズマ処理装置及び基板処理方法

【課題】不純物を含む表層から基板に不純物を注入するための、実用性に優れるプラズマ処理装置及び基板処理方法を提供する。

【解決手段】プラズマ処理装置10は、不純物を含む基板Wの表層から要求される注入深さへ不純物を注入するプラズマ処理のためのプラズマ処理パラメタ設定部13を備える。プラズマ処理パラメタは、プラズマ処理により不純物濃度が基準値に等しくなる基板表面からの深さを決定づける主パラメタ例えばバイアス電圧と、不純物濃度を基準値に飽和させる飽和範囲をもつ副パラメタ例えばプラズマ処理時間と、を含む。設定部13は、要求される注入深さから主パラメタを設定する第1設定処理と、副パラメタを設定する第2設定処理と、を実行する。

(もっと読む)

61 - 80 / 995

[ Back to top ]