Fターム[4K029BD02]の内容

Fターム[4K029BD02]に分類される特許

121 - 140 / 490

ポリアリーレンエーテルケトンより成るフィルム

次の成分:a)ポリアリーレンエーテルケトン60〜96質量部、b)六方晶窒化ホウ素2〜25質量部、並びにc)タルク2〜25質量部を包含し、その際、成分a)、b)及びc)の質量部の合計が100である成形材料が、寸法安定性のプリント回路基板の製造に適している5〜1200μmの厚さを有するフィルムの製造のために使用されることができる。 (もっと読む)

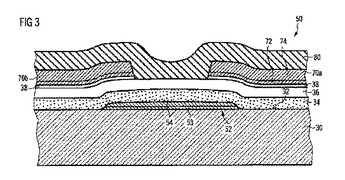

半導体デバイスを製造する方法および設備と半導体デバイス

半導体デバイスを生産する方法が提供され、この半導体デバイス(50)は、基板(30)と、半導体層(36、38)と、基板および半導体層から選択された少なくとも1つの要素に隣接する少なくとも1つのメタライゼーション層(52、70)とを含み、この方法は、基板および半導体層から選択された少なくとも1つの要素の近くに酸素を含む少なくとも1つのメタライゼーション層を形成するステップを含む。  (もっと読む)

(もっと読む)

スパッタリングターゲットの製造方法

【課題】種々の金属材料などからなるスパッタリングターゲットにおいて、各種デバイスの高性能化などに伴って益々厳しくなってきているスパッタ膜への要求特性を満足させる。具体的には、スパッタ膜の膜厚分布や膜組成の均一化、各種機能材料として用いられる膜の諸特性の向上および均一化、ダスト発生数の低減などを図る。

【解決手段】Mnを主成分とし、各部位の酸素量を全体の酸素量の平均値に対して±27%以内の範囲にあるスパッタリングターゲット、またはMnを主成分とし、各部位の窒素量を全体の酸素量の平均値に対して±75%以内の範囲にあるスパッタリングターゲットを製造する方法において、Mnを主成分とする粗金属材を真空溶解して溶解材を得る工程と、前記溶解材に所定の処理および加工を施して所定の形状に成形する工程とを有する。

(もっと読む)

載置台構造及びプラズマ成膜装置

【課題】プラズマ側にバイアス用の高周波電力を安定的に投入することによりプラズマ処理の再現性を高く維持することができる載置台構造を提供する。

【解決手段】金属膜を形成する被処理体Wを載置し、隙間94を隔ててグランド側に接続された保護カバー部材92により囲まれた載置台構造において、被処理体を載置する電極としての載置台本体48と、載置台本体の下方に配置されて絶縁状態で設けられたベース台50と、ベース台を支持してグランド側に接続された支柱46と、載置台本体に接続されてバイアス用の高周波電力を供給する高周波給電ライン70と、高周波電力が印加されるホット側とグランド側との間に形成された電力安定用コンデンサ部120とを備え、電力安定用コンデンサ部の静電容量は、載置台本体と保護カバー部材との間で形成される浮遊容量の静電容量よりも大きく設定されている。

(もっと読む)

スパッタリング装置およびスパッタリング方法並びに成膜システム

【課題】単一のスパッタリングチャンバを用いて基板に形成された開口部内へのAl材料の埋め込みを適切に行えるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、スパッタリングチャンバ30と、カソードユニット41およびアノードA間の放電によりプラズマを形成可能なプラズマガン40と、プラズマガン40から放出されたプラズマ22を磁界の作用によりシート状に変形可能な磁界発生手段24A、24Bと、を備える。シートプラズマ27は、スパッタリングチャンバ30内の基板34BとAlターゲット35Bとの間を通過するように誘導され、シートプラズマ27中の荷電粒子によってAlターゲット35BからスパッタリングされたAl材料が基板34Bの開口部に堆積する際に、Al堆積膜200のカバレッジ性が、プラズマ放電電流ID、ターゲットバイアス電圧VB、および、ターゲット−基板間距離Lに基づいて調整される。

(もっと読む)

Cu系配線材料前駆体、Cu系配線材料およびこれらの形成方法

【課題】Cu-Ti系スパッタ膜を従来よりも低い温度で熱処理しても、配線表面にTi系自己拡散バリア膜を形成できるようにする。

【解決手段】極薄のTi系膜を第一の膜2として基材1上に形成した後、Ti系材料のTi系材料とCu系材料との傾斜構造を持つ複合膜を第二の膜3として形成し、その上にCu系電極となる第三の膜4を形成することにより、3層構造の前駆体を形成する。この前駆体を450℃以下で熱処理することで、Ti系バリア膜を有するCu系電極を形成することが可能となる。

(もっと読む)

スパッタリングターゲットとそれを用いたTa−W合金膜および液晶表示装置

【課題】Ta−W系スパッタリングターゲットにおいて、面内の抵抗ばらつきが小さいと共に、下地膜との密着力に優れたTa−W合金膜を再現性よく得ることを可能にする。

【解決手段】Ta−W系スパッタリングターゲットは、0.05〜2質量%の範囲のWを含有し、残部が実質的にTaからなると共に、ターゲット全体としてのW含有量のばらつきが±20%以内とされている。このようなTa−W系スパッタリングターゲットを用いて成膜したTa−W合金膜は、例えばTFD素子1の第1の電極3に適用される。TFD素子1は第1の電極3/陽極酸化膜4/第2の電極5によるMIM構造を有し、液晶表示装置のスイッチング素子等に適用される。

(もっと読む)

半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲット

【課題】 バリア膜形成による配線の抵抗値増大及びボイドの発生を防ぐことができる半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲットを提供すること。

【解決手段】 Si酸化物を含む絶縁膜1にCuの配線が設けられている半導体装置であって、絶縁膜1に設けられた溝状の開口部1aの内面に形成されたバリア膜4と、開口部1a内であってバリア膜4上に形成されたCuからなる配線本体2と、を備え、バリア膜4が、バリア膜4が、少なくとも絶縁膜1上に形成されたBa酸化物及びSr酸化物の少なくとも一方を含有するCu合金下地層を有し、該Cu合金下地層と絶縁膜1との界面にBaSi酸化物及びSrSi酸化物の少なくとも一方が偏析している。

(もっと読む)

スパッタリングターゲットの製造方法及びスパッタリングターゲット

【課題】半導体素子などに用いられるCu配線のバリア層の形成に好適なスパッタリングターゲットの製造方法及びスパッタリングターゲットを提供する。

【解決手段】粗金属Taをエレクトロンビーム溶解して高純度Taインゴットを精製する工程と、得られた高純度Taインゴットに対して鍛造、圧延による塑性加工を施す工程と、塑性加工を施した前記高純度Taインゴットに熱処理を施す工程と、を有することを特徴とするスパッタリングターゲットの製造方法、及びパッタリングターゲット。

(もっと読む)

ダミー基板の使用方法

【課題】ダミー基板の反りを抑えることができる基板処理装置におけるダミー基板の使用方法を提供すること。

【解決手段】ダミー基板格納部に格納されている複数のダミー基板の各々について、プロセスチャンバにて行われるプロセスレシピに基づき、成膜された膜の種別と膜厚とを含む成膜履歴をコンピュータにより作成する工程と、膜の種別ごとに膜厚と成膜による基板の曲率変化とを対応付けた曲率データを用い、この曲率データとダミー基板の前記成膜履歴とに基づいて、当該ダミー基板の曲率をコンピュータにより求める工程と、求められたダミー基板の曲率と、曲率データと、成膜処理の膜の種別及び膜厚を含むプロセススケジュールと、に基づいて、ダミー基板の反りが抑えられるようにプロセスチャンバに対する搬送スケジュールを作成する工程と、を実施する。

(もっと読む)

半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲット

【課題】 バリア膜形成による配線の抵抗値増大及びボイドの発生を防ぐことができる半導体装置、その製造方法及びその製造方法に用いるスパッタリングターゲットを提供すること。

【解決手段】 Si酸化物を含む絶縁膜1にCuの配線が設けられている半導体装置であって、絶縁膜1に設けられた溝状の開口部1aの内面に形成されたバリア膜4と、開口部1a内であってバリア膜4上に形成されたCuからなる配線本体2と、を備え、バリア膜4が、バリア膜4が、少なくとも絶縁膜1上に形成されたCa酸化物を含有するCu合金下地層4aを有し、該Cu合金下地層4aと絶縁膜1との界面にCaSi酸化物が偏析している。

(もっと読む)

スパッタリング装置およびスパッタリング方法

【課題】単一のスパッタリングチャンバを用いて基板に形成された開口部内へのAl材料のコンタクト埋め込みを適切に行えるスパッタリング装置を提供する。

【解決手段】スパッタリング装置100は、Alからなるターゲット35Bおよび開口部が形成された基板34Bを格納可能なスパッタリングチャンバ30と、カソードユニット41およびアノードA間の放電によりプラズマを形成可能なプラズマガン40と、プラズマガン40から放出されたプラズマを磁界の作用によりシート状に変形可能な磁界発生手段24A、24Bと、を備える。シートプラズマ27は、スパッタリングチャンバ30内の基板34Bとターゲット35Bとの間を通過するように誘導され、シートプラズマ27中の荷電粒子によってターゲット35BからスパッタリングされたAl材料が基板34Bの開口部に堆積する際に、Al材料からなる堆積膜のカバレッジ性が、プラズマ放電電流IDおよび基板バイアス電圧VAに基づいて調整されている。

(もっと読む)

半導体装置の製造方法及びスパッタリング装置

【課題】半導体基板にシリサイド形成用の金属膜を形成する時に、ゲート絶縁膜にダメージが加わることを抑制する。

【解決手段】このスパッタリング装置は、チャンバ101、ウェハステージ102、リングチャック104、金属ターゲット105、防着シールド107、マグネット108、コリメータ109、並びに直流電源110,120を備えている。直流電源110は、コリメータ109に負電圧のみを印加するために設けられている。コリメータ109に印加される負電圧は、金属ターゲット105に印加される電圧より低電圧、例えば−70V以上−50V以下である。

(もっと読む)

表示装置用Al合金膜、表示装置およびAl合金スパッタリングターゲット

【課題】バリアメタル層を省略して透明画素電極と直接接続させた場合にも低コンタクト抵抗を示し、且つ、表示装置の製造過程における現像液耐食性や剥離液耐食性も高められた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で、透明導電膜と直接接続されるAl合金膜であって、Al合金膜は、グループAに属するNiおよび/またはCoの元素を0.5原子%以下(0原子%を含まない。)と、Geを0.2〜2.0原子%と、グループBに属するYおよび/またはZrの元素を3原子%以下(0原子%を含まない。)とを含有する。

(もっと読む)

配線構造及びその形成方法

【課題】良質な配線構造、及びその形成方法を提供する。

【解決手段】第1の導電材及び第1の絶縁層を有する第1の配線層と、前記第1の絶縁層上の第2の配線層とを備え、前記第2の配線層は第2の絶縁層と、ヴィア及びトレンチを有する開口部とを有し、前記開口部は、第2の導電材と、前記第2の導電材と、前記第2の絶縁層との間の2層以上のバリア層とを有し、前記第2の導電材は、前記第1の導電材と電気的に接続され、前記2層以上のバリア層は、前記開口内の前記第2の絶縁層と第1のバリア層とが接触し、且つ前記第1のバリア層とMnOx含有バリア層とが接触する領域と、前記第2の絶縁層と前記MnOx含有バリア層が接触する領域とを有する。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の電極に関するもの又は接合工程を有する半導体装置の作製方法に関し、(1)Al電極を用いることにより高抵抗になること、(2)AlとSiとが合金を形成すること、(3)スパッタ法により形成する膜が高抵抗になること、(4)接合工程では、それぞれの面の表面に凹凸が大きいと接合不良が生じること、が課題である。

【解決手段】金属基板又は金属膜が形成された基板を有し、金属基板上又は金属膜上の銅(Cu)メッキ膜を有し、Cuメッキ膜上のバリア膜と、バリア膜上の単結晶シリコン膜と、単結晶シリコン膜上の電極層と、を有する半導体装置を用いる。Cuメッキ膜と金属基板又は金属膜とを接合する際に熱圧着法を用いる。

(もっと読む)

スパッタリング装置および半導体装置製造方法

【課題】半導体装置基板のスパッタリングプロセスで特に周辺部に付着するパーティクルを抑制できるスパッタリング装置および半導体装置製造方法を提供する。

【解決手段】スパッタリング装置は、真空処理室1内に、ステージ2と、ターゲット4と、デポリング8と、カバーリング7とを備える。またプラズマ発生手段と、ステージ2に静電チャック作用を発生させる直流電源3と、ターゲット4のコンディショニング時にステージ2全体をプラズマから遮蔽して保護するシャッターディスク9と、クリーニング時にステージ2の基板設置面のみを覆ってプラズマから保護する保護ディスク12とを備える。保護ディスク12が上記サイズであることにより、ステージ2の側壁とデポリング8との間の余剰な成膜物も除去が可能となる。

(もっと読む)

半導体装置の製造方法

【課題】パワーMOSFETにおいては、アルミニウム系ソース電極下のアルミニウム拡散バリア・メタル膜として、チタンおよび窒化チタンからなるチタン系バリア・メタル膜が広く使用されている。しかし、本願発明者らが検討したところによると、チタン系バリア・メタル膜を使用すると、ウエハの反りが増大して、ウエハ・ハンドリングが困難となり、ウエハ割れやウエハ欠け等の問題が不可避となることが明らかとなった。この傾向は、最小寸法が0.35マクロ・メートル以下の製品において特に顕著である。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜(TiW等のタングステンを主要な成分とする合金膜)をスパッタリング成膜によって形成する際、スパッタリング成膜チャンバの気圧を1.2パスカル以下とするものである。

(もっと読む)

窒化物系半導体素子およびその製造方法

【課題】m面基板上で結晶成長させたGaN系半導体素子のコンタクト抵抗を低減する。

【解決手段】本発明の窒化物系半導体素子は、表面12がm面であるp型半導体領域を有する窒化物系半導体積層構造20と、p型半導体領域上に設けられた電極30とを備える。p型半導体領域は、AlxInyGazN(x+y+z=1,x≧0, y≧0, z≧0)半導体層26から形成されている。電極30は、p型半導体領域の表面12に接触したMg層32と、Mg層32の上に形成された金属層34とを含み、金属層34は、Auと比較してMgと合金を形成し難い金属から形成されている。

(もっと読む)

スパッタリングターゲット及びこれを利用して製造される半導体素子

【課題】スパッタリングターゲット及びこれを利用して製造される半導体素子を提供する。

【解決手段】重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成されるスパッタリングターゲットであり、また、バリア層と、バリア層上のシード層と、シード層上の導電層と、を備え、導電層は、重量%で0.01%以上から1%未満のNi、及び残部としてW及びその他の不回避な不純物で構成される、タングステンとニッケルとの合金薄膜を備える半導体素子である。

(もっと読む)

121 - 140 / 490

[ Back to top ]