Fターム[4K029BD02]の内容

Fターム[4K029BD02]に分類される特許

181 - 200 / 490

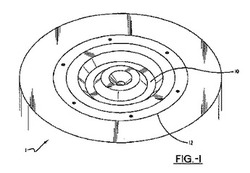

円形溝プレス装置とスパッターリングターゲットの製造方法

円形溝プレス加工によって金属ターゲットブランク(1)を製造する方法が、金属または合金ターゲットブランク(1)を第一の円形溝付きプレス加工ダイ・セット(20A、20B)内でプレスして第一の同心波形となるようにし、このときターゲットブランク(1)の元の直径が保たれるようにして、ターゲットブランク(1)内に同心円状のせん断変形部が形成されるようにすることを含む。次に、平坦ダイ・セット(30A、30B)によって当該同心波形ターゲット(1)ブランクに当該ターゲットブランクを実質的に平坦にするのに十分な力を加えて、当該ターゲットブランク(1)の元の直径を保ったまま、当該ターゲットブランク(1)を実質的に平坦な状態に戻す。当該ターゲットブランク(1)を第二の円形溝付きダイ・セット(40A、40B)内でプレスして第二の同心波形となるようにし、このとき当該ターゲットブランク(1)の元の直径が保たれるようにし、さらにこのとき、当該第二のダイ・セット(40A、40B)が当該第一のダイ・セット(20A、20B)の溝パターンからずれた溝パターンを有し、当該ターゲットブランクのそれ以前に変形されなかった領域に同心円状のせん断変形部が形成されるようにする。ふたたび、平坦ダイ・セット(30A、30B)によって当該同心波形ターゲットブランク(1)に当該ターゲットブランク(1)を実質的に平坦にするのに十分な力を加えて、当該ターゲットブランク(1)の元の直径を保ったまま、当該ターゲットブランクを実質的に平坦な状態に戻す。 (もっと読む)

半導体装置の作製方法

【課題】ソース電極層及びドレイン電極層表面に酸化物や汚染物の皮膜が生じたまま、その上に酸化物半導体層を形成すると、ソース電極層またはドレイン電極層と酸化物半導体膜との接触面に電気的に高抵抗な界面が形成され、半導体素子のオン電流が抑制されてしまう。

【解決手段】ソース電極層及びドレイン電極層の表面をプラズマでスパッタリング処理し、当該ソース電極層及びドレイン電極層を大気にさらすことなく、当該ソース電極層及びドレイン電極層上に連続してIn、Ga、及びZnを含む酸化物半導体層を形成する。

(もっと読む)

ダメージフリー被覆刻設堆積法

【課題】周辺表面を汚染もしくは乱さずに、スパッタリングした銅シード層を堆積させて、所望の形状に刻設する方法を提供する。

【解決手段】底部516と、側壁514と、上側開口526とを有する複数の凹状のデバイス特徴を含む基板上に銅シード層を堆積させる方法であって、a)基板表面からのスパッタリングを引き起こす態様において前記凹状のデバイス特徴の基板表面に衝突することなく前記銅シード層の第1の部分を前記基板上にスパッタ堆積するステップと、b)前記銅シード層の第2の部分を前記基板上にスパッタ堆積すると同時に、銅シード層の前記第1の部分の少なくとも一部を、前記複数の凹状のデバイス特徴のそれぞれの底部から対応する側壁へと再配分するステップと、を備える。

(もっと読む)

スパッタリングターゲットの製造方法及びスパタリングターゲット

【課題】 ガラス基板やSi系下地膜との密着性やバリア性に優れた配線膜を形成するための酸素を含有したCu合金ターゲットに関して、ターゲット中に存在する酸素を均一に分散させたスパッタリングターゲットの製造方法およびその製造方法で作製されるスパッタリングターゲットを提供する。

【解決手段】 酸素含有雰囲気中で加熱処理して酸素導入したCu粉末と、Cuよりも酸化物形成自由エネルギーが小さい元素から選ばれる少なくとも1種類以上の添加元素粉末とを混合した後に加圧焼結し、Cuと添加元素と酸素の総和を100原子%とした時に、添加元素を0.05〜10原子%含有するとともに、酸素を5.0原子%以上かつCuと添加元素が形成する酸化物の化学量論量以下含有するスパッタリングターゲット素材を得るスパッタリングターゲットの製造方法である。

(もっと読む)

Al基合金スパッタリングターゲットおよびその製造方法

【課題】成膜速度を速くしても、アーキング(異常放電)などのスパッタリング不良が発生しないNi含有Al基合金スパッタリングターゲットを提供する。

【解決手段】Niを0.05〜10原子%含有するAl基合金スパッタリングターゲットであり、後方散乱電子回折像法によってNi含有Al基合金スパッタリングターゲットのスパッタリング面法線方向の結晶方位<001>、<011>、<111>、および<311>が下記(1)〜(3)の要件:

(1)<001>±15°と<011>±15°と<111>±15°と<311>±15°との合計面積率をP値としたとき、スパッタリング面全面積に対するP値の比率は70%以上、

(2)P値に対する、<011>±15°の面積率の比率は30%以上、

(3)P値に対する、<111>±15°の面積率は10%以下

の要件を満足するNi含有Al基合金スパッタリングターゲットである。

(もっと読む)

微細結晶粒銅材料の製造方法、微細結晶粒銅材料及びスパッタリングターゲット

【課題】高純度銅や低濃度銅合金からなり、結晶粒が微細化されるとともに熱的に安定した微細結晶粒銅材料を低コストで製造することが可能な微細結晶粒銅材料の製造方法、この製造方法によって製造される微細結晶粒銅材料、並びに、この微細結晶粒銅材料からなるスパッタリングターゲットを提供する。

【解決手段】高純度銅または低濃度銅合金からなる銅素材1に対して、異なる方向からそれぞれ圧縮加工を施す多軸鍛造加工処理を行い、結晶粒が微細化された銅材料を製出する微細結晶粒銅材料の製造方法であって、前記多軸鍛造加工処理における1パス目の圧縮加工を行う初期加工温度T1が、銅素材1において動的再結晶が少なくとも部分的に発生する温度であることを特徴とする。

(もっと読む)

スパッタリング装置及び半導体装置の製造方法

【課題】マルチチャンバーにおけるステージ温度の急激な低下を抑制することによって品質異常を抑制することのできるスパッタリング装置を提供する。

【解決手段】本発明に係るスパッタリング装置は、第1チャンバーと、第2チャンバーと、第3のチャンバーとを具備しており、第3のチャンバーにて処理待ち状態が所定時間経過した後(S5)、ダミー収容室内のダミー基板を第2チャンバー内にて、ダミー基板を加熱しながらダミー基板上に金属膜をスパッタリング成膜し、第2チャンバー内のダミー基板を第3チャンバー内にて、ダミー基板を加熱しないで金属膜上に第2の膜をスパッタリング成膜する(S7)。その後、第3チャンバーにおいて、第2チャンバーによって金属膜が成膜された基板を加熱しない状態で金属膜上に第2の膜をスパッタリング成膜する(S8)。これによって、マルチチャンバーにおけるステージ温度を制御することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体層とソース電極層及びドレイン電極層との間にバッファ層が設けられた順スタガ型(トップゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン電極層と半導体層との間に、半導体層よりもキャリア濃度の高い金属酸化物層をバッファ層として意図的に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

銅配線基板の製造方法

【課題】 電気抵抗のさらなる低減化と基板表面に対する銅薄膜の密着性の確保との両方を高いレベルで達成することができ、かつスパッタリングプロセスで用いられる金属ターゲット材のコスト削減やそれを用いたスパッタリングプロセスを中心として全体的な製造プロセスのコスト低減を達成することを可能とした、銅配線基板の製造方法を提供する。

【解決手段】 本発明の銅配線基板の製造方法は、ガラスまたは石英からなる基板1の表面2に、例えばArガスのような不活性ガスのプラズマ4を照射することで、その表面2に改質を施して、その基板1の表面2自体における純Cuに対する密着性を向上させ、その基板1の表面2の直上に、銅薄膜3をスパッタリングによって形成することを特徴としている。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面に対する合金膜の付着性(サイドカバレッジ)を向上させることができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18は、バイアススパッタ法により形成される。そして、そのバイアススパッタ法による合金膜18の形成時には、第2溝11およびビアホール12の内面に向けて飛散するスパッタ粒子のエネルギーにより、第2溝11およびビアホール12の底面に付着しているスパッタ粒子が弾き飛ばされ、その弾き飛ばされたスパッタ粒子が第2溝11およびビアホール12の側面に再付着(リスパッタ)するように、スパッタ粒子を加速するためのRFバイアスが設定される。

(もっと読む)

フラットパネルディスプレイ用配線膜形成用スパッタリングターゲット

【課題】フラットパネルディスプレイの銅合金配線膜および銅合金配線膜を形成するためのスパッタリングターゲットを提供する。

【解決手段】Mg:0.1〜5原子%を含有し、さらにMnおよびAlのうちの1種または2種の合計:0.1〜11原子%を含有し、必要に応じてP:0.001〜0.1原子%を含有し、残部がCuおよび不可避不純物からなる組成を有するフラットパネルディスプレイ用配線膜を形成するためのスパッタリングターゲット、並びにこのターゲットを用いて成膜したMg:0.1〜5原子%を含有し、さらにMnおよびAlのうちの1種または2種の合計:0.1〜11原子%を含有し、必要に応じてP:0.001〜0.1原子%を含有し、残部がCuおよび不可避不純物からなる組成を有する銅合金薄膜からなるフラットパネルディスプレイ用配線。

(もっと読む)

半導体装置の製造方法

【課題】溝を埋め尽くすように形成されるCu層中のMnの残留量の増加を生じることなく、溝の側面上における合金膜の膜剥がれの発生を防止することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む絶縁材料からなる第2絶縁層6に、第2溝11が形成される。次に、スパッタ法により、第2溝11の内面に、CuMn合金からなる合金膜18が被着される。この合金膜18は、第2溝11の内面に接する部分のMn濃度が相対的に高く、その表層部分のMn濃度が相対的に低くなるように形成される。次いで、合金膜18上に、Cuからなる第2配線14が形成される。第2配線14の形成後、熱処理により、第2配線と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。

(もっと読む)

積層体、圧電素子、および液体吐出装置

【課題】低抵抗性で耐熱性に優れ、表面凹凸が小さい低抵抗金属層を備える積層体、このような積層体上に形成され、膜質のバラツキや表面粗さの小さい高品質な圧電体層を備える圧電素子、およびこの圧電素子を用いた液体吐出装置を提供する。

【解決手段】圧電素子10は、積層体30を用いるもので、基板12、熱酸化膜14、密着金属層16、金含有層18、密着金属層20、金属層22、圧電体層24、上部電極層26をこの順で積層した積層構造を有する。密着金属層16、金含有層18、密着金属層20および金属層22は、電極層、特に、下部電極層として用いられる低抵抗金属層28を構成し、基板12、熱酸化膜14および低抵抗金属層28は、積層体30を構成する。

(もっと読む)

スパッタターゲットの製造方法

【課題】ヒロック、エッチング残渣、ITO等との電気化学反応の発生を防止した低抵抗な配線膜を再現性よく成膜することができ、かつスパッタ時におけるダスト発生を抑制したスパッタターゲットの製造方法を提供する。

【解決手段】Y、Sc、La、Ce、Nd、Sm、Gd、Tb、DyおよびErから選ばれる少なくとも1種の第1の元素を0.001〜30原子%の範囲で含み、かつ第2の元素としてCを第1の元素に対して1.8原子ppm〜1630原子ppmの範囲で含み、残部がAlからなるスパッタターゲットを作製するにあたって、第1の元素を配合したAlを溶解した後、急冷凝固法により第1の元素とAlの金属間化合物が均一分散されたインゴットを作製する。このインゴットに熱間加工または冷間加工および機械加工を行ってスパッタターゲットを作製する。

(もっと読む)

スパッタリングカソード、スパッタリングカソードを備えたスパッタリング装置、成膜方法、および電子装置の製造方法

【課題】ターゲットと磁石ユニットとの距離の調整の自由度を高めることができるスパッタリングカソードを提供すること。

【解決手段】本発明の一実施形態に係るスパッタリングカソードは、ターゲット1の裏面に対向する位置に配置される複数の磁石ユニット7と、ターゲット1と磁石ユニット7との間の距離を各々の磁石ユニット7ごとに個別に調節する距離調節機構とを有する。また、スパッタリングカソードは、複数の磁石ユニット7をターゲットの裏面に平行に往復移動させる往復移動機構を有する。複数の磁石ユニット7、距離調節機構及び往復移動機構を、真空排気することが可能な磁石室に収容しても良い。

(もっと読む)

成膜方法及び処理システム

【課題】例えばCu膜に対するバリヤ性及び密着性を高く維持することができる層構造を形成する成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器132内で、表面に凹部2を有する被処理体Wの表面に成膜処理を施す成膜方法において、遷移金属含有原料ガスを用いて熱処理により遷移金属含有膜210を形成する遷移金属含有膜形成工程と、元素周期表のVIII族の元素を含む金属膜212を形成する金属膜形成工程とを有するようにする。これにより、例えばCu膜に対するバリヤ性及び密着性を高く維持する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】配線材との密着性が良く、バリア性の高い金属膜をもつ半導体装置、およびその製造方法を提供する。

【解決手段】基板上に絶縁膜、金属からなるバリアメタル膜、及びCu配線金属膜がこの順で積層された積層構造を具備してなり、バリアメタル膜の酸化物のX線回折測定による回折強度が、バリアメタル膜とCu配線金属膜との化合物の回折強度の10倍以下である。

(もっと読む)

電子装置及びその製造方法

【課題】絶縁膜とCuを含む配線との間に介在する下地膜であって、特に酸素のバリア性が高い下地膜を含む電子装置を提供する。

【解決手段】電子装置は、凹部の形成された絶縁膜と、凹部内に形成され、Cuを含む配線層と、絶縁膜と前記配線層との間に形成され、Ta及びMnを含む下地膜とを有する。

(もっと読む)

CVD装置及び半導体装置の製造方法

【課題】ウェハー外周部から剥離した膜がカラーリングに異物として付着することを抑制できるCVD装置及び半導体装置の製造方法を提供する。

【解決手段】高密度プラズマCVD装置は、成膜とエッチングを同時に又は繰り返して行うことで埋め込み性の高い膜をウェハー上に形成する高密度プラズマCVD装置であり、、ウェハー21が保持され、ウェハー21より径の小さい静電チャック2と、静電チャック2の側壁を囲むように設置されたカラーリング1bとを具備し、カラーリング1bは、静電チャック2の側壁に対向し且つウェハーの外周部の下方に位置する対向部40aを有し、対向部40aは静電チャックの側壁を囲むように形成されており、対向部40aにおける静電チャック2に対して外側は、前記ウェハーの外周部の最も外側の端部より内側に位置していることを特徴とする。

(もっと読む)

被処理体の移載機構及び被処理体の処理システム

【課題】少ない台数のイオン発生手段で例えば被処理体移載エリア内の広範囲に亘って帯電箇所の除電及び浮遊する帯電塵の除電を行うことが可能な被処理体の移載機構を提供する。

【解決手段】複数の被処理体Wを複数段に亘って保持して収容することが可能な収容ボックス6と、複数の被処理体を複数段に亘って保持し、被処理体に対して所定の処理を施すための処理容器64内へロード及びアンロードされる被処理体保持手段18との間で、被処理体の移載を行う被処理体の移載機構52において、昇降手段54により上下方向へ昇降可能になされた昇降台56と、昇降台に設けられて、被処理体を載置して前進、後退及び旋回可能になされたフォーク手段58と、フォーク手段に設けられて静電気を除去するイオンを発生させるイオン発生手段60とを備える。

(もっと読む)

181 - 200 / 490

[ Back to top ]