Fターム[4M104AA02]の内容

Fターム[4M104AA02]に分類される特許

201 - 220 / 393

感光性半導体基板上への局部的エレクトログラフティング方法

本発明は、感光性半導体基板の表面における選択領域上に有機膜を形成する方法であって、i)少なくとも1つの有機定着剤を含む溶液を少なくとも1つの選択領域と接触させる段階と、ii)前記基板を、段階i)において使用する前記定着剤の還元電位よりもより負の電位に分極する段階と、iii)そのエネルギーが少なくとも前記半導体のバンドギャップと少なくとも等しい光放射に前記選択領域を曝露させる段階と、を含むことを特徴とする形成方法に関する。 (もっと読む)

半導体装置及びその製造方法

【課題】Ge又はSiGe化合物と金属とをオーミック接触させるための新規な手法、新規な構造の提供。

【解決手段】i)Ge又はSiGe化合物;ii)金属;及びiii) i)の物質とii)金属との間に配置される絶縁体又は半導体;のみからなる部位、を有する半導体装置であって、Ge又はSiGe化合物と金属とがオーミック接触である、上記半導体装置により、上記課題を解決する。具体的には、上記iii)の物質が絶縁体であり、該絶縁体の厚さが2.5nm以下であること;により、上記課題を解決する。

(もっと読む)

ゲルマナイド成長の改良方法およびそれにより得られたデバイス

【課題】半導体デバイス中に金属ゲルマナイド層を形成する過程で、ピット、過成長、または突出物のような欠陥を防止する方法を提供する。

【解決手段】少なくとも1つのゲルマニウム層の領域がその上に露出した基板を提供する工程と、基板とゲルマニウム領域の上に、適当な金属を堆積させる工程と、金属の上に、シリコン酸化物含有層、シリコン窒化物層、チタン窒化物層、タンタル窒化物層、またはタングステン層からなるキャップ層を形成する工程と、次に、金属ゲルマナイドを形成するためにアニールを行う工程と、次に、キャップ層を選択的に除去する工程と、次に、未反応金属を選択的に除去する工程と、を含み、キャップ層の形成に用いられる温度は、アニール温度より低い方法。

(もっと読む)

半導体装置およびその製造方法

【課題】SiO2よりも高い誘電率を有する材料からなる絶縁膜上に設けられた金属電極の仕事関数が所望の値を有する半導体装置を提供することを可能にする。

【解決手段】半導体基板34と、半導体基板上に形成されたトンネル絶縁層36と、トンネル絶縁層上に設けられた浮遊ゲート電極37と、浮遊ゲート電極上に形成され高誘電率材料からなる第1絶縁層38aと、この第1絶縁層上に形成されシリコンおよび酸素ならびに窒素を含むかあるいはシリコンおよび窒素を含む第2絶縁層38bとを有する電極間絶縁膜38と、電極間絶縁膜上に形成された制御ゲート電極40と、第2絶縁層と制御ゲート電極との界面に形成され13族元素を含む界面層44と、制御ゲート電極の両側の半導体基板に形成されたソース・ドレイン領域35と、を含み、界面層の前記13族元素の結合状態数は酸化、窒化、または酸窒化結合状態の総数よりも金属結合状態の数が多い。

(もっと読む)

低コンタクト抵抗を示すMOS構造およびその形成方法

低コンタクト抵抗を示すMOS構造(100,200)と、このようなMOS構造の形成方法が提供される。一方法では、半導体基板(106)が提供され、前記半導体基板上にゲートスタック(146)が形成される。前記半導体基板内に、前記ゲートスタックと整合された不純物ドープ領域(116)が形成される。前記不純物ドープ領域から延びる隣接するコンタクトフィン(186)が形成され、前記コンタクトフィン上に金属シリサイド層(126)が形成される。前記コンタクトフィンの少なくとも1つに存在する前記金属シリサイド層の少なくとも一部に対するコンタクト(122)が形成される。  (もっと読む)

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】PMOSトランジスタのソース・ドレイン領域にSiGe層が形成されており、当該SiGe層の上面がシリサイド化されている構成において、ソース・ドレイン領域と金属シリサイドとの接触抵抗の低減を図ることができる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板1、SiGe層7、高濃度Ge層8および金属シリサイド層9を備えている。SiGe層7は、PMOSトランジスタ100のソース・ドレイン領域となる半導体基板の表面内に形成される。高濃度Ge層8は、SiGe層上面に形成され、SiGe層7内におけるGe濃度よりも高いGe濃度を有する。金属シリサイド層9は、高濃度Ge層8上に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの側壁絶縁膜に関連する新たな提案を行う。

【解決手段】基板と、前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記ゲート電極の側面に形成された第1の側壁絶縁膜と、前記第1の側壁絶縁膜の表面及び前記基板の上面に形成された第2の側壁絶縁膜と、前記第2の側壁絶縁膜の表面に形成された第3の側壁絶縁膜と、前記第2の側壁絶縁膜の一部が除去されて前記第1の側壁絶縁膜と前記第3の側壁絶縁膜との間に形成された溝、に埋め込まれている絶縁膜とを備えることを特徴とする半導体装置。

(もっと読む)

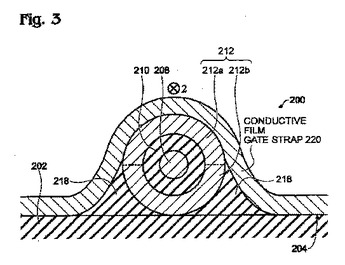

コア−シェル−シェル・ナノワイヤトランジスタ、およびその製造方法

コア−シェル−シェル(CSS)ナノワイヤトランジスタ(NWT)であって、表面を持つ基板と、半導体コアと、該半導体コアを囲む絶縁性シェルと、該絶縁性シェルを囲む導電性シェルとを含む円柱形のCSSナノ構造体であって、上記表面上にある下側半円柱を有するCSSナノ構造体と、上記CSSナノ構造体の中央部にある上記導電性シェルから形成されているゲート電極と、上記基板の表面と、上記CSSナノ構造体の中央部にある上記下側半円柱との間に配置された絶縁性凹形ストリンガと、上記CSSナノ構造体の中央部にある、ゲート電極および上記絶縁性凹形ストリンガの上に形成されている導電膜ゲートストラップと、上記CSSナノ構造体の両端部にある、上記半導体コアの複数の露出領域に形成されているソース/ドレイン(S/D)領域と、を含むコア−シェル−シェル(CSS)ナノワイヤトランジスタ(NWT)。  (もっと読む)

(もっと読む)

半導体発光素子

【課題】 発光効率を向上できると共に、順電圧の上昇を抑制可能な半導体発光素子を提供することを目的とする。

【解決手段】 半導体層と、該層上に設けられた透光性の導電性酸化物膜とを有し、導電性酸化物膜は、部分的に柱状構造部を有する半導体発光素子。

(もっと読む)

ゲート構造体を形成する方法

ゲート構造体を形成するプロセスが記述される。ウェブは、基材、その基材上に配置されている複数個の導電性エレメント並びに導電性陽極酸化バスを含む。このウェブは陽極酸化ステーションを通って動かされ、複数個のゲート電極に隣接する複数個のゲート誘電体を含む複数個のゲート構造体を形成する。半導体、ソース電極及びドレイン電極を供給する電子デバイスを形成するプロセスが更に提供される。  (もっと読む)

(もっと読む)

バイポーラ無電解プロセス方法

【課題】従来技術の欠点を有さない、バイポーラ無電解プロセス方法を提供する。

【解決手段】半導体基板の表面に金属化合物を無電解析出(光Bi−OCDとよばれる)させるバイポーラ光電気化学プロセスであって、基板の表側と基板の裏側の異なった照度が、カソード反応とアノード反応とを分離する駆動力を形成し、高歩留まりの金属化合物の析出が得られるプロセスが開示されている。更に、基板の表面が少なくとも部分的に絶縁性パターンで覆われ、金属化合物の析出がパターンの開口部中で選択的に起きる選択光Bi−OCDプロセスが開示されている。

(もっと読む)

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

半導体装置

【課題】光電変換素子を配線基板等に実装するときに、その固着強度を向上させ、接触不良や剥離等の問題を解決することを課題とする。

【解決手段】第1の基板上に、光電変換層と、光電変換層の出力電流を増幅する、少なくとも2つの薄膜トランジスタからなる増幅回路と、前記光電変換層及び前記増幅回路に電気的に接続され、高電位電源を与える第1の電極及び低電位電源を与える第2の電極と、前記第1の基板の最上層に、導電材料と合金を形成する固着層とを有し、第2の基板上に、第3の電極と第4の電極と、前記第1の電極と前記第3の電極、並びに、前記第2の電極と前記第4の電極を固着する前記導電材料とを有する半導体装置に関する。

(もっと読む)

ゲルマニウム・ナノロッドを具備した電界効果トランジスタ及びその製造方法

【課題】ゲルマニウム・ナノロッドを具備した電界効果トランジスタ及びその製造方法を提供する。

【解決手段】基板上に形成されたゲート酸化物と、ゲート酸化物に埋め込まれ、その両端が露出された少なくとも1つのゲルマニウム・ナノロッドと、ゲルマニウム・ナノロッドの両端とそれぞれ連結されたソース電極及びドレイン電極と、ゲート酸化物上でソース電極及びドレイン電極間に形成されたゲート電極とを具備することを特徴とする電界効果トランジスタである。

(もっと読む)

ナノワイヤトランジスタおよびその製造方法

【課題】ナノワイヤトランジスタ(NWT)の製造において、凹状ストリンガを除去する方法を提供する。

【解決手段】

本方法は、軸の外部表面が基板表面に接している円筒状のナノ構造体を準備する。ナノ構造体は、絶縁性半導体コアを含んでいる。導電性薄膜が、ナノ構造体上に堆積され、ゲートストラップ、またはゲートとゲートストラップとの組み合わせとして機能する。ハードマスク絶縁体が、導電性薄膜上に堆積され、ハードマスクの選択領域が異方性プラズマエッチングされる。結果として、ナノ構造体の円筒状部分を実質的に囲む導電性薄膜ゲート電極が形成される。

(もっと読む)

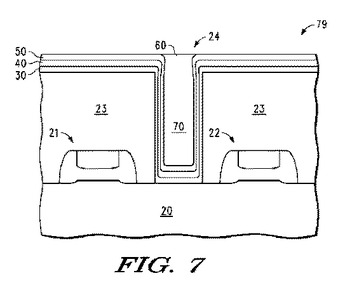

ボイドの無いコンタクトプラグ

コンタクトプラグを形成する半導体素子形成プロセスでは、チタンまたはタンタルコンタクト層(30)、窒化チタンバリア層(40)、及びタングステンシード層をコンタクト開口部(24)に順番に堆積させる。次に、コンタクトホール(24)への充填を、コンタクト開口部の底面から上に向かって、銅層(60)を電気メッキすることにより行なって、ボイドがコンタクト開口部(24)内に形成されることがないようにする。全ての余分な材料をCMPプロセスにより除去してコンタクトプラグ(70)を形成し、この場合、CMPプロセスを使用して、コンタクト層/シード層/バリア層(30,40,50)のうちの一つ以上の層を薄くする、または除去することもできる。  (もっと読む)

(もっと読む)

半導体装置

【課題】信頼性の向上した半導体装置及びその作製方法を提供する。

【解決手段】ゲート電極と重畳し、該重畳領域の外側に不純物領域が形成された半導体層と、半導体層のゲート電極が設けられた側と同じ側の面に設けられ、不純物領域と一部が接する第1導電層と、ゲート電極及び第1導電層の上に設けられた絶縁層と、該絶縁層に形成され、第1導電層と少なくとも一部が重畳する開口を介して第1導電層と接する第2導電層と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造方法の煩雑化を抑制し、ばらつきを抑え、適切なしきい値およびゲート電極の空乏化の抑制を実現可能にする。

【解決手段】p型半導体基板2と、p型半導体基板に離間して形成された第1ソース領域6aおよび第1ドレイン領域6bと、第1ソース領域および第1ドレイン領域との間のp型半導体基板上に形成された第1ゲート絶縁膜11と、第1ゲート絶縁膜上に形成され、母相が多結晶シリコン15aであり、その結晶粒界と第1ゲート絶縁膜との界面の少なくとも第1原子層15cに真空仕事関数がシリコンのミッドギャップより小さい金属状態の第1金属元素を含有する第1ゲート電極15と、を有するnチャネルMISFETと、を備えている。

(もっと読む)

熱CVD装置および成膜方法

【課題】所望の膜厚を高精度に得ることができ、基板の熱的負荷を低減できるカーボンナノチューブの作製に用いて最適な熱CVD装置および成膜方法を提供する。

【解決手段】本発明の熱CVD装置20は、基板Wの加熱源に赤外線ランプ等の加熱ランプ23を用い、反応室22内の基板Wを局所的に加熱操作することで、反応室22に導入された原料ガスが基板に到達する前に成長温度に達することを防止し、基板上における成長速度の緩和を図る。これにより、所望の膜厚の薄膜を高精度に形成することが可能となる。また、加熱源に加熱ランプ23を用いることで、基板が長時間高温に晒されることを防止して基板に加わる熱的負荷を低減することが可能となる。更に、反応室内の基板を冷却する基板冷却機構を備えることで、成膜後において基板の強制冷却が可能となり、これにより基板に加わる熱的負荷の更なる低減を図れるようになる。

(もっと読む)

2つの仕事関数を備えたCMOSデバイスの製造方法

【課題】本発明は、2つの仕事関数の半導体デバイスの製造方法を提供する。

【解決手段】製造方法は、基板の第1領域及び第2領域上にデバイスを設けることを備える。これは、基板の第1領域及び第2領域上に誘電性層を設けること、及び第1及び第2領域の両方の誘電性層の上部にゲート電極を設けることによってなされる。第1領域上のゲート電極及び第2領域上のゲート電極の両方は仕事関数を有する。上記方法は、さらに、誘電性層とゲート電極との間で第1領域上にキャッピング層を設けることで第1領域上のゲート電極の仕事関数を変更し、及び第2領域における誘電性層とゲート電極との間の界面でスピーシーズを導入するようにスピーシーズを埋め込むことにより第2領域上のゲート電極の仕事関数を変更することを備える。

(もっと読む)

201 - 220 / 393

[ Back to top ]