Fターム[4M104AA02]の内容

Fターム[4M104AA02]に分類される特許

141 - 160 / 393

相補型半導体装置とその製造方法

【課題】 マルチゲートMISFETからなる高移動度のnFET及びpFETの双方の移動度を向上させる相補型半導体装置とその製造方法を提供する。

【解決手段】

基板10上にnチャネルMISトランジスタとpチャネルMISトランジスタが形成された相補型半導体装置であって、nチャネルMISトランジスタ及びpチャネルMISトランジスタが、基板10の主面に平行な面内に引っ張り歪みを有する第一の半導体層と圧縮歪みを有する第二の半導体層とが交互に積層され、基板10の主面に対して突出した積層構造と、積層構造の対向する両側面を覆うように形成されたゲート絶縁膜80と、ゲート絶縁膜80を介して前記積層構造を覆って形成されたゲート電極30と、ゲート絶縁膜80とゲート電極30をはさんで対向し、積層構造の両端に形成されたソース/ドレイン領域20と、を有することを特徴とする相補型半導体装置。

(もっと読む)

電界効果型トランジスタ

【課題】ドレイン電極からのホールリークが防止された横型のFETを提供することを課題とする。

【解決手段】基板の表面上に形成された第1導電型のチャネル層と、前記チャネル層上に形成されたソース電極、ドレイン電極及びゲート電極とを備え、前記ソース電極及びドレイン電極を前記チャネル層とオーミックコンタクトさせて電界効果型トランジスタを構成し、前記ドレイン電極の下部の前記チャネル層に第1導電型の拡散領域を備え、前記拡散領域が、式(1)Ns≧ε×Vmax/(q×t)(式中、εは前記チャネル層の誘電率[F/m]、Vmaxは前記電界効果型トランジスタの仕様最大電圧[V]、qは電荷量(1.609×10-19)[C]、tは前記基板の表面から前記拡散領域の底面までの距離[m]である)で表されるシート不純物濃度Ns[cm-2]を有していることを特徴とする電界効果型トランジスタにより上記課題を解決する。

(もっと読む)

デュアル仕事関数半導体デバイスの製造方法および製造されたデバイス

【課題】デュアル仕事関数半導体デバイスの製造方法を提供する。

【解決手段】半導体基板100上に、これと接触するゲート誘電体層104を形成する工程と、ゲート誘電体層の上に、これと接触する金属層105を形成する工程と、金属層の上に、これと接触するゲート充填材料の層106を形成する工程と、ゲート誘電体層、金属層、およびゲート充填層をパターニングして、第1ゲートスタックと第2ゲートスタックとを形成する工程と、半導体基板中に、ソースおよびドレイン領域109を形成する工程と、第1および第2ゲートスタックの少なくとも片側の第1および第2領域中に誘電体層を形成する工程と、その後に第2ゲートスタックのみからゲート充填材料を除去し、下層の金属層を露出させる工程と、露出した金属層を金属酸化物層1051に変える工程と、第2ゲートスタックを他のゲート充填材料115を用いて再形成する工程とを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】インパクトイオン化領域にてキャリアがゲート絶縁膜に入り込むことがない半導体装置とその製造方法を提供する。

【解決手段】トランジスタ部分22と、ダイオード部分23を具備し、トランジスタ部分22は、第1導電型又は真性の半導体領域であるチャネル形成領域6と、チャネル形成領域6に接するゲート絶縁膜7と、チャネルを形成させるゲート電極8と、第2導電型あり、チャネル形成領域6に接し、ドレイン電圧が供給されるドレイン領域4と、第2導電型であり、チャネル形成領域6を介してドレイン領域4に対向し、チャネル形成領域6にチャネルが形成されたときにチャネル形成領域6を介してドレイン電圧が供給されるソース領域5とを含み、ダイオード部分23は、ソース領域5に電気的に接続されており、ソース領域5にドレイン電圧が供給されたときに、ダイオード部分23はインパクトイオン化現象が発生する領域を含む。

(もっと読む)

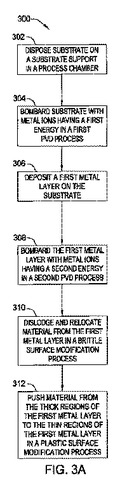

強化された銅のイオン化を伴うPVD銅シードオーバーハング再スパッタ

パターンが形成された基板上に金属を堆積させる方法および装置を提供する。金属層が,第1のエネルギーを有する物理蒸着工程で形成される。第2のエネルギーを用いて金属層上に第2の物理蒸着工程が行われ、ここで、堆積層は、脆性および塑性表面修正工程の相互作用を受け、基板上にほぼ同形の金属層が形成される。  (もっと読む)

(もっと読む)

半導体装置、パターン形成方法および半導体装置の製造方法

【課題】開口部の間口部分の拡大を抑制しつつ、開口部内に埋め込み導体を埋め込みやすくする。

【解決手段】半導体ウェハW1の中心から左側に離れたチップ領域C1a、C1bでは、開口部13a、13b内の左右の壁面のうち右側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心から右側に離れたチップ領域C1d、C1eでは、開口部13d、13e内の左右の壁面のうち左側の壁面にのみ深さ方向に沿って傾斜面を設け、半導体ウェハW1の中心の近傍のチップ領域C1cでは、開口部13c内の左右の壁面には傾斜面を設けないようにする。

(もっと読む)

半導体装置の作製方法

【課題】ガラス基板を使用したSOI基板上に形成しても、ゲート電極を形成する導電膜を成膜する際に該導電膜の加える応力により、ガラス基板上の絶縁膜及び半導体膜がはがれないような半導体装置の作製方法の提供を課題の一つとする。

【解決手段】ボンド基板上に第1の絶縁膜を形成し、ボンド基板の表面からイオンを添加することによって脆化層を形成し、ボンド基板を、第1の絶縁膜を介してガラス基板と貼り合わせ、ボンド基板を脆化層において分離してガラス基板上に第1の絶縁膜を介して半導体膜を形成し、第1の絶縁膜及び半導体膜の周辺領域を除去してガラス基板の一部を露出させ、半導体膜、第1の絶縁膜及びガラス基板上に接してゲート絶縁膜を形成し、ゲート絶縁膜上に接して2層構造の積層導電膜を形成し、2層構造の積層導電膜として、上層に引っ張り応力を有する導電膜、下層に圧縮応力を有する導電膜を用いて半導体装置を作製する。

(もっと読む)

半導体装置の製造方法

【課題】加工精度を改善し、かつ厚い配線を得るための半導体装置の製造方法を提供することを課題とする。

【解決手段】絶縁性基板上に形成された導電性膜上に配線形成領域を覆う第1のフォトレジストパターンを形成する工程と、前記第1のフォトレジストパターンをマスクとする異方性エッチングにより前記導電性膜の上部を除去することで第1溝を形成する工程と、前記第1のフォトレジストパターンを除去した後、前記第1溝の底部の少なくとも一部が露出した開口を有する第2のフォトレジストパターンを形成する工程と、前記第2のフォトレジストパターンをマスクとする異方性エッチングにより前記第1溝の底部に露出する前記導電性膜の下部を少なくとも除去することで第2溝を形成する工程を備えることで、前記第1溝と第2溝に由来する配線分離溝と、前記配線分離溝により分離された配線とを形成することを特徴とする半導体装置の製造方法により上記課題を解決する。

(もっと読む)

電界効果型トランジスタ及びその製造方法並びに画像表示装置

【課題】電界効果型トランジスタにおいて、バンク層をガイドとして半導体溶液を塗布する方法を用いて、精度良く確実にチャネル部に半導体を形成するための電界効果型トランジスタ構造を提供することを目的とする。また、その構造を用いた電界効果型トランジスタの製造方法、及びそれを用いた画像表示装置を提供すること。

【解決手段】ゲート電極と、前記ゲート電極上に形成されたゲート絶縁層と、ソース電極と、下部画素電極と、前記下部画素電極に接続されたドレイン電極と、前記ソース電極及び前記ドレイン電極の間に形成された半導体と、半導体を挟むように形成されたバンク層より構成された電界効果型トランジスタにおいて、前記バンク層がストライプ状に形成されていることを特徴とする電界効果型トランジスタとする。

(もっと読む)

バックグラウンドめっきの抑制

【課題】半導体上のバックグラウンドめっきを抑制する方法を提供する。

【解決手段】方法は、高い光透過性を有する相変換レジストを誘電体上に選択的に堆積させてパターンを形成すること、そのレジストで覆われていない誘電体の部分をエッチング除去すること、並びにその誘電体のエッチングされた部分上に金属シード層を堆積させることを含む。次いで、光誘導めっきによって、その金属シード層上に金属層が堆積させられる。

(もっと読む)

半導体装置およびその製造方法

【課題】製品の歩留まりを向上することが可能な半導体装置を提供する。

【解決手段】半導体装置100は、埋め込み絶縁膜上に第1の方向に延びて形成され、シリコンまたはゲルマニウムの単結晶からなり、ソース・ドレイン拡散層となる部分にn型の不純物を含む第1のフィン層103aと、第1のフィン層の表面に選択的に形成され、n型の不純物を含みソース・ドレイン拡散層を構成する第1のエピタキシャル成長層112a,112bと、同様に、シリコンまたはゲルマニウムの単結晶からなり、ソース・ドレイン拡散層となる部分にp型の不純物を含む第2のフィン層103bと、第2のフィン層の表面に選択的に形成され、p型の不純物を含みソース・ドレイン拡散層を構成する第2のエピタキシャル成長層112c,112dと、第1のエピタキシャル成長層と第2のエピタキシャル成長層との間に形成された第1の分離絶縁膜107a,107bと、を備える。

(もっと読む)

金属シリサイド形成のための方法および装置

本明細書で述べられる実施形態は、無拡散アニールプロセスを使用して金属シリサイド層を形成する方法を包含する。一実施形態では、基板上に金属シリサイド材料を形成するための方法が、提供される。その方法は、基板のシリコン含有表面を覆って金属材料を堆積させるステップと、金属材料を覆って金属窒化物材料を堆積させるステップと、金属窒化物材料を覆って金属接点材料を堆積させるステップと、基板を無拡散アニールプロセスにさらして金属シリサイド材料を形成するステップとを含む。無拡散アニールプロセスの短い時間枠は、窒素がシリコン含有界面に拡散して窒化シリコンを形成する時間を低減し、それ故に界面抵抗を最小限にする。  (もっと読む)

(もっと読む)

半導体トランジスタ素子の製造方法、及び半導体トランジスタ素子

【課題】集積密度の向上が容易に図れる半導体トランジスタ素子の製造方法及び半導体トランジスタ素子を提供する。

【解決手段】半導体トランジスタ素子10においては、製造時において、ソース電極18及びドレイン電極20を、半導体インク滴を保持しうる凹部Pを有する構成とし、この凹部Pを有するソース電極18及びドレイン電極20の間に、半導体インク滴22Aを滴下することで半導体層22を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】金属微粒子と半導体基板の反応を利用して電極を形成する、高性能な半導体装置の製造方法およびグレイン粒径の小さい電極を有する高性能な半導体装置を提供する。

【解決手段】直径20nm以下の金属微粒子を溶媒中に分散した溶液を、半導体基板上に塗布する工程と、溶媒を蒸発させる工程と、金属微粒子と半導体基板を反応させ、半導体基板表面に金属半導体化合物薄膜を形成する工程とを有することを特徴とする半導体装置の製造方法。半導体基板上に金属半導体化合物薄膜を有する半導体装置であって、金属半導体化合物薄膜は膜厚方向に単グレインで形成され、単グレインの粒径が40nm以下であることを特徴とする半導体装置。

(もっと読む)

アルミニウムがドープされた金属炭窒化物ゲート電極の作製方法

半導体デバイス用のアルミニウムがドープされた金属(タンタル又はチタン)炭窒化物ゲート電極の作製方法が記載されている。当該方法は、上に誘電層を有する基板を供する工程、及びプラズマが存在しない状態で前記誘電層上に前記ゲート電極を作製する工程を有する。前記ゲート電極は、金属炭窒化物を堆積する堆積工程、及び前記金属炭窒化物上にアルミニウム前駆体の原子層を吸着させる吸着工程によって作製される。前記堆積工程及び前記吸着工程は、前記アルミニウムがドープされた金属炭窒化物ゲート電極が所望の厚さを有するまで、必要な回数だけ繰り返されて良い。  (もっと読む)

(もっと読む)

半導体素子およびその製造方法

【課題】本発明はトレンチの上部縁部位でゲート絶縁膜が薄くなる現象を防止し、均一な厚さを有するゲート絶縁膜を形成することができる半導体素子、およびその製造方法を提供する。

【解決手段】本発明の半導体素子は、活性領域を画定するトレンチが形成された基板と、該トレンチに埋め込まれた素子分離膜と、前記活性領域上にゲート絶縁膜の成長時に前記トレンチの上部縁部位での酸化を促進するために前記トレンチの上部縁部位に形成された酸化促進領域と、ゲート絶縁膜上に形成されたゲート導電膜と、を備える。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ソース・ドレインの寄生抵抗の低減及び短チャネル効果の抑制と共にリーク電流の低減をはかる。

【解決手段】チャネル領域を構成する第1の半導体領域12と、第1の半導体領域12上にゲート絶縁膜15を介して形成されたゲート電極16と、第1の半導体領域12をチャネル長方向から挟んで形成された金属シリサイドからなるソース・ドレイン電極14と、を具備してなる電界効果トランジスタであって、ソース・ドレイン電極14は、チャネル領域の平均的な不純物濃度よりも高い不純物濃度を有し、且つチャネル領域との界面又は界面近傍に前記不純物濃度のピークを持ち、チャネル領域は、ソース・ドレイン電極との界面又は界面近傍に前記不純物濃度のピークを持つ。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜に高誘電率膜を用いたMISトランジスタのトランジスタ特性を向上する。

【解決手段】基板の主面上に形成した酸化シリコン(SiO2)膜上に、ハフニウムおよび酸素を含むベース絶縁膜を形成する。次いで、ベース絶縁膜上に、ベース絶縁膜より薄く、かつ、金属元素のみからなる金属薄膜を形成し、その金属薄膜上に、耐湿性および耐酸化性を有する保護膜を形成する。その後、保護膜を有する状態で、ベース絶縁膜に金属薄膜の金属元素をすべて拡散することによって、酸化シリコン膜上に、酸化シリコン膜より厚く、かつ、酸化シリコンより誘電率が高く、ベース絶縁膜のハフニウムおよび酸素と、金属薄膜の金属元素とを含む混合膜(高誘電率膜)を形成する。

(もっと読む)

半導体装置

【課題】寄生抵抗が大きい場合においても、フィン構造を有する電界効果トランジスタのゲインを向上させる。

【解決手段】複数のフィンf11〜f19、f21〜f29が互いに並行に配置し、フィンf13〜f18、f23〜f28にそれぞれ跨るようにしてゲート電極G11、G12をフィンf13〜f18、f23〜f28の両側面にそれぞれ形成し、フィンf13〜f18、f23〜f28にそれぞれ跨るようにしてゲート電極G11、G12に並列されたゲート電極G13、G14をフィンf13〜f18、f23〜f28の両側面にそれぞれ形成し、フィンf13〜f18、f23〜f28に跨るようにしてゲート電極G13、G14に並列されたゲート電極G15をフィンf13〜f18、f23〜f28の両側面に形成する。

(もっと読む)

デュアル仕事関数の金属ゲートを統合する際のイオン注入を用いた有効仕事関数の変化

【課題】 デュアル仕事関数の金属ゲートを統合する際にイオン注入を用いて有効仕事関数を変化させる方法を提供する。

【解決手段】 デュアル有効仕事関数をもつ金属ゲートを集積化するために有効仕事関数を変化させるためのイオン注入が提示される。1つの方法は、第1の型の電界効果トランジスタ(FET)領域及び第2の型のFET領域の上に、高誘電率(高k)層を形成することと、第1の型のFET領域及び第2の型のFET領域の上に、第1の型のFETに適合する第1の有効仕事関数をもつ金属層を形成することと、第2の型のFET領域の上の金属層内に種を注入することによって、第2の型のFET領域の上の第1の有効仕事関数を第2の異なる有効仕事関数に変化させることとを含むことができる。

(もっと読む)

141 - 160 / 393

[ Back to top ]